Professional Documents

Culture Documents

Lab1

Lab1

Uploaded by

Usman KianiCopyright:

Available Formats

You might also like

- Pioneer PL 500X Service ManualDocument22 pagesPioneer PL 500X Service ManualAngel Luciano Ramon Gomez100% (1)

- 6866CJ-C11 Eliminator Battery Charger 011-1519-6Document1 page6866CJ-C11 Eliminator Battery Charger 011-1519-6imacl183% (6)

- VERILOG HDL - Tutorial, PPT FormatDocument30 pagesVERILOG HDL - Tutorial, PPT FormatArslan Kiani100% (2)

- Simulation Lab FileDocument42 pagesSimulation Lab FileSougata GhoshNo ratings yet

- Coal Lab 2Document9 pagesCoal Lab 2AbdurRehmanNo ratings yet

- Assignment 5 E23CSEU0698Document8 pagesAssignment 5 E23CSEU0698sanskarsinghsengarNo ratings yet

- VHDL Unit - 1Document10 pagesVHDL Unit - 1hemanthperreddy123No ratings yet

- Assignment 5 E23CSEU0525Document8 pagesAssignment 5 E23CSEU0525sanskarsinghsengarNo ratings yet

- VLSI Lab Manual 18ECL67 2024Document80 pagesVLSI Lab Manual 18ECL67 2024SwamyNo ratings yet

- Vlsi Lab 18ecl67.DocxDocument81 pagesVlsi Lab 18ecl67.DocxAshok KariholeNo ratings yet

- EXP-2-Design of Binary AddersDocument20 pagesEXP-2-Design of Binary AddersJordan GomezNo ratings yet

- VerilogDocument17 pagesVerilogBack UpNo ratings yet

- Lecture SlideDocument18 pagesLecture SlideBilal MumtazNo ratings yet

- HDL Lab ManualDocument29 pagesHDL Lab ManualRaveen GulipuraNo ratings yet

- Design and Simulate Full Adder Using Half Adder in The Xilinx ISE ToolDocument4 pagesDesign and Simulate Full Adder Using Half Adder in The Xilinx ISE ToolAugustinNo ratings yet

- VLSI Lab Report 8Document24 pagesVLSI Lab Report 8Umar AyubNo ratings yet

- VerificationDocument11 pagesVerificationNaved Sadat YaminNo ratings yet

- Danang University of Science and Technology: Instructor: Nguyen Tri Bang Class: 15ECE2 Group Members: Vo Hoang ChuongDocument12 pagesDanang University of Science and Technology: Instructor: Nguyen Tri Bang Class: 15ECE2 Group Members: Vo Hoang ChuongBin BinNo ratings yet

- EE-307 Fpga Based System Design: Lecture # 05Document15 pagesEE-307 Fpga Based System Design: Lecture # 05Muhammad AnasNo ratings yet

- Dante Experiment#2Document8 pagesDante Experiment#2CHRISTIANJOIE DANTENo ratings yet

- LAB3 Full+AdderDocument3 pagesLAB3 Full+AdderDennis IvanNo ratings yet

- Vlsi Part A ManualDocument47 pagesVlsi Part A ManualLohit PNo ratings yet

- EEE 306 Post LAB 5Document11 pagesEEE 306 Post LAB 5Abu Saleh Bin AftabNo ratings yet

- EXOR Gate Using Concurrent Statements: RTL ViewDocument59 pagesEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNo ratings yet

- CPET7L Hands-OnExerciseNo2Document4 pagesCPET7L Hands-OnExerciseNo2Sebastian Austin SuelaNo ratings yet

- Lab Programs: Computer Organization and ArchitectureDocument57 pagesLab Programs: Computer Organization and ArchitectureTharun S vNo ratings yet

- Digital Circuit Design Lab: Part-BDocument35 pagesDigital Circuit Design Lab: Part-BPrathap VuyyuruNo ratings yet

- Exp6 122 DSDDocument1 pageExp6 122 DSDsejalrayakwar147No ratings yet

- Experiment 2 To 4 - UCS 704 - ESDDocument15 pagesExperiment 2 To 4 - UCS 704 - ESDAryan SharmaNo ratings yet

- Verilog Tutorial1Document37 pagesVerilog Tutorial1vamsikrishna gollapudiNo ratings yet

- Introduction To Verilog: Sistla Srikanth 15104416, EEDocument27 pagesIntroduction To Verilog: Sistla Srikanth 15104416, EESunil JadhavNo ratings yet

- Saksham Porwal DSD Experiment-2Document5 pagesSaksham Porwal DSD Experiment-2chinusood08No ratings yet

- EE271 Lab1 Group06Document9 pagesEE271 Lab1 Group06Lê Vương TháiNo ratings yet

- Chapter 5 Behavioral Model Part1Document24 pagesChapter 5 Behavioral Model Part1Vinh ĐứcNo ratings yet

- Test Benches in VerilogDocument16 pagesTest Benches in VerilogSharan ChaitanyaNo ratings yet

- Combinational Designs: VerilogDocument67 pagesCombinational Designs: Verilogdivakaran sundarNo ratings yet

- Digital 1 W6 NotedDocument19 pagesDigital 1 W6 NotedmartinhhhNo ratings yet

- DSDV Lab Manual PDFDocument15 pagesDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- Lab1 Directed VerificationDocument17 pagesLab1 Directed Verificationfake godNo ratings yet

- 2 49 PDFDocument48 pages2 49 PDFALEX100% (1)

- EE-307 Fpga Based System Design: Lecture # 06Document13 pagesEE-307 Fpga Based System Design: Lecture # 06Talha KhalidNo ratings yet

- VLSI Lab RecordDocument85 pagesVLSI Lab Recordsatyendumohapatra573No ratings yet

- System Verilog For Verification: Dr.R.JayagowriDocument158 pagesSystem Verilog For Verification: Dr.R.JayagowriAdithya ReddyNo ratings yet

- Verilog HDL - IntroductionDocument59 pagesVerilog HDL - IntroductionBhargavi AndraNo ratings yet

- Verilog Sample PPRDocument11 pagesVerilog Sample PPRjayaprasadkalluriNo ratings yet

- CPE 316 - Laboratory 1-2 MACAPAGALDocument17 pagesCPE 316 - Laboratory 1-2 MACAPAGALGERLAND ANDREI CUEVASNo ratings yet

- Combinational Logic CircuitDocument74 pagesCombinational Logic Circuit2023236033No ratings yet

- Combinational Designs4 - 2Document7 pagesCombinational Designs4 - 2divakaran sundarNo ratings yet

- 2022 2 CED Week03 RCA v1Document30 pages2022 2 CED Week03 RCA v1조성민No ratings yet

- COMSATS Institute of Information Technology: Lab#12: Convolutional EncodersDocument3 pagesCOMSATS Institute of Information Technology: Lab#12: Convolutional EncoderstalhaNo ratings yet

- LAB 1Document16 pagesLAB 1vamsi262005No ratings yet

- Tutorial 1Document29 pagesTutorial 1A'ziz MoNo ratings yet

- Vlsi RecordDocument54 pagesVlsi Record21311a04j5No ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Verilog LabDocument16 pagesVerilog LabBhaskar Lal DasNo ratings yet

- Homework 4Document5 pagesHomework 4Naveed AhmedNo ratings yet

- Lab ProgramsDocument14 pagesLab ProgramsspgmaniarunagiriNo ratings yet

- Vlsi LabDocument10 pagesVlsi LabNicholas BourbakiNo ratings yet

- Lecture 2 Verilog PDFDocument35 pagesLecture 2 Verilog PDFkayleNo ratings yet

- Suhas N (Lab Assign 1,2,3)Document37 pagesSuhas N (Lab Assign 1,2,3)Suhas PoliNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- DVP NS305 - NS310 NS315Document110 pagesDVP NS305 - NS310 NS315jazztecnoNo ratings yet

- Program Manual Aria SohoDocument271 pagesProgram Manual Aria Sohoelwielwi91% (11)

- HTTP Www-307.Ibm - Com PC Support Site - Wss DocumentDocument2 pagesHTTP Www-307.Ibm - Com PC Support Site - Wss Documenttintoreto106No ratings yet

- Boje Zica VolvoDocument2 pagesBoje Zica VolvoSmolovic SrdjanNo ratings yet

- Schematic - SPY Camera TransmeterDocument1 pageSchematic - SPY Camera TransmeterSami AslamNo ratings yet

- 1SAM201901R1001 Hkf1 11 Auxiliary ContactDocument4 pages1SAM201901R1001 Hkf1 11 Auxiliary ContactAlladin BegovićNo ratings yet

- Panasonic CapaciatorsDocument89 pagesPanasonic CapaciatorsKokosikNo ratings yet

- Zaman I 2010Document8 pagesZaman I 2010Đăng Nguyễn HảiNo ratings yet

- Data Sheet: Multimeter 560CVD03Document5 pagesData Sheet: Multimeter 560CVD03feromagnetizamNo ratings yet

- ESB - Catalogo Passive Das 10 3Document105 pagesESB - Catalogo Passive Das 10 3Witto PereNo ratings yet

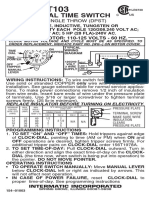

- T103 InstructionsDocument1 pageT103 Instructionsjtcool74No ratings yet

- Ques AnswerDocument8 pagesQues AnswerRafeek makramNo ratings yet

- Composite Cores in Current TransformersDocument5 pagesComposite Cores in Current TransformersMahdiNo ratings yet

- Lab 3Document8 pagesLab 3E24106610許翰翔No ratings yet

- Densitron Corporation: Handling PrecautionsDocument8 pagesDensitron Corporation: Handling PrecautionsMauricio Garcia VentNo ratings yet

- Robot Wifi CamDocument14 pagesRobot Wifi CamjoseplinNo ratings yet

- Major SS Ring Main SS Load DistributionDocument99 pagesMajor SS Ring Main SS Load DistributionAmir IbrahimNo ratings yet

- LK-023-IDN (Temperature, Mass, Volume, Pressure, Length, & Time)Document9 pagesLK-023-IDN (Temperature, Mass, Volume, Pressure, Length, & Time)Aries SupiyantoNo ratings yet

- Coffee Lake H/S Platform System Memory Interface: Technical White PaperDocument51 pagesCoffee Lake H/S Platform System Memory Interface: Technical White PaperagxinNo ratings yet

- PZ SeriesDocument28 pagesPZ SeriesSomiar TradingNo ratings yet

- Automobile Brake Failure IndicatorDocument5 pagesAutomobile Brake Failure IndicatorBhavana GummaNo ratings yet

- BSI Standards Publication: Arc Welding EquipmentDocument30 pagesBSI Standards Publication: Arc Welding EquipmentAlex Alex100% (1)

- 150Mbps PDIC Receiver - SevastopolDocument28 pages150Mbps PDIC Receiver - SevastopoldcalexNo ratings yet

- BEE Experiment 2Document3 pagesBEE Experiment 2MD ZunedNo ratings yet

- Solar Net Metering AgreementDocument7 pagesSolar Net Metering AgreementLogesh KumarNo ratings yet

- 21.alcohol Sensing Display With Alarm ProjectDocument15 pages21.alcohol Sensing Display With Alarm ProjectTrishika DebnathNo ratings yet

- SP315-51Pegatron ST5DB Rev1.0Document82 pagesSP315-51Pegatron ST5DB Rev1.0JOSE PAZNo ratings yet

- Linear Integrated Circuits - EC2254Document77 pagesLinear Integrated Circuits - EC2254Muthu LakiNo ratings yet

Lab1

Lab1

Uploaded by

Usman KianiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lab1

Lab1

Uploaded by

Usman KianiCopyright:

Available Formats

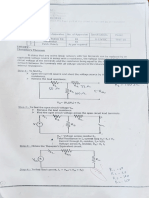

LAB-1(Individual)

Implementation of Half Adder

and Full Adder at three

abstraction level Coding

Engineer. Ali Sabir

Prof. Rashad M. Ramzan

Dr. Hassan Saif

Electrical Engineering Department

National University of Computer &

Emerging Sciences (FAST-NU)

Islamabad-44000, Pakistan

11/10/2021 VLSI Lab 1

1.1 AIM

The purpose of this lab is to introduce you to the basic programming tools. For the purposes of this lab you

will implement an half adder and full adder circuit using VLSI design flow.

1.2 OBJECTIVE

• Verify that the Xilinx tools are up and running

• Introduce you to the Xilinx ISE software.

• Become familiar with Verilog coding and use of the ISE simulator.

• Be able to synthesize and implement Verilog designs using ISE..

1.3 THEORY

1.3.1 INTRODUCTION.

This is a step-by-step tutorial for building a 1-bit full adder in Xilinx ISE 8.2, a Design Suite software that

provides designers with the ability to code designs in a hardware description language such as VHDL or

Verilog. The ISE Design Suite also provides the ability to apply FPGA pin and timing constraints, analyze

for errors and violations, and synthesize to generate configuration bit file formats for FPGAs.

By the end of this tutorial, a student should be able to:

• Create a new design by VHDL coding.

• Verify the function of a design by behavioral simulation.

• Map a design on device through placement and routing procedures.

• Estimate the performance of the design by timing analysis

1.3.2 HALF ADDER

An adder is a digital logic circuit in electronics that implements addition of numbers. In many computers

and other types of processors, adders are used to calculate addresses, similar operations and table indices

in the ALU and also in other parts of the processors. These can be built for many numerical representations

like excess-3 or binary coded decimal. Adders are classified into two types: half adder and full adder. The

half adder circuit has two inputs: A and B, which add two input digits and generate a carry and sum.

By using half adder, you can design simple addition with the help of logic gates.Let’s see an addition of

single bits.

11/10/2021 VLSI Lab 1

HALF ADDER TRUTH TABLE

INPUT OUTPUT

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Table 1.1 Half Adder truth table

Now it has been cleared that 1-bit adder can be easily implemented with the help of the XOR Gate for the

output ‘SUM’ and an AND Gate for the ‘Carry’. When we need to add, two 8-bit bytes together, we can be

done with the help of a full-adder logic. The half-adder is useful when you want to add one binary digit

quantities. A way to develop a two-binary digit adders would be to make a truth table and reduce it. When

you want to make a three binary digit adder, do it again. When you decide to make a four digit adder, do it

again. The circuits would be fast, but development time is slow.

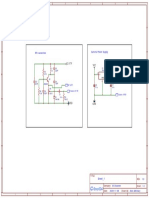

CIRCUIT DIAGRAM

Fig 1.1 Half Adder Logic Circuit

1.4 Verilog Code for Half Adder

1.4.1 Data Flow Modeling

module halfadder (a,b,sum,carry)

input a;

input b;

output sum;

output carry;

assign sum=a ^ b ;

assign carry=a & b; endmodule

11/10/2021 VLSI Lab 1

1.4.2 Test Bench

module halfadder_tb();

// Inputs

reg a;

reg b;

//outputs

wire sum;

wire carry;

// Instantiate the Unit Under Test (UUT)

halfadder uut(.a(a), .b(b), .sum(sum), .carry(carry));

initial begin

a=0;

b=0;

#100

a=0;

b=1;

#100

a=0;

b=1;

#100

a=1;

b=0;

#100

a=1;

b=1;

end

endmodule

1.4.3 Structural Modeling

module halfadder (a, b, s, c);

input a, b;

output s, c;

xor (s, b, a);

and (c, b, a);

endmodule

1.4.2 Behavioural Modeling

module halfadder3(a, sum, carry);

input [1:0] a;

output reg sum,carry;

always@(a)

begin

case(a)

2'b00:

begin

sum <= 0;

carry <= 0;

11/10/2021 VLSI Lab 1

end

2'b11:

begin

sum <= 0;

carry <= 1;

end

default:

begin

sum <= 1;

carry <= 0;

end

endcase

end

endmodule

1.4.3 Test Bench

module halfadder_tb();

// Inputs

reg [1:0] a;

//outputs

wire sum;

wire carry;

// Instantiate the Unit Under Test (UUT)

halfadder uut(.a(a), .b(b), .sum(sum), .carry(carry));

initial begin

a=0;

#100

a=1;

#100

a=2;

#100

a=3;

end

endmodule

1.5 Full Adder

This adder is different to implement than a half adder. The difference between a half adder and full adder

is that the full adder has three inputs and two outputs wheres half adder has only two inputs and two output.

The first two inputs are A and B the third input is an input carry as C-IN, when a full adder logic is designed

you string eight of them togather to create a byte-wider adder and cascade the carry bit from one adder to

the next.

11/10/2021 VLSI Lab 1

1.5.1 Truth Table

INPUT OUTPUT

A B Cin Cout S

0 0 0 0 0

0 0 1 0 1

0 1 0 0 1

0 1 1 1 0

1 0 0 0 1

1 0 1 1 0

1 1 0 1 0

1 1 1 1 1

Table 1.2 Half Adder truth table

1.5.2 Circuit Diagram

Fig 1.1 Full Adder Logic Circuit

1.6 Verilog Code for Half Adder

1.6.1 Data Flow Modeling

module fulladder(a_in, b_in, c_in, sum, carry);

input a_in, b_in,c_in;

output sum, carry;

assign sum = a_in^b_in^c_in;

assign carry = (a_in & b_in)|(b_in & c_in)|(a_in & c_in);

endmodule

11/10/2021 VLSI Lab 1

1.6.2 Test Bench

module FA();

reg a_in;

reg b_in;

reg c_in;

// Outputs

wire sum;

wire carry;

// Instantiation

fulladder uut(.a_in(a_in), .b_in(b_in), .c_in(c_in), .sum(sum),

.carry(carry)

);

initial begin

a_in=0;

b_in=0;

c_in=0;

#100

a_in=0;

b_in=0;

c_in=1;

#100

a_in=0;

b_in=1;

c_in=0;

#100

a_in=0;

b_in=1;

c_in=1;

#100

a_in=1;

b_in=0;

c_in=0;

#100

#100

a_in=1;

b_in=0;

c_in=1;

#100

a_in=1;

b_in=1;

c_in=0;

#100

a_in=1;

b_in=1;

c_in=1;

end

endmodule

11/10/2021 VLSI Lab 1

1.6.3 Behavioural Modeling

module fulladder(abc, sum, carry);

input [2:0] abc;

output sum,carry;

reg sum,carry;

always@(abc)

begin

{c_out, sum} = abc[0] + abc[1] + abc[2];

end

endmodule

1.6.3 Test Bench

module FA();

reg [2:0] abc;

// Outputs

wire sum;

wire carry;

// Instantiation

fulladder uut(.abc(abc), .sum(sum), .carry(carry)

);

initial begin

abc=0;

#100

abc=1;

#100

abc=2;

#100

abc=3;

#100

abc=4;

#100

abc=5;

#100

11/10/2021 VLSI Lab 1

abc=6;

#100

abc=7;

end

endmodule

1.7 IN LAB-TASK

Implement 4-bit full adder at gate level also create their test bench.

1.8 POST LAB TASK

Implement the encoder at data flow and behavioural level modeling.

ENCODER:

A 2^n-to-n encoder has n number of outputs in correspondence to the 2^n number of inputs. It thus

reduces the number of transmission lines and can be compared to a multiplexer. Only one of the

inputs become "high" (logic state "1") at a time.

Example:

• 8:3 encoder ( you are required to implement 8:3 encoder)

11/10/2021 VLSI Lab 1

1.8.1 Data Flow Modeling

1.8.2 Test Bench

11/10/2021 VLSI Lab 1

1.8.3 Behavioural Modeling

1.8.4 Test Bench

11/10/2021 VLSI Lab 1

You might also like

- Pioneer PL 500X Service ManualDocument22 pagesPioneer PL 500X Service ManualAngel Luciano Ramon Gomez100% (1)

- 6866CJ-C11 Eliminator Battery Charger 011-1519-6Document1 page6866CJ-C11 Eliminator Battery Charger 011-1519-6imacl183% (6)

- VERILOG HDL - Tutorial, PPT FormatDocument30 pagesVERILOG HDL - Tutorial, PPT FormatArslan Kiani100% (2)

- Simulation Lab FileDocument42 pagesSimulation Lab FileSougata GhoshNo ratings yet

- Coal Lab 2Document9 pagesCoal Lab 2AbdurRehmanNo ratings yet

- Assignment 5 E23CSEU0698Document8 pagesAssignment 5 E23CSEU0698sanskarsinghsengarNo ratings yet

- VHDL Unit - 1Document10 pagesVHDL Unit - 1hemanthperreddy123No ratings yet

- Assignment 5 E23CSEU0525Document8 pagesAssignment 5 E23CSEU0525sanskarsinghsengarNo ratings yet

- VLSI Lab Manual 18ECL67 2024Document80 pagesVLSI Lab Manual 18ECL67 2024SwamyNo ratings yet

- Vlsi Lab 18ecl67.DocxDocument81 pagesVlsi Lab 18ecl67.DocxAshok KariholeNo ratings yet

- EXP-2-Design of Binary AddersDocument20 pagesEXP-2-Design of Binary AddersJordan GomezNo ratings yet

- VerilogDocument17 pagesVerilogBack UpNo ratings yet

- Lecture SlideDocument18 pagesLecture SlideBilal MumtazNo ratings yet

- HDL Lab ManualDocument29 pagesHDL Lab ManualRaveen GulipuraNo ratings yet

- Design and Simulate Full Adder Using Half Adder in The Xilinx ISE ToolDocument4 pagesDesign and Simulate Full Adder Using Half Adder in The Xilinx ISE ToolAugustinNo ratings yet

- VLSI Lab Report 8Document24 pagesVLSI Lab Report 8Umar AyubNo ratings yet

- VerificationDocument11 pagesVerificationNaved Sadat YaminNo ratings yet

- Danang University of Science and Technology: Instructor: Nguyen Tri Bang Class: 15ECE2 Group Members: Vo Hoang ChuongDocument12 pagesDanang University of Science and Technology: Instructor: Nguyen Tri Bang Class: 15ECE2 Group Members: Vo Hoang ChuongBin BinNo ratings yet

- EE-307 Fpga Based System Design: Lecture # 05Document15 pagesEE-307 Fpga Based System Design: Lecture # 05Muhammad AnasNo ratings yet

- Dante Experiment#2Document8 pagesDante Experiment#2CHRISTIANJOIE DANTENo ratings yet

- LAB3 Full+AdderDocument3 pagesLAB3 Full+AdderDennis IvanNo ratings yet

- Vlsi Part A ManualDocument47 pagesVlsi Part A ManualLohit PNo ratings yet

- EEE 306 Post LAB 5Document11 pagesEEE 306 Post LAB 5Abu Saleh Bin AftabNo ratings yet

- EXOR Gate Using Concurrent Statements: RTL ViewDocument59 pagesEXOR Gate Using Concurrent Statements: RTL ViewSurbhit SinhaNo ratings yet

- CPET7L Hands-OnExerciseNo2Document4 pagesCPET7L Hands-OnExerciseNo2Sebastian Austin SuelaNo ratings yet

- Lab Programs: Computer Organization and ArchitectureDocument57 pagesLab Programs: Computer Organization and ArchitectureTharun S vNo ratings yet

- Digital Circuit Design Lab: Part-BDocument35 pagesDigital Circuit Design Lab: Part-BPrathap VuyyuruNo ratings yet

- Exp6 122 DSDDocument1 pageExp6 122 DSDsejalrayakwar147No ratings yet

- Experiment 2 To 4 - UCS 704 - ESDDocument15 pagesExperiment 2 To 4 - UCS 704 - ESDAryan SharmaNo ratings yet

- Verilog Tutorial1Document37 pagesVerilog Tutorial1vamsikrishna gollapudiNo ratings yet

- Introduction To Verilog: Sistla Srikanth 15104416, EEDocument27 pagesIntroduction To Verilog: Sistla Srikanth 15104416, EESunil JadhavNo ratings yet

- Saksham Porwal DSD Experiment-2Document5 pagesSaksham Porwal DSD Experiment-2chinusood08No ratings yet

- EE271 Lab1 Group06Document9 pagesEE271 Lab1 Group06Lê Vương TháiNo ratings yet

- Chapter 5 Behavioral Model Part1Document24 pagesChapter 5 Behavioral Model Part1Vinh ĐứcNo ratings yet

- Test Benches in VerilogDocument16 pagesTest Benches in VerilogSharan ChaitanyaNo ratings yet

- Combinational Designs: VerilogDocument67 pagesCombinational Designs: Verilogdivakaran sundarNo ratings yet

- Digital 1 W6 NotedDocument19 pagesDigital 1 W6 NotedmartinhhhNo ratings yet

- DSDV Lab Manual PDFDocument15 pagesDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- Lab1 Directed VerificationDocument17 pagesLab1 Directed Verificationfake godNo ratings yet

- 2 49 PDFDocument48 pages2 49 PDFALEX100% (1)

- EE-307 Fpga Based System Design: Lecture # 06Document13 pagesEE-307 Fpga Based System Design: Lecture # 06Talha KhalidNo ratings yet

- VLSI Lab RecordDocument85 pagesVLSI Lab Recordsatyendumohapatra573No ratings yet

- System Verilog For Verification: Dr.R.JayagowriDocument158 pagesSystem Verilog For Verification: Dr.R.JayagowriAdithya ReddyNo ratings yet

- Verilog HDL - IntroductionDocument59 pagesVerilog HDL - IntroductionBhargavi AndraNo ratings yet

- Verilog Sample PPRDocument11 pagesVerilog Sample PPRjayaprasadkalluriNo ratings yet

- CPE 316 - Laboratory 1-2 MACAPAGALDocument17 pagesCPE 316 - Laboratory 1-2 MACAPAGALGERLAND ANDREI CUEVASNo ratings yet

- Combinational Logic CircuitDocument74 pagesCombinational Logic Circuit2023236033No ratings yet

- Combinational Designs4 - 2Document7 pagesCombinational Designs4 - 2divakaran sundarNo ratings yet

- 2022 2 CED Week03 RCA v1Document30 pages2022 2 CED Week03 RCA v1조성민No ratings yet

- COMSATS Institute of Information Technology: Lab#12: Convolutional EncodersDocument3 pagesCOMSATS Institute of Information Technology: Lab#12: Convolutional EncoderstalhaNo ratings yet

- LAB 1Document16 pagesLAB 1vamsi262005No ratings yet

- Tutorial 1Document29 pagesTutorial 1A'ziz MoNo ratings yet

- Vlsi RecordDocument54 pagesVlsi Record21311a04j5No ratings yet

- Combinational Logic Circuits: Prof. David Márquez ViloriaDocument16 pagesCombinational Logic Circuits: Prof. David Márquez ViloriaJose Mateo Aristizabal DiazNo ratings yet

- Verilog LabDocument16 pagesVerilog LabBhaskar Lal DasNo ratings yet

- Homework 4Document5 pagesHomework 4Naveed AhmedNo ratings yet

- Lab ProgramsDocument14 pagesLab ProgramsspgmaniarunagiriNo ratings yet

- Vlsi LabDocument10 pagesVlsi LabNicholas BourbakiNo ratings yet

- Lecture 2 Verilog PDFDocument35 pagesLecture 2 Verilog PDFkayleNo ratings yet

- Suhas N (Lab Assign 1,2,3)Document37 pagesSuhas N (Lab Assign 1,2,3)Suhas PoliNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- DVP NS305 - NS310 NS315Document110 pagesDVP NS305 - NS310 NS315jazztecnoNo ratings yet

- Program Manual Aria SohoDocument271 pagesProgram Manual Aria Sohoelwielwi91% (11)

- HTTP Www-307.Ibm - Com PC Support Site - Wss DocumentDocument2 pagesHTTP Www-307.Ibm - Com PC Support Site - Wss Documenttintoreto106No ratings yet

- Boje Zica VolvoDocument2 pagesBoje Zica VolvoSmolovic SrdjanNo ratings yet

- Schematic - SPY Camera TransmeterDocument1 pageSchematic - SPY Camera TransmeterSami AslamNo ratings yet

- 1SAM201901R1001 Hkf1 11 Auxiliary ContactDocument4 pages1SAM201901R1001 Hkf1 11 Auxiliary ContactAlladin BegovićNo ratings yet

- Panasonic CapaciatorsDocument89 pagesPanasonic CapaciatorsKokosikNo ratings yet

- Zaman I 2010Document8 pagesZaman I 2010Đăng Nguyễn HảiNo ratings yet

- Data Sheet: Multimeter 560CVD03Document5 pagesData Sheet: Multimeter 560CVD03feromagnetizamNo ratings yet

- ESB - Catalogo Passive Das 10 3Document105 pagesESB - Catalogo Passive Das 10 3Witto PereNo ratings yet

- T103 InstructionsDocument1 pageT103 Instructionsjtcool74No ratings yet

- Ques AnswerDocument8 pagesQues AnswerRafeek makramNo ratings yet

- Composite Cores in Current TransformersDocument5 pagesComposite Cores in Current TransformersMahdiNo ratings yet

- Lab 3Document8 pagesLab 3E24106610許翰翔No ratings yet

- Densitron Corporation: Handling PrecautionsDocument8 pagesDensitron Corporation: Handling PrecautionsMauricio Garcia VentNo ratings yet

- Robot Wifi CamDocument14 pagesRobot Wifi CamjoseplinNo ratings yet

- Major SS Ring Main SS Load DistributionDocument99 pagesMajor SS Ring Main SS Load DistributionAmir IbrahimNo ratings yet

- LK-023-IDN (Temperature, Mass, Volume, Pressure, Length, & Time)Document9 pagesLK-023-IDN (Temperature, Mass, Volume, Pressure, Length, & Time)Aries SupiyantoNo ratings yet

- Coffee Lake H/S Platform System Memory Interface: Technical White PaperDocument51 pagesCoffee Lake H/S Platform System Memory Interface: Technical White PaperagxinNo ratings yet

- PZ SeriesDocument28 pagesPZ SeriesSomiar TradingNo ratings yet

- Automobile Brake Failure IndicatorDocument5 pagesAutomobile Brake Failure IndicatorBhavana GummaNo ratings yet

- BSI Standards Publication: Arc Welding EquipmentDocument30 pagesBSI Standards Publication: Arc Welding EquipmentAlex Alex100% (1)

- 150Mbps PDIC Receiver - SevastopolDocument28 pages150Mbps PDIC Receiver - SevastopoldcalexNo ratings yet

- BEE Experiment 2Document3 pagesBEE Experiment 2MD ZunedNo ratings yet

- Solar Net Metering AgreementDocument7 pagesSolar Net Metering AgreementLogesh KumarNo ratings yet

- 21.alcohol Sensing Display With Alarm ProjectDocument15 pages21.alcohol Sensing Display With Alarm ProjectTrishika DebnathNo ratings yet

- SP315-51Pegatron ST5DB Rev1.0Document82 pagesSP315-51Pegatron ST5DB Rev1.0JOSE PAZNo ratings yet

- Linear Integrated Circuits - EC2254Document77 pagesLinear Integrated Circuits - EC2254Muthu LakiNo ratings yet