Professional Documents

Culture Documents

Syllabus Testing 2023

Syllabus Testing 2023

Uploaded by

victor504320 ratings0% found this document useful (0 votes)

3 views1 pageOriginal Title

syllabus.testing.2023

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

3 views1 pageSyllabus Testing 2023

Syllabus Testing 2023

Uploaded by

victor50432Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 1

清華大學 電機工程學系 碩博士班 111 學年度第二學期, Spring 2023

EE-6250 超大型積體電路測試 (VLSI Testing)

教師: 黃錫瑜 Shi-Yu Huang (syhuang@ee.nthu.edu.tw)

教材請上【國立清華大學-eeclass數位學習系統】https://eeclass.nthu.edu.tw/ 下載

上課時間與地點: 星期一 6:30-9:20pm @台達館 216 教室

若須採線上課程: https://meet.google.com/iip-jugm-tka

1. 課程說明 (General Description)

This course is devoted to the fundamental knowledge of testing Very Large-Scale Integrated circuits (VLSI). The emphasis

is on the investigation of various technically feasible test solutions combining both Design-for-Testability hardware and

Computer-Aided Design algorithms for test-pattern generation to make sure the overall testability and quality of manufactured ICs.

It begins with the topics of fault modeling and fault simulation, followed by the algorithms of Automatic Test Pattern Generation

(ATPG). Then, widely adopted Design-for-Testability (DFT) techniques in IC design industry, such as Scan Test, Built-In

Self-Test (BIST), Test Compression, and IEEE-1149.1 Boundary Scan Test Standard will be elaborated. At the final stage, some

selective advanced topics such as power & clock networks testing and logic fault diagnosis will also be discussed. Upon the

completion of this course, the students will know how to apply all kinds of test solutions to make an IC easily testable and reliable

in a cost-effective way.

2. 助教 (TAs) @ 台達館 923 實驗室

賴淇(chilai.asdf@gmail.com) 許志嘉(jesse16180@gmail.com) 鄧向凱(stan888957@gmail.com)

3. 先修課程 (Prerequisites)

程式設計,邏輯設計,積體電路設計導論

4. 修完此課程後之效益 (Benefits After Taking this Course)

Students who have taken this course will become knowledgeable about state-of-the-art VLSI test and diagnosis technologies

that are often mandatory if working as an IC designer and/or IC testing or product engineer in the industry.

5. 主要參考書 (Textbook):

⚫ L.-T. Wang, C.-W. Wu, and X. Wen, “VLSI Test Principles and Architectures: Design for Testability,” Morgan

Kaufmann, July 2006.

6. 教學方式 (Teaching Method)

以使用 PowerPoint 投影片為主的課堂討論 (Lectures using PowerPoint Slides)

7. 成績考核: 課堂出席情況 5%,作業 (實作型) 30%,期中考 30%,期末考 35%

8. 教學大綱 (Course Outline)

1. Introduction

2. Fault Modeling

3. Fault Simulation

4. Design-for-Testability (DFT) and Scan Test

5. Automatic Test Pattern Generation (ATPG)

6. Delay Test

7. Built-In Self-Test (BIST)

8. Test Compression

9. Boundary Scan Test

10. Testing Clock and Power Network

11. Fault Diagnosis

12. Scan Chain Diagnosis using Artificial Neural Network

A1: Review of Digital Circuit Design Methodology

A2: Quick-and-Cool Scan Test Methodology

A3: Optimization by Branch-and-Bound Search

9. 考試資訊: (上課教室) 6:30-8:10pm, Midterm Exam. on April 17, 2023, Final Exam. on June 12, 2023.

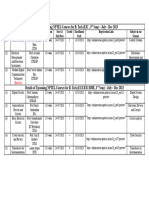

10. 進度表 (Schedule)

Feb. 20, 2023 先由助教播放錄影課程,複習 Cell-based design tools。

April 24, 2023 先由助教擔任 Tutorial 講師,介紹 Test Tool (Scan Insertion + ATPG) 之使用方式。

Week 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18

Month Feb. 2023 March 2023 April 2023 May 2023 June 2023

Date

13 20 27 6 13 20 27 3 10 17 24 1 8 15 22 29 5 12

星期一

預估進度 C1 C2 放假日 C3 C4 C5 C5 放假日 C6 期中考 C7 C7 C8 C9 C10 C11 C12 期末考

You might also like

- Design For Testability With DFT Compiler and TetraMaxDocument191 pagesDesign For Testability With DFT Compiler and TetraMaxerik_xfan100% (1)

- COMSATS University Islamabad: Course Description FileDocument8 pagesCOMSATS University Islamabad: Course Description FileSouban JavedNo ratings yet

- Structural Lab 1Document21 pagesStructural Lab 1Stefhany RapioNo ratings yet

- TestingDocument13 pagesTestingJayamani KrishnanNo ratings yet

- Chapter 16: Design For Testability: Prof. Ming-Bo LinDocument59 pagesChapter 16: Design For Testability: Prof. Ming-Bo Linreddydv100% (1)

- A Pulse Oximeter System, OxiSense, With Embedded Signal Processing Using An Ultra-Low Power ASIC Designed For Testability PDFDocument10 pagesA Pulse Oximeter System, OxiSense, With Embedded Signal Processing Using An Ultra-Low Power ASIC Designed For Testability PDFNeyronal MelgarNo ratings yet

- Semester-IV: Computer Networking Course Code: 4340703Document10 pagesSemester-IV: Computer Networking Course Code: 4340703Zaidali BurmawalaNo ratings yet

- 5th & 6thDocument49 pages5th & 6thViru SahnerNo ratings yet

- ECE 7995-Embedded Systems For Vehicles-Syllabus S17 - v2Document6 pagesECE 7995-Embedded Systems For Vehicles-Syllabus S17 - v2AsraButoolNo ratings yet

- Diploma Engineering: Laboratory ManualDocument112 pagesDiploma Engineering: Laboratory ManualDHRUV PATELNo ratings yet

- III Yr Students CirculationDocument2 pagesIII Yr Students CirculationNaveen SNo ratings yet

- AI and Machine LearningDocument92 pagesAI and Machine LearningRAVINo ratings yet

- MCA NEW IInd Semester 2023-24Document9 pagesMCA NEW IInd Semester 2023-24Ujjwal BarmanNo ratings yet

- Final DocumentDocument61 pagesFinal Documentandirajukeshavakrishna6945No ratings yet

- Building Crack Detection Using Deep Learning TechniquesDocument11 pagesBuilding Crack Detection Using Deep Learning TechniquesIJRASETPublicationsNo ratings yet

- Offered Mooc Ay - 2022-23Document1 pageOffered Mooc Ay - 2022-23rajeshbhramaNo ratings yet

- AKTU Admit CardDocument1 pageAKTU Admit CardUjjwal GargNo ratings yet

- Projects 1920 C 15Document92 pagesProjects 1920 C 15Murtaza KathawalaNo ratings yet

- Syll BTech Aff 130423Document51 pagesSyll BTech Aff 130423schoolvodNo ratings yet

- CSI - 468 - A - Syllabus - Spring 2021Document6 pagesCSI - 468 - A - Syllabus - Spring 2021Saer El MasriNo ratings yet

- ES Course OutlineDocument2 pagesES Course OutlineBurtukan EdaoNo ratings yet

- Lung Tuberculosis Detection Using CT ImagesDocument5 pagesLung Tuberculosis Detection Using CT ImagesPrashansa KhandelwalNo ratings yet

- mpr1 mpr1 mpr1 mpr1 mpr1 mpr1Document93 pagesmpr1 mpr1 mpr1 mpr1 mpr1 mpr1alfxxuNo ratings yet

- Thiruvalluvar University Master of Computer Application Cbcs Pattern (With Effect From 2020 - 2021) The Course of Study and Scheme of ExaminationDocument44 pagesThiruvalluvar University Master of Computer Application Cbcs Pattern (With Effect From 2020 - 2021) The Course of Study and Scheme of ExaminationPrabu KumarNo ratings yet

- Teaching Plan SOCTP W23Document2 pagesTeaching Plan SOCTP W23pankaj chandankhedeNo ratings yet

- B.tech AdmitCardsCollegeRollNo CSE 5THDocument46 pagesB.tech AdmitCardsCollegeRollNo CSE 5THAnujNo ratings yet

- Assigment FiveDocument15 pagesAssigment FivemelsewNo ratings yet

- Manual EJ6I CND 22634 120421Document169 pagesManual EJ6I CND 22634 120421Ritika KambleNo ratings yet

- Packing Automation in A High Variety Conveyor Line Via Image ClassificationDocument39 pagesPacking Automation in A High Variety Conveyor Line Via Image Classificationsobako123No ratings yet

- Summer Training On STAAD Pro V8iDocument24 pagesSummer Training On STAAD Pro V8iParwin Mards86% (7)

- MT Ce Se 2018Document58 pagesMT Ce Se 2018Vineetha KrishnanNo ratings yet

- SRE Assignment 062021 - Coppa Updated 10062021Document10 pagesSRE Assignment 062021 - Coppa Updated 10062021ccnimingNo ratings yet

- NPTEL Courses - 3rd - 5th Sem - ECE - EICDocument1 pageNPTEL Courses - 3rd - 5th Sem - ECE - EICsawasthi.1801No ratings yet

- CSE 4 NotesDocument22 pagesCSE 4 NotesCSE SSGINo ratings yet

- Online Examination Hall Seating ArrangementDocument5 pagesOnline Examination Hall Seating ArrangementIJRASETPublicationsNo ratings yet

- Mtec Ece-Vlsi-Design 2018Document67 pagesMtec Ece-Vlsi-Design 2018jayan dNo ratings yet

- Mca New Assignment ListDocument11 pagesMca New Assignment ListHemraj ChhonkarNo ratings yet

- 06/02/2022 1 ANAMIKA TIWARI Discrete Structures Unit 2Document76 pages06/02/2022 1 ANAMIKA TIWARI Discrete Structures Unit 2Ruag ShradaNo ratings yet

- Venkat ReportDocument30 pagesVenkat ReportvenkatNo ratings yet

- Report StudentVotingProjectDocument53 pagesReport StudentVotingProjectdhammumudigondaNo ratings yet

- Online Examination System Using JavaDocument7 pagesOnline Examination System Using JavaIJRASETPublicationsNo ratings yet

- (BNJ10903) LAB 01 - Resistors Network and CircuitDocument15 pages(BNJ10903) LAB 01 - Resistors Network and CircuitMuhammad NaufalNo ratings yet

- Vlsisyll 22Document91 pagesVlsisyll 22MaheshReddyNo ratings yet

- UT Dallas Syllabus For cs4376.502 05f Taught by Anthony Sullivan (Sulliva)Document7 pagesUT Dallas Syllabus For cs4376.502 05f Taught by Anthony Sullivan (Sulliva)UT Dallas Provost's Technology GroupNo ratings yet

- 4026MAA EEC - Manufacturing Technology and Materials: Faculty of Engineering, Environment and ComputingDocument5 pages4026MAA EEC - Manufacturing Technology and Materials: Faculty of Engineering, Environment and ComputingwahajNo ratings yet

- IPU BTech CSE Syllabus All 4 Year PDFDocument430 pagesIPU BTech CSE Syllabus All 4 Year PDFMritunjay PandeyNo ratings yet

- Course Outline - INFO8500 (103) - Network Security IIDocument3 pagesCourse Outline - INFO8500 (103) - Network Security IIJonkers LeeNo ratings yet

- Computer Systems: Unit Guide - On Campus Semester One, 2010Document21 pagesComputer Systems: Unit Guide - On Campus Semester One, 2010rar93No ratings yet

- Launches: Junior EngineerDocument7 pagesLaunches: Junior EngineerBANARSEE LALNo ratings yet

- v2 22cs2103a-P Aoop Lab Work Book CompleteDocument242 pagesv2 22cs2103a-P Aoop Lab Work Book Completejayasai268853No ratings yet

- Front Pages With Pages RemovedDocument8 pagesFront Pages With Pages RemovedGayathri kNo ratings yet

- Cse - 5thDocument46 pagesCse - 5thSakshi SharmaNo ratings yet

- DWMMDocument8 pagesDWMMSangita HazraNo ratings yet

- Final Term Exam Fall 2020 - 2Document4 pagesFinal Term Exam Fall 2020 - 2Muhammad Sumair AlamNo ratings yet

- Gs Ee287-02Document7 pagesGs Ee287-02MelissaNo ratings yet

- TH - 1 AhmadDocument8 pagesTH - 1 AhmadHaseeb AmjadNo ratings yet

- VALUE ADDED 2020-CIVIL - DR - Sanjay - TiwariDocument1 pageVALUE ADDED 2020-CIVIL - DR - Sanjay - TiwariAdityaNo ratings yet

- BE - (IT) - V & VI Sem AMC 2020-21Document60 pagesBE - (IT) - V & VI Sem AMC 2020-21Anoohya ChNo ratings yet

- K. J. Somaiya College of Engineering, Mumbai-77Document8 pagesK. J. Somaiya College of Engineering, Mumbai-77CHINTAN MODINo ratings yet

- Software Engineering Lab Report: Siddaganga Institute of TechnologyDocument58 pagesSoftware Engineering Lab Report: Siddaganga Institute of Technologygowdaveeresh494No ratings yet

- EMCS BrochureDocument1 pageEMCS BrochureEmon KhanNo ratings yet

- Alpin Ak Online Examination SystemDocument61 pagesAlpin Ak Online Examination SystemANDRU PRADHEEPNo ratings yet

- ANSYS Workbench 2023 R2: A Tutorial Approach, 6th EditionFrom EverandANSYS Workbench 2023 R2: A Tutorial Approach, 6th EditionNo ratings yet

- Lecture 1Document40 pagesLecture 1balaji ENo ratings yet

- Observability & Controllability: 12: Design For Testability 1Document29 pagesObservability & Controllability: 12: Design For Testability 1nation first100% (1)

- Vlsi TestabilityDocument50 pagesVlsi TestabilityjeevithpaulNo ratings yet

- Et Ug PmbistDocument40 pagesEt Ug PmbistNitish KumarNo ratings yet

- Multiservicer User Manual: Version: 1.8 - Hw2 Code No. 20 750 505Document64 pagesMultiservicer User Manual: Version: 1.8 - Hw2 Code No. 20 750 505ejmiejmiNo ratings yet

- Testing and Design-for-Testability (DFT) For Digital Integrated CircuitsDocument95 pagesTesting and Design-for-Testability (DFT) For Digital Integrated Circuitsnagabhairu anusha100% (1)

- Design VerificationDocument16 pagesDesign VerificationPraveen KethipalliNo ratings yet

- Louis J Gullo - Jack Dixon - Design For Maintainability (2021, Wiley) - Libgen - LiDocument383 pagesLouis J Gullo - Jack Dixon - Design For Maintainability (2021, Wiley) - Libgen - LiJean IsidroNo ratings yet

- Design For Testability Design For Testability - Organization OrganizationDocument28 pagesDesign For Testability Design For Testability - Organization OrganizationNeusilica school of VLSINo ratings yet

- Test Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeDocument6 pagesTest Logic Insertion For Optimization of Testing Parameters On Lower Technology NodeshaguftaNo ratings yet

- (MIT Press Series in Computer Systems) Hideo Fujiwara-Logic Testing and Design For testability-MIT Press (1985) PDFDocument293 pages(MIT Press Series in Computer Systems) Hideo Fujiwara-Logic Testing and Design For testability-MIT Press (1985) PDFAayush100% (1)

- JG-004-DTF (Design For Test Flow)Document19 pagesJG-004-DTF (Design For Test Flow)Sanil Kumar PillaiNo ratings yet

- Ee 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduDocument30 pagesEe 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EdusanthiyadevNo ratings yet

- Design For Testability (DFT) : Vlsi Ii: Design of Very Large Scale Integration CircuitsDocument22 pagesDesign For Testability (DFT) : Vlsi Ii: Design of Very Large Scale Integration CircuitsSiam HasanNo ratings yet

- Thesis On LFSRDocument104 pagesThesis On LFSRKaran RoyNo ratings yet

- Vlsi Module-5Document56 pagesVlsi Module-5Phanindra ReddyNo ratings yet

- Genus Synthesis Solution DsDocument3 pagesGenus Synthesis Solution DsHistPro WebNo ratings yet

- Primer: IEEE STD 1149.1 (JTAG) TestabilityDocument130 pagesPrimer: IEEE STD 1149.1 (JTAG) TestabilityteomondoNo ratings yet

- CTL The Language For Describing Core-Based TestDocument10 pagesCTL The Language For Describing Core-Based Testimoon63No ratings yet

- Testability For Resistive Open Defects by Electrical Interconnect Test of 3D ICs Without Boundary Scan Flip FlopsDocument2 pagesTestability For Resistive Open Defects by Electrical Interconnect Test of 3D ICs Without Boundary Scan Flip Flopsjiangcj27No ratings yet

- Asic Design FlowDocument25 pagesAsic Design FlowKarishma PotnuruNo ratings yet

- Test-Expert BrochureDocument6 pagesTest-Expert Brochuremouloud hadbiiNo ratings yet

- Design For TestabilityDocument26 pagesDesign For TestabilityDenise NelsonNo ratings yet

- DFM Training Course-2Document6 pagesDFM Training Course-2Mauricio CastroNo ratings yet

- DFT Scan Insertion: VLSI Testing and Design For TestabilityDocument19 pagesDFT Scan Insertion: VLSI Testing and Design For TestabilityHuzur AhmedNo ratings yet

- Testing of Digital Vlsi CircuitsDocument2 pagesTesting of Digital Vlsi CircuitsNikhilRaviNo ratings yet