Professional Documents

Culture Documents

301 RISC Processor Fa14

301 RISC Processor Fa14

Uploaded by

2017a.techOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

301 RISC Processor Fa14

301 RISC Processor Fa14

Uploaded by

2017a.techCopyright:

Available Formats

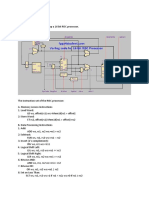

CECS 301 Computer Logic Design II © 2014 R. W.

Allison

Fall 2014 CECS 301 – 16‐bit RISC Processor

I. Application You are to complete the design of an 16-bit “Reduced Instruction Set Computing” (RISC)

processor that will fetch and execute a simple set of 16-bit machine instructions.

II. Instruction Set Architecture -- The 16 opcodes for 16-bit RISC Processor will be encoded in bits IR[15:9]

of the instruction register. IR[8:6] will have the binary code for the destination register. IR[5:3] and IR[2:0]

will have the binary codes for the source registers.

A. Memory Structure

1. 256x16 address space

2. Each memory location holds one 16-bit word.

B. Processor Register Set (available to user)

1. Eight 16-bit integer registers (R0, R1, R2, R3, R4, R5, R6 and R7).

2. 16-bit Program Counter (PC).

3. Flags Register (N, Z, C)

C. Data Types -- 16-bit single word signed integer (i.e. -32768 to +32767)

D. Addressing Modes

1. Immediate (16-bit integer, in a “trailing word”)

2. Register

3. Register indirect (load, store and jmp)

4. PC relative (je, jne and jc)

E. Instruction Opcodes/Formatting

Instructions Opcodes Instructions Opcodes

Name Opcodes Name Opcodes

add 111_0000 load 111_1000

double‐source

sub 111_0001 operands store 111_1001 load/store,

halt

cmp 111_0010 loadi 111_1010

halt 111_1011

mov 111_0011

shl 111_0100 je 111_1100

single-source

shr 111_0101 operands

jne 111_1101 jumps

inc 111_0110 jc 111_1110

dec 111_0111 jmp 111_1111

The basic format for the instructions is shown below:

15 9 8 6 5 3 2 0

opcode dest_reg src1_reg src2_reg

301 RISC Specifications – Page 1

CECS 301 Computer Logic Design II © 2014 R. W. Allison

E. Instruction Opcodes/Formatting (cont.)

1. Double‐source op’s: all these instructions are register based. No memory accesses are allowed.

15 9 8 6 5 3 2 0

opcode dest_reg src1_reg src2_reg

Triple operand operations (i.e. add / sub / cmp) are to be performed as:

dest_reg src1_reg operation src2_reg

Example: sub r4, r2, r3 ; {N,Z,C, r4} r2 ‐ r3 [Binary code: 1110001_100_010_011]

cmp r6, r7 ; {N,Z,C} r6 ‐ r7 [Binary code: 1110010_000_110_111]

2. Single‐source op’s: all single-operand (i.e. single source operand) instructions are register based.

No memory accesses are allowed.

All single source operand operations (i.e. mov / shl / shr/ inc/ dec) are to be performed as:

dest_reg operation src2_reg

Examples: dec r4 ; {N,Z,C, r4} r4 – 1 [Binary code: 1110111_100_000_100]

shl r5, r1 ; {N,Z,C, r5} r1 << 1 [Binary code: 1110100_101_000_001]

mov r6, r7 ; r6 r7 [Binary code: 1110011_110_000_111]

3. Load, Store, Halt format:

For Load, the 16-bit word in a memory location (pointed at by register (R0..R7) specified by the

“src2_reg” field) is transferred into the register specified by the “dest_reg” field.

For Store, the 16-bit register specified by the “src2_reg” field is transferred to a memory

location (pointed at by register (R0..R7) specified by the “dest_reg” field).

For Load immediate, the 16-bit immediate value (located in the trailing word) is transferred into

the register specified by the “dest_reg” field. This is the only “32-bit instruction.”

For Halt, the RISC processor will stop fetching instructions, going to a state that waits for reset.

4. Conditional jumps (relative), Jump (register indirect): the result of a “jump” type instruction is

to change the PC (if applicable). The “effective address” of the “conditional jump” instructions is

calculated by adding the 16-bit “sign-extension” of a 8-bit signed offset to the Program Counter.

15 9 8 7 0

opcode 0 8-bit signed offset

Example: jne -5 {if Z = 0, PC PC + 1111111111111011} [Binary code: 1111101_0_11111011]

The “effective address” of the “unconditional” jump instruction is the contents of the src2_reg.

15 9 8 6 5 3 2 0

opcode src2_reg

Example: jmp r6 {PC r6} [Binary code: 1111111_000_000_110]

F. Reset

In response to an external reset input, your processor should do the following:

(1) PC 00h (2) Flags (N,Z,C) 0002 (3) Goto the “fetch state”

301 RISC Specifications – Page 2

You might also like

- Sol3e Preint U3 Progress Test BDocument5 pagesSol3e Preint U3 Progress Test Bcherska antonina100% (1)

- The Rocc Doc V2: An Introduction To The Rocket Custom Coprocessor InterfaceDocument11 pagesThe Rocc Doc V2: An Introduction To The Rocket Custom Coprocessor Interfacekbkkr0% (1)

- 4 - Komyo Reiki Manual ShinpidenDocument29 pages4 - Komyo Reiki Manual ShinpidenJotaro KashiharaNo ratings yet

- 2022HI400070G NiveditaDocument27 pages2022HI400070G NiveditaNivedita Acharyya 2035No ratings yet

- PRA1Document15 pagesPRA1najlaecasalsgraciaNo ratings yet

- Workshop SlidesDocument73 pagesWorkshop Slidesoscar tebarNo ratings yet

- Lecture 08Document17 pagesLecture 08Swetha Rani MunirajuNo ratings yet

- Week 04Document68 pagesWeek 04aroosa naheedNo ratings yet

- F2010 552 Project DescriptionDocument6 pagesF2010 552 Project DescriptionJamil_fawadNo ratings yet

- Lectures 3-4: MIPS Instructions: MotivationDocument22 pagesLectures 3-4: MIPS Instructions: Motivationbilo044No ratings yet

- Arm InstDocument75 pagesArm InstJohnJohnNo ratings yet

- Assembler 1Document45 pagesAssembler 1Ebnazer JamesNo ratings yet

- SS AssemblersDocument24 pagesSS Assemblershari krishnanNo ratings yet

- Experiment 5Document7 pagesExperiment 5Kanwal GillNo ratings yet

- ProblemDescriptionDocument13 pagesProblemDescriptionShivani MisraNo ratings yet

- Chapter 5 - The Processor: Datapath and ControlDocument101 pagesChapter 5 - The Processor: Datapath and Controlapi-26072581No ratings yet

- Introduction To RISC and CISC:: RISC (Reduced Instruction Set Computer)Document62 pagesIntroduction To RISC and CISC:: RISC (Reduced Instruction Set Computer)pinkgirl2519No ratings yet

- Arm Instruction 2 - 001Document26 pagesArm Instruction 2 - 001Ankit SanghviNo ratings yet

- FPGA Microprocessor: ECE 428 Programmable ASIC DesignDocument20 pagesFPGA Microprocessor: ECE 428 Programmable ASIC DesignHuzur AhmedNo ratings yet

- ACE201slides 8Document75 pagesACE201slides 8alexistheNo ratings yet

- MP SoluDocument21 pagesMP SoluAhmad MukaddasNo ratings yet

- Lab 5 DR Muslim (Latest)Document15 pagesLab 5 DR Muslim (Latest)a ThanhNo ratings yet

- PDF 2Document13 pagesPDF 2Nivedita Acharyya 2035No ratings yet

- Hard Disk Drives ControllersDocument50 pagesHard Disk Drives Controllersatorresh090675No ratings yet

- Assembly LanguageDocument29 pagesAssembly Languagemritunjay bihari singhNo ratings yet

- Chapter 3 Instructions ARMDocument35 pagesChapter 3 Instructions ARMSlaney AguiarNo ratings yet

- Chapter 05 - Msp430 IsaDocument71 pagesChapter 05 - Msp430 Isaokocha712No ratings yet

- PDF 1Document17 pagesPDF 1Nivedita Acharyya 2035No ratings yet

- c64 Interrupts Eng Part03Document5 pagesc64 Interrupts Eng Part03olivier bernhardNo ratings yet

- Central Processing UnitDocument11 pagesCentral Processing UnitPace InfotechNo ratings yet

- Basic Microprocessor: Barbaros ÖzdemirelDocument24 pagesBasic Microprocessor: Barbaros ÖzdemirelAyberk Furkan YağdıNo ratings yet

- Fetch Execute CycleDocument17 pagesFetch Execute CycleMuhammad Ehtisham HassanNo ratings yet

- The Register Set of Msp430x5x SeriesDocument2 pagesThe Register Set of Msp430x5x SeriesTwinkle RatnaNo ratings yet

- 04 - Instruction Set Architecture-RV Part IIIDocument56 pages04 - Instruction Set Architecture-RV Part IIINadun Sasanga KumarasingheNo ratings yet

- 6016 4Document19 pages6016 4Ahmed QaziNo ratings yet

- Von Neuman Model Part-2Document42 pagesVon Neuman Model Part-2G.PranithaNo ratings yet

- A RISC-Architecture As Target: 9.1. Resources and RegistersDocument64 pagesA RISC-Architecture As Target: 9.1. Resources and RegistersanikaNo ratings yet

- MIC 15 - Arduino AssemblyDocument11 pagesMIC 15 - Arduino Assemblysaleh buenqNo ratings yet

- Assembler VerilogDocument9 pagesAssembler VerilogAyush GeraNo ratings yet

- Coa VL - 1Document55 pagesCoa VL - 1Kasi BandlaNo ratings yet

- Computer System Architecture Assignment: Submitted To:-Submitted By:-Mayank Sharma Roll No.:-19hcs4034Document37 pagesComputer System Architecture Assignment: Submitted To:-Submitted By:-Mayank Sharma Roll No.:-19hcs4034Anirban BhattacharjeeNo ratings yet

- 8085 Microprocessor Architecture and Programming-1Document92 pages8085 Microprocessor Architecture and Programming-1ShubhamNo ratings yet

- Arm&Es Module2Document148 pagesArm&Es Module2manjunathanaikvNo ratings yet

- Interrupts & PollingDocument10 pagesInterrupts & Pollingwazazzu3349No ratings yet

- Chapter 08 Processor DesignDocument70 pagesChapter 08 Processor Designsudah15No ratings yet

- Computer Architechture ReportDocument15 pagesComputer Architechture ReportNguyn LNo ratings yet

- 1 2. Objective 2 3. System Description and Design 3 4. Codes 9 5. Simulation Results 18 6. Conclusion 19 7. References 20Document21 pages1 2. Objective 2 3. System Description and Design 3 4. Codes 9 5. Simulation Results 18 6. Conclusion 19 7. References 20nishant_88No ratings yet

- Assembler Linker: Source Program Object CodeDocument15 pagesAssembler Linker: Source Program Object CodeRavish KumarNo ratings yet

- The ARM Instruction Set: Advanced RISC MachinesDocument58 pagesThe ARM Instruction Set: Advanced RISC MachinesPoorva RathoreNo ratings yet

- 2021 Qna EsDocument10 pages2021 Qna Estemp.prathampalNo ratings yet

- Lesson 13Document27 pagesLesson 13kadaNo ratings yet

- Chapter 3: Introduction To Assembly Language Programming: CEG2400 - Microcomputer SystemsDocument57 pagesChapter 3: Introduction To Assembly Language Programming: CEG2400 - Microcomputer SystemsRANJITHANo ratings yet

- Wipro Confidential: Stack Tracing and Variable Arguments in C - WorkshopDocument15 pagesWipro Confidential: Stack Tracing and Variable Arguments in C - WorkshopPrasanna KakumanuNo ratings yet

- 8051 Microcontroller: Assembly Language ProgrammingDocument23 pages8051 Microcontroller: Assembly Language ProgrammingVaibhav GodboleNo ratings yet

- Extracted Datasheet Pic16f8xa Part2Document7 pagesExtracted Datasheet Pic16f8xa Part2hajarelbekaryNo ratings yet

- 16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Document4 pages16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Kyra LathonNo ratings yet

- 22sp-041-cs Lab3 CO&ALDocument8 pages22sp-041-cs Lab3 CO&ALSubul RazaNo ratings yet

- Control Unit Design: Decoder &Document30 pagesControl Unit Design: Decoder &blackmaverick0912No ratings yet

- Simple Machine ArchitectureDocument20 pagesSimple Machine Architecturejoe corteseNo ratings yet

- PicoProcessor InstructionDocument3 pagesPicoProcessor Instructionapi-27229361No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- James Jackson - Figurative-Language-Worksheet-01Document2 pagesJames Jackson - Figurative-Language-Worksheet-01Yoshino Jackson0% (1)

- BỘ ĐỀ ÔN TẬP TIẾNG ANH 4Document5 pagesBỘ ĐỀ ÔN TẬP TIẾNG ANH 4Nhu Trang Phung ThiNo ratings yet

- Unit 2 - Arrays and PointersDocument7 pagesUnit 2 - Arrays and PointersKrishna KapadiaNo ratings yet

- O Level Math Syllabus BreakupDocument8 pagesO Level Math Syllabus BreakupMariyum SaajidNo ratings yet

- English CoursesDocument21 pagesEnglish CoursesDebili YacineNo ratings yet

- PPTG4 W THEMEDocument25 pagesPPTG4 W THEMErandolf wassigNo ratings yet

- 0548 w09 Ms 1 PDFDocument7 pages0548 w09 Ms 1 PDFCatherine WreyfordNo ratings yet

- TCS NQT Online Test Pattern: Section Order Section # Qs Duration (Minutes)Document33 pagesTCS NQT Online Test Pattern: Section Order Section # Qs Duration (Minutes)smkcoolllll-10No ratings yet

- A & AD Error CodesDocument186 pagesA & AD Error CodesCHIROIUNo ratings yet

- 418 Automatic Railway Gate Control SystemDocument27 pages418 Automatic Railway Gate Control SystemRam VBIT100% (1)

- 1st Periodic Test - G7 EnglishDocument4 pages1st Periodic Test - G7 EnglishErlindaLozanoGarciaNo ratings yet

- Anshu Kumar: Education SkillsDocument1 pageAnshu Kumar: Education SkillsAnshu ThakurNo ratings yet

- Battle of Ages 3Document135 pagesBattle of Ages 3Olga MunetsiNo ratings yet

- English 8 - Exam Q4Document3 pagesEnglish 8 - Exam Q4joydesiarNo ratings yet

- Noun ErrorsDocument3 pagesNoun ErrorsManasvi PanwarNo ratings yet

- Down Syndrome Parent GuideDocument40 pagesDown Syndrome Parent GuideDr-Mudassar Ali PT100% (1)

- Romeo and JulietDocument8 pagesRomeo and Julietc.ralphNo ratings yet

- Elements of PoetryDocument13 pagesElements of PoetryStephanie AnabaNo ratings yet

- Partial Differential and Integral EquationsDocument367 pagesPartial Differential and Integral EquationsBuston JumaevNo ratings yet

- Variables & Constants in C++ - Types of VariablesDocument6 pagesVariables & Constants in C++ - Types of Variablesyanachii22No ratings yet

- Du PHD InterviewDocument10 pagesDu PHD InterviewRahul JatNo ratings yet

- The Union, Intersect, Minus OperatorsDocument4 pagesThe Union, Intersect, Minus Operators20f4a7bcNo ratings yet

- CLASS 9th CBSE COMPUTER TEST - ASSIGNMENTDocument2 pagesCLASS 9th CBSE COMPUTER TEST - ASSIGNMENTAnonymous zrAfrkPOJ7No ratings yet

- Canada'S Chess Magazine For Kids: September 2019 Number 145Document27 pagesCanada'S Chess Magazine For Kids: September 2019 Number 145Bolo BTNo ratings yet

- ANALYTIC GEOMETRY Rev1Document8 pagesANALYTIC GEOMETRY Rev1HERMINIO MENDOZANo ratings yet

- Human Lie Detectorpdf PDFDocument45 pagesHuman Lie Detectorpdf PDFHaydee RocaNo ratings yet

- English LiteratureDocument6 pagesEnglish LiteratureSopa De PolloNo ratings yet

- EthicsDocument3 pagesEthicsJe Anne Rose CanonesNo ratings yet