Professional Documents

Culture Documents

A Review Report On Multi-Voltage Rule Check - HBRP Publication

A Review Report On Multi-Voltage Rule Check - HBRP Publication

Uploaded by

Saisantosh RajputhCopyright:

Available Formats

You might also like

- TC1767 Microcontroller Manual PDFDocument1,892 pagesTC1767 Microcontroller Manual PDFpierpaolo aldrigo100% (1)

- CMOS C35 Design RulesDocument60 pagesCMOS C35 Design RulesFernando Sánchez HernándezNo ratings yet

- Power Gating - Power Management Technique: VLSI Basics and Interview QuestionsDocument12 pagesPower Gating - Power Management Technique: VLSI Basics and Interview QuestionsRohith RajNo ratings yet

- Survey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyDocument15 pagesSurvey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyAnonymous e4UpOQEPNo ratings yet

- Design Stratigies of Low Power Voltage Level Shifter Circuits For Multi Supply SystemsDocument6 pagesDesign Stratigies of Low Power Voltage Level Shifter Circuits For Multi Supply SystemsIRJMETS JOURNALNo ratings yet

- IJETR032239Document5 pagesIJETR032239erpublicationNo ratings yet

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 pagesDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsNo ratings yet

- Review Article: Device and Circuit Design Challenges in The Digital Subthreshold Region For Ultralow-Power ApplicationsDocument16 pagesReview Article: Device and Circuit Design Challenges in The Digital Subthreshold Region For Ultralow-Power ApplicationsFemin VargheseNo ratings yet

- A Review of Low Power Processor DesignDocument10 pagesA Review of Low Power Processor DesignNalini RadhakrishnanNo ratings yet

- A Distributed Filter Within A Switching Converter For Application To 3-D Integrated CircuitsDocument11 pagesA Distributed Filter Within A Switching Converter For Application To 3-D Integrated CircuitsDaniel zanelattoNo ratings yet

- Leakage Power Reduction and Power Delay Product (PDP) Improvement Using Dual Stack MethodDocument9 pagesLeakage Power Reduction and Power Delay Product (PDP) Improvement Using Dual Stack MethoderpublicationNo ratings yet

- Power Analysis in Vlsi Designs: Electronics and Communication Engineering. Dronacharya College of Engineering, GurgaonDocument2 pagesPower Analysis in Vlsi Designs: Electronics and Communication Engineering. Dronacharya College of Engineering, GurgaonSudhanshu ShekharNo ratings yet

- VLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)Document3 pagesVLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)IPASJNo ratings yet

- Low Power VLSI Design Methodologies & Power ManagementDocument4 pagesLow Power VLSI Design Methodologies & Power ManagementGeetha Rani NNo ratings yet

- TP LeakagePowerOptimizationFlowDocument11 pagesTP LeakagePowerOptimizationFlowSathyanarayana RaoNo ratings yet

- Power Optimization For Low Power VLSI CircuitsDocument4 pagesPower Optimization For Low Power VLSI CircuitsCHARANNo ratings yet

- FORTRAN Based ApproachDocument22 pagesFORTRAN Based ApproachGS EKTANo ratings yet

- Analysis of Power Dissipation and Low PoDocument9 pagesAnalysis of Power Dissipation and Low PoClementeNo ratings yet

- DSP Based Control of Interleaved Boost ConverterDocument11 pagesDSP Based Control of Interleaved Boost ConverterDany ApablazaNo ratings yet

- Low Power Techniques For VLSI DesignDocument6 pagesLow Power Techniques For VLSI DesignjainatinNo ratings yet

- Bypassing Multiplier Design Techniques For Detecting Aging EffectDocument5 pagesBypassing Multiplier Design Techniques For Detecting Aging EffectInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorKiran KNo ratings yet

- Mixed-Signal IP Design Challenges in 28 NM and BeyondDocument14 pagesMixed-Signal IP Design Challenges in 28 NM and BeyondyvarshneyNo ratings yet

- An On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SDocument7 pagesAn On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SBhaskar YalamoluNo ratings yet

- A Review of Low Power Processor DesignDocument9 pagesA Review of Low Power Processor DesignNalini RadhakrishnanNo ratings yet

- AnnepuBaburao TSrinivasaRao 62Document5 pagesAnnepuBaburao TSrinivasaRao 62Ahmed HussainNo ratings yet

- Low PowerDocument48 pagesLow PowerRákêsh Råkêë100% (1)

- Design of A Novel Energy Efficient Double Tail Dynamic ComparatorDocument5 pagesDesign of A Novel Energy Efficient Double Tail Dynamic ComparatorerpublicationNo ratings yet

- Low Power Vlsi Design1Document23 pagesLow Power Vlsi Design1Shruthi GourishettiNo ratings yet

- Low-Power Circuits Using Dynamic Threshold DevicesDocument5 pagesLow-Power Circuits Using Dynamic Threshold DevicesGiang Nguyễn VănNo ratings yet

- ME Notes Unit 4 Part 3 Low Power IC and RFICsDocument5 pagesME Notes Unit 4 Part 3 Low Power IC and RFICssayan.transcuratorsNo ratings yet

- SCE 100nmDocument48 pagesSCE 100nmGoogle acntNo ratings yet

- A 09-V Input Discontinuous-Conduction-Mode Boost CDocument12 pagesA 09-V Input Discontinuous-Conduction-Mode Boost CDanial RazaNo ratings yet

- Design of Low Power and High Speed Components of SAR ADCDocument6 pagesDesign of Low Power and High Speed Components of SAR ADCSuraj Kumar PrustyNo ratings yet

- Effect of Process, Voltage and Temperature (PVT) Variations in LECTOR-B (Leakage Reduction Technique) at 70 NM Technology NodeDocument7 pagesEffect of Process, Voltage and Temperature (PVT) Variations in LECTOR-B (Leakage Reduction Technique) at 70 NM Technology NodeDiana MaldonadoNo ratings yet

- Low-Power Digital VLSI DesignDocument530 pagesLow-Power Digital VLSI DesignAllanki Sanyasi Rao50% (2)

- Modified Gdi Technique - A Power Efficient Method For Digital Circuit DesignDocument23 pagesModified Gdi Technique - A Power Efficient Method For Digital Circuit DesignswathiNo ratings yet

- Development of A Smart LED Lighting System: Rapid Prototyping ScenarioDocument6 pagesDevelopment of A Smart LED Lighting System: Rapid Prototyping ScenariocarlosNo ratings yet

- Low Power Vlsi ThesisDocument5 pagesLow Power Vlsi Thesismariapadillaomaha100% (2)

- D Flip FlopDocument5 pagesD Flip FlopNaveen Kumar RavillaNo ratings yet

- Column Bypassing Multiplier Implementation On FPGADocument17 pagesColumn Bypassing Multiplier Implementation On FPGAIJRASETPublicationsNo ratings yet

- Thesis FinalDocument75 pagesThesis FinalSHARIZA DAYANA RODRIGUEZ URRESTANo ratings yet

- Power Management and Delivery For High-Performance MicroprocessorsDocument4 pagesPower Management and Delivery For High-Performance Microprocessorsrizal iskandarNo ratings yet

- Kinget Matching OffsetDocument14 pagesKinget Matching OffsetMikeNo ratings yet

- Review Paper On Low Power VLSI Design Techniques: Neha Thakur, Deepak KumarDocument5 pagesReview Paper On Low Power VLSI Design Techniques: Neha Thakur, Deepak Kumarhamza shahbazNo ratings yet

- Energy Efficient CMOS Microprocessor DesignDocument10 pagesEnergy Efficient CMOS Microprocessor Designnew accNo ratings yet

- Efficient Design of 1Document7 pagesEfficient Design of 1sumathiNo ratings yet

- A 45 NM Resilient Microprocessor Core For Dynamic Variation ToleranceDocument15 pagesA 45 NM Resilient Microprocessor Core For Dynamic Variation ToleranceNguyen Van ToanNo ratings yet

- Cmos Low PowerDocument5 pagesCmos Low PowerbhoomikachawlaNo ratings yet

- On Interaction Between Internal ConverteDocument7 pagesOn Interaction Between Internal ConverteDalm DuduNo ratings yet

- A Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferDocument5 pagesA Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferRaja PosupoNo ratings yet

- Signal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhuDocument8 pagesSignal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhusalehNo ratings yet

- Dynamic Voltage (IR) Drop Analysis and Design Closure: Issues and ChallengesDocument7 pagesDynamic Voltage (IR) Drop Analysis and Design Closure: Issues and ChallengesRohit KatkarNo ratings yet

- Design & Analysis of Different Types of Sleepy Methods For Future TechnologiesDocument6 pagesDesign & Analysis of Different Types of Sleepy Methods For Future TechnologiesseventhsensegroupNo ratings yet

- 4 Bit Johnson CounterDocument6 pages4 Bit Johnson CountermahimaNo ratings yet

- Dynamic Voltage DropDocument7 pagesDynamic Voltage DropBaluvu Jagadish100% (1)

- Tunnel Fets For Ultra-Low Voltage Digital Vlsi Circuits: Part Ii-Evaluation at Circuit Level and Design PerspectivesDocument14 pagesTunnel Fets For Ultra-Low Voltage Digital Vlsi Circuits: Part Ii-Evaluation at Circuit Level and Design PerspectivesBappy DebnathNo ratings yet

- ECEG-4281-MDC-Lec 01 Fundamentals of MicroelectronicsDocument38 pagesECEG-4281-MDC-Lec 01 Fundamentals of MicroelectronicserenaNo ratings yet

- En - Steval-Strkt01 SchematicDocument7 pagesEn - Steval-Strkt01 SchematicGael Marciano RodríguezNo ratings yet

- Using Clcs in Real-Time Applications: Wwwproducts/En/Pic18F47Q10Document41 pagesUsing Clcs in Real-Time Applications: Wwwproducts/En/Pic18F47Q10Bruno LeppeNo ratings yet

- Using In-System Programming in Boundary-Scan Systems: TAP TimingDocument8 pagesUsing In-System Programming in Boundary-Scan Systems: TAP TimingNandhini IlangovanNo ratings yet

- EEE Software Lab Report On PspiceDocument9 pagesEEE Software Lab Report On PspiceSayem Mahmud (Sym)No ratings yet

- Comparison of I C Logic FamiliesDocument2 pagesComparison of I C Logic FamiliesVinod kumarNo ratings yet

- Mentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowDocument7 pagesMentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowbipbulNo ratings yet

- ARM Introduction & ArchitectureDocument33 pagesARM Introduction & ArchitectureSanjana PulapaNo ratings yet

- Bipolar Junction Transistors (BJTS) 1Document19 pagesBipolar Junction Transistors (BJTS) 1ጁንታው ነኝNo ratings yet

- Microcontroller - PPT 2. 2020Document13 pagesMicrocontroller - PPT 2. 2020Irvine ChibayaNo ratings yet

- Lab 13: Binary Counter Systems:: Three Stage Ripple Counter. Down Counters. Up/Down Counters. Altera 4count SymbolDocument5 pagesLab 13: Binary Counter Systems:: Three Stage Ripple Counter. Down Counters. Up/Down Counters. Altera 4count Symbolasin12336No ratings yet

- (WWW - Entrance-Exam - Net) - Tata ELXSI Placement Sample Paper 1Document9 pages(WWW - Entrance-Exam - Net) - Tata ELXSI Placement Sample Paper 1karthikNo ratings yet

- DE LAB ManualC-18 FinalDocument85 pagesDE LAB ManualC-18 FinalBRAGPW,Karimnagar 087No ratings yet

- Micom 87L LogicDocument4 pagesMicom 87L LogictajudeenNo ratings yet

- Mobile ProcessorDocument3 pagesMobile ProcessorMohamd barcaNo ratings yet

- FPGADocument122 pagesFPGANishit Gupta100% (2)

- CSM51A W17 SyllabusDocument1 pageCSM51A W17 SyllabusSriramNo ratings yet

- 555 Timer Monostable OperationDocument13 pages555 Timer Monostable OperationGrigore ManNo ratings yet

- Vlsiguru DFT Training Edt Insertion Lab ObservationsDocument12 pagesVlsiguru DFT Training Edt Insertion Lab ObservationssenthilkumarNo ratings yet

- TLC5615 Schematic DiagramDocument2 pagesTLC5615 Schematic DiagramMuhammad Ahsan AkramNo ratings yet

- Bm94801kut Audio SOC in Panasonic Audio MicrosistemDocument379 pagesBm94801kut Audio SOC in Panasonic Audio MicrosistemNataLeeNo ratings yet

- Verilog ReferenceDocument77 pagesVerilog ReferencePRANJAL SHRIVASTAVANo ratings yet

- EE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduDocument18 pagesEE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduPhạm Đức ThuậnNo ratings yet

- Embedded Software Design & FPGAs 2022Document28 pagesEmbedded Software Design & FPGAs 2022Alex PérezNo ratings yet

- W. Gayler - The Apple II Circuit DescriptionDocument219 pagesW. Gayler - The Apple II Circuit DescriptionJuan Carlos ZavalaNo ratings yet

- Avr MicrocontrollerDocument21 pagesAvr MicrocontrollerRohit KanyalNo ratings yet

- Taller Chapter 16 PDFDocument2 pagesTaller Chapter 16 PDFManuel ZuñiigaNo ratings yet

A Review Report On Multi-Voltage Rule Check - HBRP Publication

A Review Report On Multi-Voltage Rule Check - HBRP Publication

Uploaded by

Saisantosh RajputhOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

A Review Report On Multi-Voltage Rule Check - HBRP Publication

A Review Report On Multi-Voltage Rule Check - HBRP Publication

Uploaded by

Saisantosh RajputhCopyright:

Available Formats

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

A Review Report on Multi-Voltage Rule Check and Formal

Verification of ASIC design

Mythili M.1*, Sujata D Badiger2, Jayati Singh3, Venkata Rangam Totakura4

1

Student, Department of Electronics and Communication, RV College of Engineering,

Bengaluru, Karnataka, India

2

Assistant Professor, Department of Electronics and Communication, RV College of

Engineering, Bengaluru, Karnataka, India

3,4

Cypress – an Infineon technologies company, Bengaluru-93, Karnataka, India

*Corresponding Author

E-Mail Id: mythilim.ec16@rvce.edu.in

ABSTRACT

In order to decrease the power dissipation in ASIC design, Multi-voltage design techniques

such as Power gating, Clock gating, Power down mode, Multi-threshold, etc. are employed.

To help designers verify the correct implementation of these low power design techniques,

Multi-voltage Rule Check is used. The implementation of different Multi-voltage design

elements such as Isolation Cell, Level Shifter Cell, Retention Cell and power aware design is

explained using Unified power format (UPF). And in the design process from Register-

transfer level (RTL) to Graphic Database System (GDSII) various changes are made to the

netlist to make it easily testable, to satisfy the timing constraints, to optimally place and route

the design. These processes introduce variations in the netlist, which must be checked to

make sure that its functionality has not changed. So Formal Verification is performed to

confirm that Golden netlist (Reference) and revised netlist are equivalent at different phases,

example Synthesis, Design for Testability (DFT), Place and route. This paper discusses the

different mathematical algorithms underlying formal Verification such as Binary decision

diagram and Satisfiability solvers. It provides a detailed review of both formal verification

and multi-voltage rule check.

Keywords: Power gating, clock gating, unified power format, binary decision diagram,

satisfiability solvers

INTRODUCTION the process technology decreases below

With the increase in the development of 90nm the sub threshold leakage increases

portable devices, the low power designing which lead to power dissipation even when

of circuit is becoming one of the most there is no switching activity in the gates

important domains in VLSI. Since the [19]. Hence the modern chip designs not

battery usage must be as minimal as only focus on satisfying the functionality

possible, several techniques are being of the intended specification but also put a

implemented in the chip design to reduce huge effort on power reduction. It employs

power consumption. The total power various techniques such as having multiple

dissipation in CMOS circuits can be power domains according to the power

divided into static and dynamic power requirement, unlike the traditional designs

dissipation. The static power dissipation is where the entire chip had a single power

due to subthreshold conduction, reverse domain. Clock gating is used to turn-off

bias leakage and tunneling current. And the clock switching when the device is not

dynamic power consumption is mainly due in use, Multi-threshold voltage cells are

to switching and short-circuits power. As used to reduce static power, etc. But the

HBRP Publication Page 1-11 2020. All Rights Reserved Page 1

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

main thing to be noted is that all these are are added, and optimizations are

additional methods should not affect the performed in order to reduce area, power

original intended functionality of the and delay. Formal verification plays an

design. And in order to make sure this, the important role in making sure the

Multi-Voltage rule check (MVRC) is used. functionality of the design is not changing

It checks for all the power related issues in after each stage from RTL to GDSII. The

the design and reports them, so that the traditional way of performing this

designer can add suitable cells to verification was simulation, where a set of

overcome this or the design will be input vectors are applied and the outputs

tweaked accordingly to ensure that the data were checked against the expected results.

integrity is maintained. There are various But as input size increases the number of

tools available in the market to perform testcases to be verified will also increase

MVRC and FV as shown in Table-1, this exponentially and after a point it becomes

paper discusses about the Cadence practically impossible within a given time

Conformal tool. to verify the entire design. And the

testcases applied may not completely

Table 1: Different EDA Tools for FV and cover all the possibilities. There is a

MVRC. famous case of Intel Pentium FDIV where

EDA Formal MVRC after the chip was released, a bug was

TOOLS Verification found in the floating-point unit, because of

Cadence Conformal Conformal which it was giving incorrect results after a

LEC Low Power few decimal places for division. Since this

Synopsys Formality Eclypse was a very rare case, it was missed during

Mentor Formal Pro the verification.

Graphics

BACKGROUND

Formal verification (FV) is another Power Dissipation in CMOS

process used to perform the equivalence The total power dissipation in CMOS

check between two netlists at different circuits can be divided into static and

stage in ASIC design flow. The RTL code dynamic power.

in Verilog or VHDL format is converted to

gate level net list after synthesis; in this Static power

conversion, the actual human It is dissipated even when there is no clock

understandable code is converted into signal applied. It is due to the following

logic gates and optimizations are factors:

performed on the netlist. In the DFT 1. Subthreshold conduction: If the input

(Design for Testability) stage, extra logic voltage of a transistor is less than the

is inserted into the netlist to make the threshold, ideally there should not be

design testable; various operations any drain current, but due to

performed are scan chain insertion and subthreshold conduction of transistors,

built in self-test etc. After fabrication there there will be some leakage current [9].

could be some defect in silicon, the DFT 2. Reverse bias leakage: In CMOS

logic helps in identifying these defects at circuits, at the junction between the

the post-silicon test. In the next stage the diffusion and well, reverse biased

DFT netlist is placed and routed, the clock diodes are formed, and this constitutes

network is built; buffer/inverters are added to reverse biased leakage current.

to satisfy timing constrains [6]. As it can 3. Tunneling Current: As the size of the

be seen, the netlist at the end of each stage MOSFET is made smaller in order to

has some modifications, a few components reduce area, the thickness of the oxide

HBRP Publication Page 1-11 2020. All Rights Reserved Page 2

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

is also reduced and when this due to the quadratic dependency of leakage

dielectric layer is reduced beyond a power on total number of transistors, it

certain point it will increase the makes reducing the leakage current as an

probability of electrons tunneling from important objective. With every 10°C rise

gate to the channel due to Quantum in temperature of high-power devices, the

mechanical effects. This process is silicon failure rate is doubling, which

called Gate tunneling. prioritizes the power reduction of deep

submicron nodes and nanometer

Dynamic power technologies [8].

It is constituted by the following factors:

1. Switching Power: It is due to the net From the view of power management, the

capacitance at the load of a gate. low power circuit consists of three

Hence higher the load or if the components they are: the design which is

switching activity is more, dynamic divided into various power domains, the

power will be high; that is the power control circuitry containing level

capacitor will get charged and shifter cells, retention cells, isolation cells.

discharged quickly. Without switching And the power control logic [13].

there is no dynamic power, but static

power still exists. Low Power techniques

2. Short Circuit Power: During switching The various low power design techniques

an instantaneous short-circuits is implemented in the design for power

formed between the supply and the reduction are:

ground, as both pMOS and nMOS are

ON, this gives rise to short circuit Clock gating

power [8]. The distribution networks of clock

contribute to around 50 percent of dynamic

The total power dissipation is the amount power consumed. The clock buffers have

of leakage and dynamic power. high switching rate and require larger

Total Power = Pleakage + Pswitching + Pshort- driving strength in order to minimize the

circuit clock delay [4]. This clock signal can be

Pleakage is a function of {VDD , Vth , W/L}, disable when not required by clock gating;

Since ,

and Pshort-circuit = ISC * VDD * f, where Ceff and if the switching frequency that is * f

is the effective capacitance, VDD is the is reduced, this will significantly reduce

supply voltage, is the switching activity, the switching power.

f is switching frequency and ISC is the

short-circuit current. Multi Vt

In this technique MOSFETs with higher

As technology progresses, the linear threshold voltages are be used, in order to

dimension of the design is scaled usually reduce the sub-threshold conduction

by a factor of 0.7, since that factor will (Pstatic). But its drawback is that the

reduce the chip area by approximately half transistor will take more time to turn ON.

of its original size [12]. As the process Hence in blocks where performance

technology decreases below 100nm, the matters the most, low Vt or normal Vt cells

contribution of leakage power also are used.

increases along with switching power.

According to reports, around 40 percent of Multi VDD

the total power is constituted by leakage Since all the power domains does not

power at 65nm technology node [1]. And require the same supply voltage,

HBRP Publication Page 1-11 2020. All Rights Reserved Page 3

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

depending on the power requirement the But in this case an isolation cell must be

supply voltage can be reduced, where inserted if the block turned off is a driver

some blocks use low power, and some be of some other block.

completely shut off depending on the

mode of operation. Using multiple voltage Some or all the above discussed techniques

domains will reduce dynamic voltage. And are implemented in a design to minimize

if two different power domains must the power consumption, but at the same

communicate then level shifter cells are time it is crucial to verify the working of

used between them to preserve the data the design and if it is performing in the

integrity. intended way and that the data is not

getting corrupted due to any of this low

Dynamic voltage scaling power techniques. To verify this Multi-

It is a technique by which, the chip can voltage rule check is needed where

change its power supply value depending additional cells are added for proper

upon the required performance, such as functionality.

sleep mode, standby mode, full power or

overdrive mode. This will reduce the METHODOLOGY

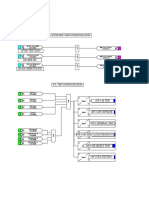

dynamic power consumption. The flowchart in Figure 1 is the ASIC

design flow from RTL to GDSII; it shows

Power gating the different stages where MVRC and

If the power is not required to a particular Formal verification are performed on the

block, then it is turned off using switching design.

cells and this reduces the static power [2].

Fig. 1: ASIC Design Flow Showing FV and MVRC.

HBRP Publication Page 1-11 2020. All Rights Reserved Page 4

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

Concepts of Multi-Voltage Rule Check Format (CPF) or Unified Power Format

Unified power format (UPF) (UPF), which describes the power

The power management techniques can be structure of the design; CPF is a standard

implemented at various levels of adopted by Silicon Integration Initiative

abstraction from system-level to register [5]. UPF is an IEEE standard from

level or transistor level. A greater power Accellera; it provides a universal format

saving can be attained at higher level as for specifying a design’s power intent

the main choices regarding timing, area easily in one place for many elements in

and power are done at higher abstraction the design [4].

[15]. The amount of power that can be The goals of UPF are to:

saved decreases from system-level design Capture power intent early in the

to transistor level. Hence to achieve design flow, during RTL development

maximum power saving the power intent Implement power intent consistently

must be combined with the logic at the throughout the flow

system level. The power intent can be Isolate HDL from Power Intent

introduced either through Common Power

Fig. 2: UPF Flow.

UPF includes consistent semantics across sub-components, each of which can be

the design flow without being tied to one independently ON/OFF depending on the

tool or vendor. It is written in tcl, and requirement. In figure since P2 is

provides a concise and universal format transmitting data to P3, so when P2

for specifying a design’s power intent becomes OFF, the input at P3 becomes

easily in one place for many elements in undetermined (X) and it is propagated

the design. UPF file combined along with throughout the circuit. In order to prevent

the RTL is used to describe the power this Isolation cells are inserted which

intent of the design at a relatively higher retains the value of the circuit before it

level [10]. went OFF [7]. The CLP tool checks if the

Isolation cells are inserted between OFF to

Multi-voltage design elements ON paths; that is between driver and

The different Multi-Voltage design receiver, if the driver is power gated and it

elements are discussed in the following turns off when not in use, it should not

section: transmit the wrong data to the receiver. If

the isolation cell is not present in such a

Isolation (Iso) Cell path the tool will report an error.

Consider a power domain with several

HBRP Publication Page 1-11 2020. All Rights Reserved Page 5

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

Fig. 3: Inserting Isolation Cell in OFF to ON Path.

The two types of Isolation cells are: to a greater extent by removing the

Clamp 1 Isolation Cell (e.g. OR gate) redundant entries and duplicate sub-trees.

Clamp 0 Isolation Cell. (e.g. AND The BDD representation depends on the

gate). ordering of the variables, for some order

there could be more reduction in the size

Level Shifter Cell of BDD compared to others. But for a

given order of variables, the BDD has a

Level shifter cells are used if there are

unique representation. There are reduction

components with different power domains.

algorithms that can be used to reduce the

If a component with a power domain of BDD. Hence a wonderful property

0.7V must send data to a 1.0V power emerges that is, for a given Boolean

domain, the data must be shifted by the equation by restricting the global ordering

level shifter cell before transmitting in of variables that can be obtained is a

order to maintain the data integrity. It canonical representation of BDD which

basically translates values between two will always be the same and the

power domains with different operating redundancy from the truth table is

voltages; this makes sure the data integrity significantly removed. Such reduced

of the signal is maintained. Possible level BDDs are called Reduced Ordered Binary

Shifters are: Low to High, High to Low or Decision Diagram (ROBDD). An example

Both Low to high, High to low (Employed of BDD and ROBDD representation is

in a Dynamic Voltage Scaling design). shown in Figure 4 for the function

̅ ̅ . Also, every node in a

Retention Cell BDD represents some Boolean function,

Retention cell is used to store the register so it can be shared between multiple

state before power down mode. These functions and are called multi-rooted BDD

values will be restored when power is up. [17]; this will also result in reduction in

So, retention cell be always on to serve the size. They are implemented in a bottom-up

fashion by building a set of operators and

purpose. As these are always ON, it can

joining them using recursive methods.

consume power even in power down mode This helps in comparing logic

[3]. implementations [14] that are if two

functions are equivalent then they will also

Concepts of Formal Verification have the same BDD representation as

Binary decision diagram (BDD) BDDs are canonical and they have a

BDDs are data structures that provide an unique representation for a given function.

efficient way of representing the Boolean And if the functions are not logically

function. The traditional truth table method equivalent their BDDs will differ hence it

is very space consuming; it requires 2n has to be verified to check for any

(n+1) entries for n variable function. But problems.

by using BDDs this space can be reduced

HBRP Publication Page 1-11 2020. All Rights Reserved Page 6

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

Fig. 4: (a) BDD and (b) ROBDD Representation for ̅ ̅ .

Boolean satisfiability (SAT) complete problems [20]. That means it

SAT is another technique that can be used takes polynomial time to verify if the

for formal verification. The SAT problem solution is correct or not. But finding a

is to assign true/false to the literals correct solution itself will take much

(variables) such that the final output of the longer time. But that is under worst-case

Boolean function is true. If for a given condition, for a reasonably small function,

Boolean expression the output cannot be satisfiability can be proven in much lesser

made true for any combination of inputs to time. Hence divide and conquer methods

the literals, then it is unsatisfiable. SAT are used to reduce the logic into small

problems are usually represented in pieces and then solving them using SAT.

Conjunctive Normal Form (CNF), that is There are also algorithms such as the

any Boolean function written as the Davis-Putnam-Logemann-Loveland

conjunction of clauses, where each of the (DPLL) algorithm, which can reduce its

clauses is the disjunction of literals. For complexity [16].

example:

f = (x1 ∨ x2) ∧ (x2 ∨ x3) ∧ (x2 ∨ x3 ∨ x5) ∧ Cadence conformal logic equivalence

(x4 ∨ x6 ∨ x5 ) ∧ (x1 ∨ x3 ∨ x5 ∨ x2) checking (LEC)

Where ∧ represents AND, ∨ represents OR The Formal verification tool by Cadence is

and represents NOT operation. Conformal LEC. Along with equivalence

checking it can also perform Clock-

Here x1 , x2, x2 , x3, x3 , etc., are the literals. domain-crossing (CDC) checks and

And (x1 ∨ x2), (x2 ∨ x3), etc. are the verifies multi-cycle paths and false paths

clauses. [11]. It considers some components in the

design as key points and logic cones to

If somehow, all the clauses can be made as divide the entire design. It checks the

true then the function f will be true, hence logical equivalence of the netlist after each

it is satisfiable. But if f cannot be made stage by comparing it with the previous

true for any combination of true/false of stage netlist which is called Golden

the literals, then the function is (Reference) netlist. And the netlist that is

unsatisfiable. The Boolean Satisfiability is being verified is the revised netlist as

a very famous problem in computer shown in Figure 5.

science and math; it falls under the NP-

HBRP Publication Page 1-11 2020. All Rights Reserved Page 7

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

Fig. 5: Comparison between Golden and Revised Netlist.

The various steps involved in LEC are: compared and mapped.

b. Function based: The function of

Defining of key points compare points are used in golden and

The LEC tool loads the golden and revised revised design to map them.

design and finds out the key points. The

key points which are targeted are: Primary Comparison of key points

inputs, Primary outputs, D flip-flop, D The compare points are Sink points of

latches, Blackboxes, TIE-Z cells (The LEC logic cones − Primary outputs, cut gates,

tool inserts the TIE-Z cells to drive a DFFs, D-latches, and Inputs of

floating net), TIE-E cells (All the X- Blackboxes. The tool loads the reference/

assignments in the netlist are given to the original design netlist and stores it as the

TIE-E cells), CUT gates (inserted in golden design. The tool then loads the

combinational feedback loops to break new/ updated design and stores it as the

them; A combinational feedback loop is an revised design. The compare points in both

unregistered feedback loop which leads to the designs are marked. The marked

slew degradation). compared points in the revised design are

mapped with its corresponding compared

Then Logic cones are formed which is a points in the reference design. This

combinational block that is bounded by mapping step uses an algorithm which is

key points. The sink points of logic cones based on name of the compare point or the

are called as compare points and these functionality of the compare point. The

points will be used by the tool to map and mapped points are then checked for the

compare the two netlists. equivalency and the equivalent and non-

equivalent points are reported. It is

Mapping of key points important to note that only mapped points

At this stage the corresponding golden and can be compared.

revised key points are paired. Mapping can

be done based on Name or Function. It can The Cadence Conformal LEC flow mainly

be applied in both Setup and LEC modes. consists of two modes namely, Setup mode

a. Name based: The instance name of key and LEC mode as shown in Figure 6.

points in golden and revised design are

HBRP Publication Page 1-11 2020. All Rights Reserved Page 8

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

Fig. 6: Conformal LEC Flow.

The comparison report includes the Golden design or in only the Revised

following classification: design but does not affect the circuit

functionality. Example: scan_in,

Categories of mapped points scan_out

1. Equivalent: The compared points are 2. Unreachable: Key point that is not

logically equivalent. propagated to any observable point.

2. Inverted Equivalent: The compared Example: spare flops not connected,

points are logically inverted. scan flops blocked after constraining

3. Non-Equivalent: The compared points 3. Not-mapped: Key point which cannot

are not equivalent and have different be mapped because there is no

functions correspondence on the other side.

4. Abort: The compared points are not Such points may be resolved with

yet proved because of timeout or some renaming rules.

other system parameter.

RESULTS AND DISCUSSION

Categories of unmapped points BDD and SAT techniques provide a better

1. Extra: Key point that exists in only the way to perform formal verification

HBRP Publication Page 1-11 2020. All Rights Reserved Page 9

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

compared to the traditional simulation R., Holcomb, K., & Wood, T. (2013,

techniques. But the problem with BDD is March). Low power design flow based

that since they vary as the order of variable on Unified Power Format and

changes, they do not always give the Synopsys tool chain. In 2013 3rd

smallest representation. So, for a bad Interdisciplinary Engineering Design

ordering there will be exponential growth Education Conference (pp. 28-31).

in the BDD representation [18]. In order to IEEE.

overcome this, there are some algorithms 5. Mandal, S., Da Costa, A. B., Hazra,

that can select the order dynamically to A., Dasgupta, P., Naware, B.,

give a better reduction but choosing the Chunduri, R. M., & Basu, S. (2017,

order in a most efficient way is not January). Formal verification of power

possible. Hence BDD based FV can be management logic with mixed-signal

used in cases where complete coverage is domains. In 2017 30th International

required like in floating point arithmetic Conference on VLSI Design and 2017

and SAT based FV can be used in cases 16th International Conference on

where the design is larger, quick results are Embedded Systems (VLSID) (pp. 239-

required. 244). IEEE.

6. Gayathri, S., & Taranath, T. C. (2017,

CONCLUSION December). RTL synthesis of case

This paper gives a detailed literature study using design compiler. In 2017

review of Multi-voltage rule check and International Conference on

Formal verification techniques. It explains Electrical, Electronics,

the power dissipation in CMOS circuits, Communication, Computer, and

various low pow techniques, and multi- Optimization Techniques

voltage design elements such as Isolation (ICEECCOT) (pp. 1-7). IEEE.

cell, level shifter cell and retention cells. It 7. Bhatt, H., Decker, J., & Desai, H. The

discusses the need for FV, and briefs the Case for Low-Power Simulation-to-

underlying mathematics of FV that is BDD Implementation Equivalence

and SAT. It also describes steps involved Checking.

in FV with respect to the Cadence 8. Varadharajan, S. K., & Nallasamy, V.

Conformal tool. (2017, March). Low power VLSI

circuits design strategies and

REFERENCES methodologies: A literature review. In

1. Bailey, S., Chidolue, G., & Crone, A. 2017 Conference on Emerging

(2007). Low power design and Devices and Smart Systems (ICEDSS)

verification techniques. Mentor (pp. 245-251). IEEE.

Graphics, white paper. 9. Klavakolanu, S. S., Raju, M. K.,

2. Challa, N.K., Nelakuditi, & U.R. Noorbasha, F., & Kanth, B. R. (2015,

(2016). The New Era on Low Power January). A review report on low

Design and Verification Methodology. power VLSI systems analysis and

International Journal of Advances in modeling techniques. In 2015

Science Engineering and Technology, International Conference on Signal

4(3). Processing and Communication

3. Bembaron, F., Kakkar, S., Mukherjee, Engineering Systems (pp. 142-146).

R., & Srivastava, A. (2009). Low IEEE.

power verification methodology using 10. Sharafinejad, R., Alizadeh, B., &

UPF. Proc. DVCon, 228-233. Fujita, M. (2015, April). UPF-based

4. Gourisetty, V., Mahmoodi, H., formal verification of low power

Melikyan, V., Babayan, E., Goldman, techniques in modern processors. In

HBRP Publication Page 1-11 2020. All Rights Reserved Page 10

Journal of VLSI Design and its Advancement

Volume 3 Issue 2

DOI: [To be assigned]

2015 IEEE 33rd VLSI Test Symposium Telecommunications and Computer

(VTS) (pp. 1-6). IEEE. Networks (SoftCOM) (pp. 11-15).

11. Seligman, E., & Yarom, I. (2006). IEEE.

Best known methods for using 16. Prasad, M. R., Biere, A., & Gupta, A.

Cadence Conformal LEC at Intel. In (2005). A survey of recent advances in

Cadence User Conference. SAT-based formal verification.

12. Brooks, D., Bose, P., Srinivasan, V., International Journal on Software

Gschwind, M. K., Emma, P. G., & Tools for Technology Transfer, 7(2),

Rosenfield, M. G. (2003). New 156-173.

methodology for early-stage, 17. Wang, F. (2004). Formal verification

microarchitecture-level power- of timed systems: A survey and

performance analysis of perspective. Proceedings of the IEEE,

microprocessors. IBM Journal of 92(8), 1283-1305.

Research and Development, 47(5.6), 18. Xu, Z., Yan, X., Lu, Y., & Ge, H.

653-670. (2003, November). Equivalence

13. Hazra, A., Goyal, S., Dasgupta, P., & checking using independent cuts

Pal, A. (2012). Formal verification of [logic design verification]. In 2003

architectural power intent. IEEE Test Symposium (pp. 482-485). IEEE.

transactions on very large scale 19. Chandramouli, B., Tsai, H. C.,

integration (VLSI) systems, 21(1), 78- Pandey, M., Lin, C. C., & Das, M. M.

91. (2010). U.S. Patent No. 7,694,251.

14. Seligman, E., Schubert, T., & Kumar, Washington, DC: U.S. Patent and

M. A. K. (2015). Formal verification: Trademark Office.

an essential toolkit for modern VLSI 20. Goldberg, E. I., Prasad, M. R., &

design. Morgan Kaufmann. Brayton, R. K. (2001, March). Using

15. Muslim, F. B., Qamar, A., & SAT for combinational equivalence

Lavagno, L. (2015, September). Low checking. In Proceedings Design,

power methodology for an ASIC Automation and Test in Europe.

design flow based on high-level Conference and Exhibition 2001 (pp.

synthesis. In 2015 23rd International 114-121). IEEE.

Conference on Software,

HBRP Publication Page 1-11 2020. All Rights Reserved Page 11

You might also like

- TC1767 Microcontroller Manual PDFDocument1,892 pagesTC1767 Microcontroller Manual PDFpierpaolo aldrigo100% (1)

- CMOS C35 Design RulesDocument60 pagesCMOS C35 Design RulesFernando Sánchez HernándezNo ratings yet

- Power Gating - Power Management Technique: VLSI Basics and Interview QuestionsDocument12 pagesPower Gating - Power Management Technique: VLSI Basics and Interview QuestionsRohith RajNo ratings yet

- Survey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyDocument15 pagesSurvey On Power Optimization Techniques For Low Power Vlsi Circuit in Deep Submicron TechnologyAnonymous e4UpOQEPNo ratings yet

- Design Stratigies of Low Power Voltage Level Shifter Circuits For Multi Supply SystemsDocument6 pagesDesign Stratigies of Low Power Voltage Level Shifter Circuits For Multi Supply SystemsIRJMETS JOURNALNo ratings yet

- IJETR032239Document5 pagesIJETR032239erpublicationNo ratings yet

- Design and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueDocument7 pagesDesign and Analysis of Different Circuits Using DCVSL & Static CMOS TechniqueGRD JournalsNo ratings yet

- Review Article: Device and Circuit Design Challenges in The Digital Subthreshold Region For Ultralow-Power ApplicationsDocument16 pagesReview Article: Device and Circuit Design Challenges in The Digital Subthreshold Region For Ultralow-Power ApplicationsFemin VargheseNo ratings yet

- A Review of Low Power Processor DesignDocument10 pagesA Review of Low Power Processor DesignNalini RadhakrishnanNo ratings yet

- A Distributed Filter Within A Switching Converter For Application To 3-D Integrated CircuitsDocument11 pagesA Distributed Filter Within A Switching Converter For Application To 3-D Integrated CircuitsDaniel zanelattoNo ratings yet

- Leakage Power Reduction and Power Delay Product (PDP) Improvement Using Dual Stack MethodDocument9 pagesLeakage Power Reduction and Power Delay Product (PDP) Improvement Using Dual Stack MethoderpublicationNo ratings yet

- Power Analysis in Vlsi Designs: Electronics and Communication Engineering. Dronacharya College of Engineering, GurgaonDocument2 pagesPower Analysis in Vlsi Designs: Electronics and Communication Engineering. Dronacharya College of Engineering, GurgaonSudhanshu ShekharNo ratings yet

- VLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)Document3 pagesVLSI Design Fault Tolerant Network On Chip: IPASJ International Journal of Electronics & Communication (IIJEC)IPASJNo ratings yet

- Low Power VLSI Design Methodologies & Power ManagementDocument4 pagesLow Power VLSI Design Methodologies & Power ManagementGeetha Rani NNo ratings yet

- TP LeakagePowerOptimizationFlowDocument11 pagesTP LeakagePowerOptimizationFlowSathyanarayana RaoNo ratings yet

- Power Optimization For Low Power VLSI CircuitsDocument4 pagesPower Optimization For Low Power VLSI CircuitsCHARANNo ratings yet

- FORTRAN Based ApproachDocument22 pagesFORTRAN Based ApproachGS EKTANo ratings yet

- Analysis of Power Dissipation and Low PoDocument9 pagesAnalysis of Power Dissipation and Low PoClementeNo ratings yet

- DSP Based Control of Interleaved Boost ConverterDocument11 pagesDSP Based Control of Interleaved Boost ConverterDany ApablazaNo ratings yet

- Low Power Techniques For VLSI DesignDocument6 pagesLow Power Techniques For VLSI DesignjainatinNo ratings yet

- Bypassing Multiplier Design Techniques For Detecting Aging EffectDocument5 pagesBypassing Multiplier Design Techniques For Detecting Aging EffectInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorKiran KNo ratings yet

- Mixed-Signal IP Design Challenges in 28 NM and BeyondDocument14 pagesMixed-Signal IP Design Challenges in 28 NM and BeyondyvarshneyNo ratings yet

- An On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SDocument7 pagesAn On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SBhaskar YalamoluNo ratings yet

- A Review of Low Power Processor DesignDocument9 pagesA Review of Low Power Processor DesignNalini RadhakrishnanNo ratings yet

- AnnepuBaburao TSrinivasaRao 62Document5 pagesAnnepuBaburao TSrinivasaRao 62Ahmed HussainNo ratings yet

- Low PowerDocument48 pagesLow PowerRákêsh Råkêë100% (1)

- Design of A Novel Energy Efficient Double Tail Dynamic ComparatorDocument5 pagesDesign of A Novel Energy Efficient Double Tail Dynamic ComparatorerpublicationNo ratings yet

- Low Power Vlsi Design1Document23 pagesLow Power Vlsi Design1Shruthi GourishettiNo ratings yet

- Low-Power Circuits Using Dynamic Threshold DevicesDocument5 pagesLow-Power Circuits Using Dynamic Threshold DevicesGiang Nguyễn VănNo ratings yet

- ME Notes Unit 4 Part 3 Low Power IC and RFICsDocument5 pagesME Notes Unit 4 Part 3 Low Power IC and RFICssayan.transcuratorsNo ratings yet

- SCE 100nmDocument48 pagesSCE 100nmGoogle acntNo ratings yet

- A 09-V Input Discontinuous-Conduction-Mode Boost CDocument12 pagesA 09-V Input Discontinuous-Conduction-Mode Boost CDanial RazaNo ratings yet

- Design of Low Power and High Speed Components of SAR ADCDocument6 pagesDesign of Low Power and High Speed Components of SAR ADCSuraj Kumar PrustyNo ratings yet

- Effect of Process, Voltage and Temperature (PVT) Variations in LECTOR-B (Leakage Reduction Technique) at 70 NM Technology NodeDocument7 pagesEffect of Process, Voltage and Temperature (PVT) Variations in LECTOR-B (Leakage Reduction Technique) at 70 NM Technology NodeDiana MaldonadoNo ratings yet

- Low-Power Digital VLSI DesignDocument530 pagesLow-Power Digital VLSI DesignAllanki Sanyasi Rao50% (2)

- Modified Gdi Technique - A Power Efficient Method For Digital Circuit DesignDocument23 pagesModified Gdi Technique - A Power Efficient Method For Digital Circuit DesignswathiNo ratings yet

- Development of A Smart LED Lighting System: Rapid Prototyping ScenarioDocument6 pagesDevelopment of A Smart LED Lighting System: Rapid Prototyping ScenariocarlosNo ratings yet

- Low Power Vlsi ThesisDocument5 pagesLow Power Vlsi Thesismariapadillaomaha100% (2)

- D Flip FlopDocument5 pagesD Flip FlopNaveen Kumar RavillaNo ratings yet

- Column Bypassing Multiplier Implementation On FPGADocument17 pagesColumn Bypassing Multiplier Implementation On FPGAIJRASETPublicationsNo ratings yet

- Thesis FinalDocument75 pagesThesis FinalSHARIZA DAYANA RODRIGUEZ URRESTANo ratings yet

- Power Management and Delivery For High-Performance MicroprocessorsDocument4 pagesPower Management and Delivery For High-Performance Microprocessorsrizal iskandarNo ratings yet

- Kinget Matching OffsetDocument14 pagesKinget Matching OffsetMikeNo ratings yet

- Review Paper On Low Power VLSI Design Techniques: Neha Thakur, Deepak KumarDocument5 pagesReview Paper On Low Power VLSI Design Techniques: Neha Thakur, Deepak Kumarhamza shahbazNo ratings yet

- Energy Efficient CMOS Microprocessor DesignDocument10 pagesEnergy Efficient CMOS Microprocessor Designnew accNo ratings yet

- Efficient Design of 1Document7 pagesEfficient Design of 1sumathiNo ratings yet

- A 45 NM Resilient Microprocessor Core For Dynamic Variation ToleranceDocument15 pagesA 45 NM Resilient Microprocessor Core For Dynamic Variation ToleranceNguyen Van ToanNo ratings yet

- Cmos Low PowerDocument5 pagesCmos Low PowerbhoomikachawlaNo ratings yet

- On Interaction Between Internal ConverteDocument7 pagesOn Interaction Between Internal ConverteDalm DuduNo ratings yet

- A Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferDocument5 pagesA Wide Range Level Shifter Using A Self Biased Cascode Current Mirror With PTL Based BufferRaja PosupoNo ratings yet

- Signal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhuDocument8 pagesSignal Integrity Analysis in PCB For High Speed Digital Circuit Design T.S. Srinivasan, J. Uma, V. PrabhusalehNo ratings yet

- Dynamic Voltage (IR) Drop Analysis and Design Closure: Issues and ChallengesDocument7 pagesDynamic Voltage (IR) Drop Analysis and Design Closure: Issues and ChallengesRohit KatkarNo ratings yet

- Design & Analysis of Different Types of Sleepy Methods For Future TechnologiesDocument6 pagesDesign & Analysis of Different Types of Sleepy Methods For Future TechnologiesseventhsensegroupNo ratings yet

- 4 Bit Johnson CounterDocument6 pages4 Bit Johnson CountermahimaNo ratings yet

- Dynamic Voltage DropDocument7 pagesDynamic Voltage DropBaluvu Jagadish100% (1)

- Tunnel Fets For Ultra-Low Voltage Digital Vlsi Circuits: Part Ii-Evaluation at Circuit Level and Design PerspectivesDocument14 pagesTunnel Fets For Ultra-Low Voltage Digital Vlsi Circuits: Part Ii-Evaluation at Circuit Level and Design PerspectivesBappy DebnathNo ratings yet

- ECEG-4281-MDC-Lec 01 Fundamentals of MicroelectronicsDocument38 pagesECEG-4281-MDC-Lec 01 Fundamentals of MicroelectronicserenaNo ratings yet

- En - Steval-Strkt01 SchematicDocument7 pagesEn - Steval-Strkt01 SchematicGael Marciano RodríguezNo ratings yet

- Using Clcs in Real-Time Applications: Wwwproducts/En/Pic18F47Q10Document41 pagesUsing Clcs in Real-Time Applications: Wwwproducts/En/Pic18F47Q10Bruno LeppeNo ratings yet

- Using In-System Programming in Boundary-Scan Systems: TAP TimingDocument8 pagesUsing In-System Programming in Boundary-Scan Systems: TAP TimingNandhini IlangovanNo ratings yet

- EEE Software Lab Report On PspiceDocument9 pagesEEE Software Lab Report On PspiceSayem Mahmud (Sym)No ratings yet

- Comparison of I C Logic FamiliesDocument2 pagesComparison of I C Logic FamiliesVinod kumarNo ratings yet

- Mentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowDocument7 pagesMentor Graphics Tutorial - From VHDL To Silicon Layout Design FlowbipbulNo ratings yet

- ARM Introduction & ArchitectureDocument33 pagesARM Introduction & ArchitectureSanjana PulapaNo ratings yet

- Bipolar Junction Transistors (BJTS) 1Document19 pagesBipolar Junction Transistors (BJTS) 1ጁንታው ነኝNo ratings yet

- Microcontroller - PPT 2. 2020Document13 pagesMicrocontroller - PPT 2. 2020Irvine ChibayaNo ratings yet

- Lab 13: Binary Counter Systems:: Three Stage Ripple Counter. Down Counters. Up/Down Counters. Altera 4count SymbolDocument5 pagesLab 13: Binary Counter Systems:: Three Stage Ripple Counter. Down Counters. Up/Down Counters. Altera 4count Symbolasin12336No ratings yet

- (WWW - Entrance-Exam - Net) - Tata ELXSI Placement Sample Paper 1Document9 pages(WWW - Entrance-Exam - Net) - Tata ELXSI Placement Sample Paper 1karthikNo ratings yet

- DE LAB ManualC-18 FinalDocument85 pagesDE LAB ManualC-18 FinalBRAGPW,Karimnagar 087No ratings yet

- Micom 87L LogicDocument4 pagesMicom 87L LogictajudeenNo ratings yet

- Mobile ProcessorDocument3 pagesMobile ProcessorMohamd barcaNo ratings yet

- FPGADocument122 pagesFPGANishit Gupta100% (2)

- CSM51A W17 SyllabusDocument1 pageCSM51A W17 SyllabusSriramNo ratings yet

- 555 Timer Monostable OperationDocument13 pages555 Timer Monostable OperationGrigore ManNo ratings yet

- Vlsiguru DFT Training Edt Insertion Lab ObservationsDocument12 pagesVlsiguru DFT Training Edt Insertion Lab ObservationssenthilkumarNo ratings yet

- TLC5615 Schematic DiagramDocument2 pagesTLC5615 Schematic DiagramMuhammad Ahsan AkramNo ratings yet

- Bm94801kut Audio SOC in Panasonic Audio MicrosistemDocument379 pagesBm94801kut Audio SOC in Panasonic Audio MicrosistemNataLeeNo ratings yet

- Verilog ReferenceDocument77 pagesVerilog ReferencePRANJAL SHRIVASTAVANo ratings yet

- EE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduDocument18 pagesEE 466/586 VLSI Design: School of EECS Washington State University Pande@eecs - Wsu.eduPhạm Đức ThuậnNo ratings yet

- Embedded Software Design & FPGAs 2022Document28 pagesEmbedded Software Design & FPGAs 2022Alex PérezNo ratings yet

- W. Gayler - The Apple II Circuit DescriptionDocument219 pagesW. Gayler - The Apple II Circuit DescriptionJuan Carlos ZavalaNo ratings yet

- Avr MicrocontrollerDocument21 pagesAvr MicrocontrollerRohit KanyalNo ratings yet

- Taller Chapter 16 PDFDocument2 pagesTaller Chapter 16 PDFManuel ZuñiigaNo ratings yet