Professional Documents

Culture Documents

QB - Unit 5 - 22MT4201 Processor and Controller

QB - Unit 5 - 22MT4201 Processor and Controller

Uploaded by

R.MADHU SUDHANAN HICET STAFF EIEOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

QB - Unit 5 - 22MT4201 Processor and Controller

QB - Unit 5 - 22MT4201 Processor and Controller

Uploaded by

R.MADHU SUDHANAN HICET STAFF EIECopyright:

Available Formats

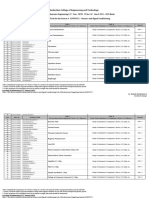

Hindusthan College of Engineering And Technology

Approved by AICTE, New Delhi, Accredited with ‘A++’ Grade by NAAC

(An Autonomous Institution, Affiliated to Anna University, Chennai)

Coimbatore – 641 032, www.hicet.ac.in | https://hindusthan.net/hicet

Phone : 0422-2611833/44 | Fax : 0422-2611855

COURSE CODE & COURSE NAME :: 22MT4201&Processor and Controller

SEMESTER -FOURTH

QUESTION BANK (With Answer Reference)

UNIT – V ::ASSEMBLY LANGUAGE PROGRAMMING

Unit # 5::I/O Port Programming - Timer Programming - Counter Programming – Serial

Communication Programming –Interrupt Programming

E-Book #

T1- A. NagoorKani, ―Microprocessors & Microcontrollers, 2nd Edition, Tata McGraw Hill

Publishing Company Limited,NewDelhi,2012.

PART A (2 Mark)

[Book T1/T2/R1]

(Page No. P.)

S.No Questions BTL Marks

{Figure / Table No

F/ T # }

What is a subroutine? What are the advantages of subroutine? R 2 [T1]

1.

(P-8.195)

2. Make a comparison between ‘Procedure’ and ‘Macro’ R 2 [T1]

(P-8.16)

Table # 8.4

3. What is data transfer scheme and what are its types? R 2 [T1]

(P-9.107)

4. What is a synchronous data transfer scheme? What is an R 2 [T1]

asynchronous data transfer scheme? (P-9.108)

5. What are the internal devices of 8255? What are the operating R 2 [T1]

modes of port-A of an 8255? (P-9.108)

6. What is USART? What are functions performed by INTEL 8251A? R 2 [T1]

(P-9.110)

7. What are the operating modes of a timer 8254? R 2 [T1]

(P-9.112)

8. What is the function of GATE signal in timer 8254? R 2 [T1]

(P-9.112)

PART B (14 Mark)

S.No Questions BTL Marks [Book T1/T2]

(Page No. P.)

{Figure / Table No

F/ T #}

i. Enumerate on the various assembly language program

9. development tools ie., Editor, Assembler, Library builder, U 14 [T1]

Linker, Debugger and simulator. (P-8.3 to 8.8 )

ii. Elaborate on the development process of an assembly {F#8.3}

language program with a flowchart.

i. Explain the pin description of INTEL-8255 Programmable

10. Peripheral Interface with neat sketch also elaborate it with U 14 [T1]

internal block diagram. (P-9.12 to )

ii. Draw and explain the schematic diagram of interfacing {F#9.15, 9.16 & 9.17}

8255 with 8085 Processor. Tabulate IO addresses of 8255A {Table #9.4 }

Explain the pin description of USART-8251A with neat [T1]

11. sketch also elaborate it with a functional block diagram. U 14 (P-9.53 to 9.56)

{F# 9.45 & 9.46}

12. i. Illustrate programming Format of 8251A mode, command [T1]

and status words. U 14 (P-9.56 to 9.60)

ii. Explain interfacing of 8251A to 8085 microprocessor with a {F# 9.47, 9.48 & 9.50}

schematic diagram. {Table #9.19}

iii. Enumerate serial communication using 8051 microcontroller.

13. i. Explain the features and pin details of Programmable [T1]

Timer - INTEL 8254. U 14 (P-9.79 to 9.82)

ii. Explain the 8254 Programmable Timer with its functional {F#9.68, 9.69 & 9.70 }

block diagram. {Table #9.68 }

14. i. Explain Control word and status word of 8254 timer? [T1]

ii. Illustrate the six operating modes of 8254 with necessary U 14 (P-9.83 to )

timing diagram. {F#9.72, 9.73, 9.74,

9.75, 9.76, 9.77, 9.78,

9.79 & 9.80 }

15. i. Explain the features and pin details of Programmable [T1]

Interrupt Controller- INTEL 8259. U 14 (P-7.16 to 7.18 )

ii. Draw the schematic diagram showing the way 8085 {F#7.6, 7.7 }

interfaced with 8259 {Table # 7.5}

16. i. Explain the 8259 Programmable Interrupt Controller with [T1]

its functional block diagram. U 14 (P-7.19 to 7.27)

ii. Describe processing and programming of Interrupts by {F#7.9,7.11, 7.13 &

8259 in 8085 with a flow chart also show the format of 7.12 }

ICWs & OCWs. {Table # 7.7}

PART C (10 Mark)

17. i. Draw and explain the schematic diagram of interfacing [T1]

8255 with 8051 microcontroller with allotted address. (P-9.17 to 9.21 )

ii. Explain 8255 Handshake input port (Mode-1), Handshake Ap 10 {F#9.19, 9.23, 9.24 &

output port (Mode-1) and Bidirectional Port (Mode-2) with 9.25 }

neat figures {Table #9.6 }

Faculty in Charge HoD

Dr.Madhusudhanan.R Dr.P.T.Saravanakumar

You might also like

- PLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingFrom EverandPLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingRating: 4 out of 5 stars4/5 (11)

- Ils Cat II-III ChecksDocument2 pagesIls Cat II-III ChecksEnrique Corvalán HernándezNo ratings yet

- QB - Unit 5 - 22MT4201 # Processor and ControllerDocument3 pagesQB - Unit 5 - 22MT4201 # Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 2 - 22MT4201 # Processor and ControllerDocument3 pagesQB - Unit 2 - 22MT4201 # Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 4 - 22MT4201 Processor and ControllerDocument2 pagesQB - Unit 4 - 22MT4201 Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 3 - 21MT6204 # Brain Computer Interface and Its ApplicationsDocument3 pagesQB - Unit 3 - 21MT6204 # Brain Computer Interface and Its ApplicationsR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 3 - 22MT4201 Processor and ControllerDocument3 pagesQB - Unit 3 - 22MT4201 Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 3 - 22MT4201 # Processor and ControllerDocument3 pagesQB - Unit 3 - 22MT4201 # Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- MPMC CP FinalDocument9 pagesMPMC CP Finalsimman8371029No ratings yet

- Alp Sol BankDocument58 pagesAlp Sol BankABOUBACAR TRAORENo ratings yet

- MP (5th) May2019Document2 pagesMP (5th) May2019monikasadwal11No ratings yet

- Department of Electronics and Communication Engineering Course DescriptionDocument7 pagesDepartment of Electronics and Communication Engineering Course DescriptionDurga SravanthiNo ratings yet

- Ec6504 MPMC QBDocument8 pagesEc6504 MPMC QBAJ ADNo ratings yet

- Question Paper Code: 13881: Reg. NoDocument4 pagesQuestion Paper Code: 13881: Reg. NoNisha JagdishNo ratings yet

- 1415 Sem 2Document7 pages1415 Sem 2anson232323No ratings yet

- MPMC Model I QPDocument2 pagesMPMC Model I QPSurendar PNo ratings yet

- Microprocessor& Micro ControllerDocument3 pagesMicroprocessor& Micro ControllersujithNo ratings yet

- 15A04407 Microprocessors & InterfacingDocument1 page15A04407 Microprocessors & InterfacingjravieceNo ratings yet

- PLC & Scada - Be - Unit Wise - All New - 2015 PatDocument20 pagesPLC & Scada - Be - Unit Wise - All New - 2015 PatSAHILNo ratings yet

- Micro 2015-2023Document13 pagesMicro 2015-2023AbhishekNo ratings yet

- 3C.Embedded Systems-1Document22 pages3C.Embedded Systems-1jeelankhader1No ratings yet

- Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesLesson Plan Microprocessor and Micro COntrollerRaja Pirian0% (2)

- Up & Uc - LessonPlanDocument2 pagesUp & Uc - LessonPlanKannan AlagumuthiahNo ratings yet

- Mapper 34R1 Manual CardDocument10 pagesMapper 34R1 Manual CardskorlipaNo ratings yet

- RP Tip Print NewDocument5 pagesRP Tip Print NewNishant RajNo ratings yet

- SESSION: 2016 - 2017 (Spring) B. Tech. 3 Year Subject Code: EE 342 Subject Name: No. of Pages: 1 (Both Side) Full Marks: 30 Duration: 2 HoursDocument2 pagesSESSION: 2016 - 2017 (Spring) B. Tech. 3 Year Subject Code: EE 342 Subject Name: No. of Pages: 1 (Both Side) Full Marks: 30 Duration: 2 HourshiNo ratings yet

- MPMC University Questions PDFDocument22 pagesMPMC University Questions PDFRajasekar PichaimuthuNo ratings yet

- Ca 2 I MSC 8085Document1 pageCa 2 I MSC 8085Vicky VickyNo ratings yet

- Department of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravananDocument4 pagesDepartment of Electronics and Communication Engineering: Mr.K.Aanandhasaravanan AanandhasaravanansarvanmeNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)Kumarasabapathy NatarajanNo ratings yet

- EC8691 Lesson Plan Microprocessor and Micro COntrollerDocument7 pagesEC8691 Lesson Plan Microprocessor and Micro COntrollerlauro eugin brittoNo ratings yet

- Mca A0532Document2 pagesMca A0532Shishupal SinghNo ratings yet

- Mpi 34095 2020Document2 pagesMpi 34095 2020ayush bansalNo ratings yet

- QP Code: 21102170: Sexplain ShldinstructionDocument2 pagesQP Code: 21102170: Sexplain ShldinstructionSanal SanuNo ratings yet

- Digital Signal Processing Lab Record R20 (III ECE)Document78 pagesDigital Signal Processing Lab Record R20 (III ECE)goudNo ratings yet

- Transmittal List 02.12.2015Document2 pagesTransmittal List 02.12.2015myLogbook thesaturdayjulyNo ratings yet

- Aditya College of Engineering &technology: III-B.Tech: II-Sem (Document86 pagesAditya College of Engineering &technology: III-B.Tech: II-Sem (Chaitanya KaisarlaNo ratings yet

- Design of A Soft Core Processor in Fpga IJERTV12IS010057Document8 pagesDesign of A Soft Core Processor in Fpga IJERTV12IS010057Technical NoviceNo ratings yet

- Stucor QP Ee8551Document8 pagesStucor QP Ee8551NagendranNo ratings yet

- 1718 Sem 3Document6 pages1718 Sem 3anson232323No ratings yet

- r05320202 Microprocessors and Micro ControllersDocument5 pagesr05320202 Microprocessors and Micro ControllersSRINIVASA RAO GANTANo ratings yet

- Sardar Raja College of Engineering Department of Electrical and Electronics Engineering Micro Lesson PlanDocument4 pagesSardar Raja College of Engineering Department of Electrical and Electronics Engineering Micro Lesson PlanKarthi SathyaNo ratings yet

- Lesson Plan CaoDocument4 pagesLesson Plan CaoPrincy UshaNo ratings yet

- Nov Dec 2019Document2 pagesNov Dec 2019ShubhamNo ratings yet

- Introduction To MicroprocessorDocument9 pagesIntroduction To MicroprocessorAman NurNo ratings yet

- Microcontrollers & Applications QBDocument7 pagesMicrocontrollers & Applications QBKeerthe VaasanNo ratings yet

- Answer All Questions, Each Carries 3 Marks: Reg No.: - NameDocument2 pagesAnswer All Questions, Each Carries 3 Marks: Reg No.: - NamelijaNo ratings yet

- Timing DiagramDocument12 pagesTiming DiagramVishal ShahNo ratings yet

- 4th Sem. / I & C Subject: Microproc. Microcontroller & Their Appl./Microproc.& App. Section-DDocument2 pages4th Sem. / I & C Subject: Microproc. Microcontroller & Their Appl./Microproc.& App. Section-Dmukulranag4No ratings yet

- MP MC Imp QuestionsDocument2 pagesMP MC Imp Questionschetanajitesh76No ratings yet

- Answer All Questions, Each Carries 3 Marks: Reg No.: - NameDocument2 pagesAnswer All Questions, Each Carries 3 Marks: Reg No.: - NameVishal KeshariNo ratings yet

- Department of Electronics and Communication Engineering: B E Degree Examination - Internal Assessment-IIDocument1 pageDepartment of Electronics and Communication Engineering: B E Degree Examination - Internal Assessment-IIvaniprabhaNo ratings yet

- Ee2354 QBDocument10 pagesEe2354 QByuvigunaNo ratings yet

- R5311901-Microprocessors and InterfacingDocument4 pagesR5311901-Microprocessors and InterfacingsivabharathamurthyNo ratings yet

- EC1301 Micro ProcessorDocument3 pagesEC1301 Micro ProcessortksctNo ratings yet

- Jntu Hyd 3 2 It Embsys Set 1Document5 pagesJntu Hyd 3 2 It Embsys Set 1Sri DNo ratings yet

- CS (Ece) (Eee) (Instr) F241 - Mpi - 2023 - 24Document3 pagesCS (Ece) (Eee) (Instr) F241 - Mpi - 2023 - 24f20212358No ratings yet

- MS BBSR T2Document3 pagesMS BBSR T2anithasancsNo ratings yet

- Microprocessors and InterfacingDocument4 pagesMicroprocessors and InterfacingVenkatesh RachaNo ratings yet

- Multicore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCFrom EverandMulticore DSP: From Algorithms to Real-time Implementation on the TMS320C66x SoCNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- 22MT4201 Processor and ControllerDocument2 pages22MT4201 Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- DAA Lab ObservationDocument49 pagesDAA Lab ObservationR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- 22cs4001 Dbms Lab ManualDocument69 pages22cs4001 Dbms Lab ManualR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- Bme 65Document8 pagesBme 65R.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- Name - List - MCT - B - Sec - 2021 - 2025 - 2nd Year - 4th - Sem - AssignmentDocument2 pagesName - List - MCT - B - Sec - 2021 - 2025 - 2nd Year - 4th - Sem - AssignmentR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- Assignment Task - 21MT4251 - SSC - MCT - B - Sec - 2021 - 2025 - 2nd Year - 4th - SemDocument3 pagesAssignment Task - 21MT4251 - SSC - MCT - B - Sec - 2021 - 2025 - 2nd Year - 4th - SemR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 3 - 22MT4201 # Processor and ControllerDocument3 pagesQB - Unit 3 - 22MT4201 # Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- QB - Unit 5 - 22MT4201 # Processor and ControllerDocument3 pagesQB - Unit 5 - 22MT4201 # Processor and ControllerR.MADHU SUDHANAN HICET STAFF EIENo ratings yet

- Bus ScheduleDocument1 pageBus SchedulerachelcanlaszapataNo ratings yet

- Creative Tim License PDFDocument3 pagesCreative Tim License PDFTeguh Belum SiapNo ratings yet

- Description Appearance: 1 Watt Metal Case Zener DiodesDocument3 pagesDescription Appearance: 1 Watt Metal Case Zener DiodesDeepa DevarajNo ratings yet

- Cisco Systems, Inc.: Implementing ERP: - Submitted by Group 2Document5 pagesCisco Systems, Inc.: Implementing ERP: - Submitted by Group 2Aditya Vidolkar100% (1)

- 14th Annual State of Agile ReportDocument19 pages14th Annual State of Agile ReportariannayamileNo ratings yet

- Republic vs. Court of Appeals: Vol. 168, November 29, 1988 77Document6 pagesRepublic vs. Court of Appeals: Vol. 168, November 29, 1988 77Joanne CamacamNo ratings yet

- Sdtechandeducation - In-Emerging Trends in Computer and Information Technology Practice MCQ Question Amp AnswerDocument16 pagesSdtechandeducation - In-Emerging Trends in Computer and Information Technology Practice MCQ Question Amp Answer09whitedevil90No ratings yet

- Tilt Up DesignDocument27 pagesTilt Up DesigntwinniesNo ratings yet

- Math 220 Final ExamDocument3 pagesMath 220 Final ExamElle Michelle YangNo ratings yet

- Amal Kumar BanerjeeDocument3 pagesAmal Kumar BanerjeeAmal Kumar BanerjeeNo ratings yet

- Lab 8Document13 pagesLab 8Tanzeela KhalidNo ratings yet

- Classification of WinesDocument3 pagesClassification of WinesRHTi BDNo ratings yet

- Weller WCB 2 Mjerac Tempearture PDFDocument1 pageWeller WCB 2 Mjerac Tempearture PDFslvidovicNo ratings yet

- Women EntrepreneursDocument27 pagesWomen Entrepreneursurvashirthr86No ratings yet

- P2141 Om 334 - R7 PDFDocument43 pagesP2141 Om 334 - R7 PDFsusheelNo ratings yet

- 01 Audi Utilises Social Media AnswersDocument3 pages01 Audi Utilises Social Media AnswersAn Thùy TrầnNo ratings yet

- WG2540 User Guide Release 2.09aDocument79 pagesWG2540 User Guide Release 2.09aMuhammad Shahroz AfzalNo ratings yet

- NAME: Jimenez, Samantha Shane O. Group # 5 DATE: July 27,2021Document6 pagesNAME: Jimenez, Samantha Shane O. Group # 5 DATE: July 27,2021Samantha JimenezNo ratings yet

- The Expansion of Economic GlobalizationDocument15 pagesThe Expansion of Economic GlobalizationRachel Demesa BadaguasNo ratings yet

- ICI Pakistan LimitedDocument74 pagesICI Pakistan LimitedZeeshan GillNo ratings yet

- Measuring Ultrasonic Velocity in Materials: Standard Practice ForDocument14 pagesMeasuring Ultrasonic Velocity in Materials: Standard Practice ForDavidMontillaNo ratings yet

- Solar Photovoltaics - Business OpportunitiesDocument17 pagesSolar Photovoltaics - Business OpportunitiesmrinalroyNo ratings yet

- Crack Width Calculation: Bending Stress Is Greater Than 130 Mpa,"hence Crack Width Caln Is RequiredDocument16 pagesCrack Width Calculation: Bending Stress Is Greater Than 130 Mpa,"hence Crack Width Caln Is RequiredAnand.5No ratings yet

- Project On Query in Ms AccessDocument36 pagesProject On Query in Ms Accessmathews johnsonNo ratings yet

- Friday, September 18, 2015 EditionDocument16 pagesFriday, September 18, 2015 EditionFrontPageAfricaNo ratings yet

- 3Q19 and 9M19 Results PresentationDocument46 pages3Q19 and 9M19 Results PresentationRoamNo ratings yet

- Overtourism Causes Implications and Solutions 1St Ed Edition Hugues Seraphin Full ChapterDocument67 pagesOvertourism Causes Implications and Solutions 1St Ed Edition Hugues Seraphin Full Chapterevelyn.kennedy635100% (6)

- Escalation and Price Indices ESB 450Document31 pagesEscalation and Price Indices ESB 450sarcozy922No ratings yet

- MB Precast Concrete Civil Engineering Feb09Document24 pagesMB Precast Concrete Civil Engineering Feb09Paulo CotteNo ratings yet