Professional Documents

Culture Documents

Synchronization

Synchronization

Uploaded by

AlexCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Synchronization

Synchronization

Uploaded by

AlexCopyright:

Available Formats

Synchronization

SRAN5.0

Feature Parameter Description

Issue 01

Date 2010-10-15

HUAWEI TECHNOLOGIES CO., LTD.

Copyright © Huawei Technologies Co., Ltd. 2011. All rights reserved.

No part of this document may be reproduced or transmitted in any form or by any means without prior

written consent of Huawei Technologies Co., Ltd.

Trademarks and Permissions

and other Huawei trademarks are trademarks of Huawei Technologies Co., Ltd.

All other trademarks and trade names mentioned in this document are the property of their respective

holders.

Notice

The purchased products, services and features are stipulated by the contract made between Huawei and

the customer. All or part of the products, services and features described in this document may not be

within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements,

information, and recommendations in this document are provided "AS IS" without warranties, guarantees or

representations of any kind, either express or implied.

The information in this document is subject to change without notice. Every effort has been made in the

preparation of this document to ensure accuracy of the contents, but all statements, information, and

recommendations in this document do not constitute the warranty of any kind, express or implied.

Huawei Technologies Co., Ltd.

Address: Huawei Industrial Base

Bantian, Longgang

Shenzhen 518129

People's Republic of China

Website: http://www.huawei.com

Email: support@huawei.com

SingleRAN

Synchronization Contents

Contents

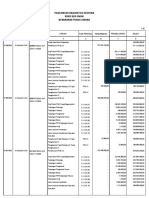

1 Introduction ................................................................................................................................1-1

1.1 Scope ............................................................................................................................................ 1-1

1.2 Intended Audience ........................................................................................................................ 1-1

1.3 Change History.............................................................................................................................. 1-1

2 Overview .....................................................................................................................................2-1

2.1 Clock Synchronization ................................................................................................................... 2-1

2.2 Time Synchronization .................................................................................................................... 2-1

2.3 Frequency Synchronization........................................................................................................... 2-2

2.4 Difference Between Time Synchronization and Frequency Synchronization ............................... 2-3

3 Synchronization Techniques .................................................................................................3-1

3.1 Main Clock Synchronization Techniques....................................................................................... 3-1

3.2 Line Clock Synchronization ........................................................................................................... 3-1

3.3 GPS Clock Synchronization .......................................................................................................... 3-1

3.3.1 Overview ............................................................................................................................... 3-1

3.3.2 Advantages and Disadvantages of GPS Clock Synchronization ......................................... 3-2

3.4 BITS Clock Synchronization.......................................................................................................... 3-2

3.4.1 Overview ............................................................................................................................... 3-2

3.4.2 BITS Clock Synchronization Solution ................................................................................... 3-3

3.4.3 Advantages and Disadvantages of BITS Clock Synchronization ......................................... 3-4

3.5 Ethernet Clock Synchronization .................................................................................................... 3-4

3.5.1 Overview ............................................................................................................................... 3-4

3.5.2 Advantages and Disadvantages of Ethernet Clock Synchronization ................................... 3-5

3.6 IEEE1588 V2 Clock Synchronization ............................................................................................ 3-5

3.6.1 Overview ............................................................................................................................... 3-5

3.6.2 Application Modes of IEEE1588 V2 Clock Synchronization ................................................. 3-5

3.6.3 Advantages and Disadvantages of IEEE1588 V2 Clock Synchronization ........................... 3-7

4 SingleRAN Clock Solutions ...................................................................................................4-1

4.1 MBSC Clock Solution .................................................................................................................... 4-1

4.1.1 Overview ............................................................................................................................... 4-1

4.1.2 Clock Sources ...................................................................................................................... 4-1

4.1.3 Structure of Clock Synchronization Subsystem ................................................................... 4-2

4.1.4 Clock Synchronization Process ............................................................................................ 4-4

4.1.5 RFN Generation and Reception ........................................................................................... 4-6

4.2 MBTS Clock Solution .................................................................................................................... 4-7

4.2.1 Overview ............................................................................................................................... 4-7

4.2.2 Clock Sources ...................................................................................................................... 4-8

4.2.3 Clock Synchronization Process ............................................................................................ 4-9

4.3 MBTS Common Clock Solution................................................................................................... 4-10

Issue 01 (2010-10-15) Huawei Proprietary and Confidential i

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization Contents

4.3.1 Overview ............................................................................................................................. 4-10

4.3.2 Common GPS Reference Clock ..........................................................................................4-11

4.3.3 Common BITS Reference Clock ........................................................................................ 4-12

4.3.4 Common E1/T1 Reference Clock......................................................................................... 4-1

4.3.5 Common IEEE1588 V2 Reference Clock............................................................................. 4-2

4.3.6 Common Synchronous Ethernet Reference Clock .............................................................. 4-4

5 Appendix Synchronization Process in the UTRAN .........................................................5-1

5.1 Overview ....................................................................................................................................... 5-1

5.2 Network Synchronization .............................................................................................................. 5-2

5.2.1 Overview ............................................................................................................................... 5-2

5.2.2 Network Synchronization Modes .......................................................................................... 5-2

5.2.3 Network Synchronization in the UTRAN .............................................................................. 5-2

5.3 Node Synchronization ................................................................................................................... 5-3

5.3.1 Overview ............................................................................................................................... 5-3

5.3.2 Node Synchronization Procedure......................................................................................... 5-3

5.4 Frame Synchronization ................................................................................................................. 5-4

5.4.1 Overview ............................................................................................................................... 5-4

5.4.2 Frame Timing Supervision .................................................................................................... 5-5

5.4.3 Frame Timing Adjustment ..................................................................................................... 5-6

5.5 Radio Interface Synchronization ................................................................................................... 5-7

5.5.1 Overview ............................................................................................................................... 5-7

5.5.2 Radio Interface Synchronization Procedure ......................................................................... 5-7

6 Parameters .................................................................................................................................6-1

7 Counters ......................................................................................................................................7-1

8 Glossary ......................................................................................................................................8-1

9 Reference Documents .............................................................................................................9-1

Issue 01 (2010-10-15) Huawei Proprietary and Confidential ii

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 1 Introduction

1 Introduction

1.1 Scope

This document describes the synchronization feature of GSM and WCDMA, consisting of the basic

principles of clock synchronization, the main clock synchronization techniques, and the SingleRAN clock

solutions. The SingleRAN clock solutions consist of the clock solution on the MBSC side, the clock

solution on the MBTS side, and the common clock solution on the MBTS side.

MBSC is a GSM+UMTS (GU) multi-mode base station controller of Huawei. In this document, the BSC refers to the

MBSC performing the functions of a GSM base station controller, the RNC refers to the MBSC performing the functions

of a UMTS base station controller.

MBTS is a GU, GSM+LTE (GL), or UMTS+LTE (UL) multi-mode base station of Huawei. In this document, the GSM

BTS refers to the MBTS performing the functions of a GSM base station, the NodeB refers to the MBTS performing the

functions of a UMTS base station, and the LTE eNodeB refers to the MBTS performing the functions of a LTE base

station.

1.2 Intended Audience

This document is intended for:

Personnel who are familiar with WCDMA and GSM basics

Personnel who need to understand the synchronization feature of the SingleRAN system

Personnel who work with Huawei products

1.3 Change History

This section provides information on the changes in different document versions.

There are two types of changes, which are defined as follows:

Feature change: refers to the change in the synchronization feature.

Editorial change: refers to the change in wording or the addition of the information that was not

described in the earlier version.

Document Issues

The document issues are as follows:

01 (2010-10-15)

Draft (2010-05-15)

01 (2010-10-15)

This is the document for the first commercial release of SRAN5.0.

Compared with issue Draft (2010-05-15) of SRAN5.0, this issue optimizes the description.

Draft (2010-05-15)

This is the draft for SRAN5.0.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 1-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 2 Overview

2 Overview

2.1 Clock Synchronization

Synchronization of clocks in the network is a critical issue for the digital communication network.

Synchronization of clocks means that the frequencies or phases of clock signals maintain a precise

relation. The purpose of synchronization is to ensure that the frequency or time difference between the

devices in a network is kept within an acceptable margin of error. This can prevent the transmission

performance in a digital communication system from deterioration, such as bit error and jitter, because

data is not correctly transmitted or received.

Clock synchronization consists of time synchronization (also known as phase synchronization) and

frequency synchronization.

The principle of clock synchronization is that a lower-level device is required to synchronize its clock with

the clock of an upper-level device. The base station controller needs to synchronize its clock with the

clock of the Core Network (CN), and the base station needs to synchronize its clock with the clock of the

base station controller.

2.2 Time Synchronization

Time signals are the clock signals used as a reference to the time of the year. It contains information

related to the year, month, day, hour, minute, and second. The time standard Coordinated Universal

Time (UTC) has been widely used in the telecom industry.

Time synchronization is the synchronization of the absolute time. Time synchronization throughout the

entire network means the synchronization of the clocks of all the devices in the network with the UTC,

that is, the start time of time signals is synchronized with the UTC. As shown in Figure 2-1, signal B is

time-synchronized with the UTC, whereas signal C and signal D are not time-synchronized with the

UTC.

Figure 2-1 Time synchronization

Phase time, also called phase, is the time delay between the actual signal and the ideal signal at a

significant instance (generally, a rising edge or a falling edge), as shown in Figure 2-2.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 2-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 2 Overview

Figure 2-2 Phase time

2.3 Frequency Synchronization

Frequency synchronization means that the frequencies of two signals change at the same rate or the

ratio of the frequency change period of one signal to that of the other is a fixed value. The phases and

frequencies of the two signals can be different. As shown in Figure 2-3, signals A, B, and C are

frequency-synchronized.

In frequency synchronization, the clock signals change periodically yet do not contain the time

information.

Figure 2-3 Frequency synchronization

Only frequency synchronization is required in GSM and WCDMA systems. The accuracy requirement is

0.05 per million (ppm).

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 2-2

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 2 Overview

2.4 Difference Between Time Synchronization and Frequency

Synchronization

Figure 2-4 Time synchronization (phase synchronization) and frequency synchronization

As shown in Figure 2-4, the difference between time synchronization and frequency synchronization is

as follows:

In phase synchronization, Watch A and Watch B always have the same time.

In frequency synchronization, Watch A and Watch B have different times, but the time difference

between the two is always the same, for example, six hours.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 2-3

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

3 Synchronization Techniques

In a traditional clock synchronization solution, PDH and SDH networks are used to provide clocks for

GSM and WCDMA systems. After all-IP evolution, IP networks replace PDH and SDH networks to

provide clocks for GSM and WCDMA systems.

3.1 Main Clock Synchronization Techniques

The main clock synchronization techniques include:

Line clock synchronization

GPS clock synchronization

BITS clock synchronization

Ethernet clock synchronization

IEEE1588 V2 clock synchronization

3.2 Line Clock Synchronization

All ports that support line clock recovery, such as STM-1, E1, and Ethernet ports, trace the uplink line

clock, perform synchronization at the physical layer, and then recover clock signals from the line code

streams. The recovered clock signals subsequently work as the reference clock of the system.

The Ethernet ports of the MBSC do not support line clock recovery.

Line clock synchronization provides a high-accuracy reference clock for the radio access network

without requiring additional equipment. Thus, the cost of network construction is greatly reduced. Line

clock is the most widely used synchronization technique.

3.3 GPS Clock Synchronization

3.3.1 Overview

The Global Positioning System (GPS) is a satellite-based navigation system provided by the United

States. It provides a high-accuracy reference clock, which can be utilized for time and frequency

synchronization.

The GPS clock synchronization solution generally uses an oven-controlled crystal oscillator (OCXO) and

the GPS satellite. On the MBSC/MBTS side, a GPS reference receiver obtains the UTC-based time from

the GPS satellite and recovers the 1PPS clock signals. The GPS reference receiver then compares the

recovered clock signals with the clock signals generated by the oscillator. Then, the clock signals are

frequency-locked and phase-locked through software to generate standard clock signals for the system.

Figure 3-1 shows the GPS clock synchronization solution.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

Figure 3-1 GPS clock synchronization solution

3.3.2 Advantages and Disadvantages of GPS Clock Synchronization

Advantages

The GPS clock synchronization solution can be used for time synchronization and frequency

synchronization.

The GPS clock synchronization solution can accurately provide the UTC-based time.

Disadvantages

The GPS clock synchronization solution requires each base station to be equipped with a GPS

reference receiver, which increases the overall CAPEX.

The GPS antenna requires the field angle of 45ºof the centrum to be clear from obstacles. Thus, the

antenna site selection becomes limited.

Feeders need to be installed between the GPS antenna and the base station. In the case of a

complicated construction venue or building, feeder installation can be difficult. In addition, feeder

installation requires the consent of both the house owners and the property management authorities,

and thus the negotiation may be challenging.

3.4 BITS Clock Synchronization

3.4.1 Overview

A Building Integrated Timing Supply (BITS) device is mainly used to synchronize the devices in a fixed

network. It is a dedicated timing signal generator in a communications building or area. A BITS device

generally provides reference clocks for switches.

A BITS device can work as the stratum-3 slave clock, stratum-2 slave clock, and stratum-1 Primary

Reference Clock (PRC)/Local Primary Reference Clock (LRP) for a digital synchronization network.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-2

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

A BITS device can synchronize its clock with the primary reference clock and provide various timing

signals for the digital devices to be synchronized. The types of reference clock of a BITS device can be

the E1 link, 10 MHz, 5 MHz, 1 MHz, or 2048 KHz.

A BITS device may have different configurations based on the importance of the site. A high-end

configuration of the BITS device is rubidium clock + GPS or OXCO + GPS. The GPS module locks the

phase and frequency of the GPS 1PPS clock signals to ensure the long-term stability of the clock. The

rubidium clock or the OXCO ensures the short-term stability of the clock. In this manner, the stability of

the clock is guaranteed.

If a BITS device is not configured with GPS + crystal oscillator, it can lock the upper-level reference clock

through an E1 link.

3.4.2 BITS Clock Synchronization Solution

Figure 3-2 BITS clock synchronization solution

BITS clocks are generally layered according to the clock quality. A clock synchronization network adopts

a top-down design and provides master and slave synchronization clocks. The clock signals in the clock

synchronization network are distributed through transmission links in a layered and hierarchical manner.

Figure 3-2 shows the BITS clock synchronization solution.

The BITS of the PRC/LPR stratum generally uses the rubidium clock + GPS satellite synchronization

mode. A cesium or hydrogen clock can be used to replace the rubidium clock.

The BITS of the Synchronization Supply Unit (SSU) stratum can be the Transmit Network Clock (TNC)

or the Local Network Clock (LNC).

− BITS of the TNC stratum uses a rubidium clock as the local clock.

− BITS of the LNC stratum uses an OXCO as the local clock.

The BITS of the SDH Equipment Clock (SEC) stratum usually uses a constant-temperature crystal

oscillator as the local clock. SEC specifies a requirement for the transmission device that carries the

source clock signals.

Transmission devices are usually deployed in ring topology. To prevent an upper-level clock device from

tracing the reference clock of a lower-level clock device in ring topology, the strata of reference clocks

are specified by the Synchronization Status Message (SSM) and are ranked in descending order of PRC,

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-3

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

TNC, LNC, and SEC. A BITS device will not choose a reference clock whose stratum is lower than the

stratum of itself.

3.4.3 Advantages and Disadvantages of BITS Clock

Synchronization

Advantages

A BITS device adopts a high-accuracy local clock and a high-reliability phase-locked algorithm.

Therefore, the clock provided by the BITS device features high accuracy and stable phase even during

the time period when the upper-level reference clock is lost. Compared with other clock synchronization

solutions, the BITS solution provides higher quality of clock for the radio access network devices.

Disadvantages

BITS clock signals are transmitted through coaxial cables or differential cables, and thus the

transmission distance is relatively short. Therefore, a BITS device provides reference clock signals only

for the communication devices in the same telecommunication equipment room.

3.5 Ethernet Clock Synchronization

3.5.1 Overview

Ethernet clock synchronization is a technique using the code streams on an Ethernet link to recover the

clock. The Ethernet physical layer (PHY) chip has the clock recovery capability. It uses the clock and

data recovery (CDR) technique to extract the clock signals from the serial code streams sent from the

transmission end.

Figure 3-3 shows the principle of extracting clock signals from Ethernet. On the transmission side, the

clock module of the system generates a high-accuracy system clock and distributes it to all the Ethernet

ports. Then, the PHY chip on the Ethernet interface board transmits the clock signals to an Ethernet port

of the MBTS through an FE/GE link. On the reception side, the PHY chip on the Ethernet interface board

of the MBTS recovers the clock signals, performs frequency division, and then distributes the clock

signals to the other modules of the MBTS.

Figure 3-3 Principle of extracting clock signals from Ethernet

The Ethernet clock synchronization technique is a type of IP network clock solution. See the IP Network

Clock Feature Parameter Description of RAN for details.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-4

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

3.5.2 Advantages and Disadvantages of Ethernet Clock

Synchronization

Advantages

This is a mature technique.

Clock signals are recovered through the physical-layer code streams. The performance of the

recovered clock is reliable, and the quality of the recovered clock is similar to the quality of the clock

transmitted on an SDH link.

The clock features high reliability and is not affected by the load fluctuation in the network.

Disadvantages

There is a restriction on the deployment of a synchronous Ethernet. Clock signals are transmitted on

links. Therefore, all the links on the clock transmission path are required to support synchronous

Ethernet in principle.

Clock extraction is not supported by all ports.

This solution does not provide time synchronization.

3.6 IEEE1588 V2 Clock Synchronization

3.6.1 Overview

IEEE1588 V2 is a precise clock synchronization protocol. It is also called the precision time protocol

(PTP). As defined by the IEEE1588 V2 protocol, IEEE 1588 messages are transmitted between the

master and slave devices to calculate the time and frequency offsets. In this manner, the time and

frequency of the master and slave devices are synchronized. Currently, Huawei devices support only

frequency synchronization using IEEE1588 V2 clock synchronization.

The IEEE1588 V2 protocol involves the following key technical points:

Best Master Clock (BMC) algorithm

The devices in the network may have different clock reference sources. Therefore, before clock

synchronization is performed, the tracing relationships of the master and slave clocks of the entire

network need to be determined. This algorithm prevents the occurrence of multiple or no master

clocks and free-run condition.

Principle of master and slave synchronization

The IEEE1588 V2 protocol adopts the handshake method and uses a precise timestamp to implement

frequency and time synchronization.

Transparent Clock (TC) model

The TC does not participate in the decision of the master and slave clocks. It only processes the delay.

When a packet is transmitted over the intermediate equipment, extra delay is generated. The TC

labels a timestamp when a packet is received and labels another timestamp when this packet is

transmitted. The time difference between the two timestamps is the time elapsed when this packet

traverses the TC.

The IEEE1588 V2 clock synchronization technique is a type of IP network clock solution and used in

Ethernet transport networks. See the IP Network Clock Feature Parameter Description of RAN for

details.

3.6.2 Application Modes of IEEE1588 V2 Clock Synchronization

The IEEE1588 V2 time synchronization solution has two application modes, as shown in Figure 3-4.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-5

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

Boundary Clock (BC) mode

An external clock device on the core network side, or a Packet Transport Network (PTN) device such

as the MBTS on the radio access network side, provides clock signals for a PTN device through a

dedicated clock port (1PPS + serial port). In this case, the MBTS does not need to support the

IEEE1588 V2 protocol.

TC mode

FE/GE ports are used to transmit clock signals. If the IEEE1588 V2 server provides time

synchronization, then all the devices on the clock transmission path are required to support the

IEEE1588 V2 protocol.

Figure 3-4 Application modes of IEEE1588 V2 time synchronization

According to the IEEE1588 V2 protocol, the clocks in the entire network are classified into TC, BC, and

Ordinary Clock (OC):

The TC is used to transparently transmit clock signals in the network. It processes the delay generated

on the path transmitting IEEE1588 V2 packets.

The BC is an intermediate clock device in the network. A BC has multiple IEEE1588 V2 ports. One

IEEE1588 V2 port of the BC works in slave mode and synchronizes the time and frequency of the

system clock with an upper-level device. Other IEEE1588 V2 ports of the BC work in master mode and

transmit synchronization information level by level.

The OC is an initial device or a terminal device. Such a device has only one IEEE1588 V2 port and

works in slave or master mode. The MBTS functions only as an OC.

The IEEE1588 V2 frequency synchronization does not require a TC or BC, as shown in Figure 3-5.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-6

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 3 Synchronization Techniques

Figure 3-5 Application modes of IEEE1588 V2 frequency synchronization

3.6.3 Advantages and Disadvantages of IEEE1588 V2 Clock

Synchronization

Advantages

The extracted clock signals are of high quality.

The IEEE1588 V2 clock synchronization solution provides time synchronization and frequency

synchronization.

IEEE1588 V2 is an open standard protocol.

The clock used in the PTN can be smoothly upgraded from a synchronous Ethernet clock to an

IEEE1588 V2 clock.

Disadvantages

The IEEE1588 V2 clock synchronization solution requires an IEEE1588 V2 server.

If an IEEE1588 V2 server provides time synchronization, all the devices on the clock transmission path

are required to support the IEEE1588 V2 protocol. Deploying devices supporting the IEEE1588 V2

protocol on a large scale in the network is challenging.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 3-7

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

4 SingleRAN Clock Solutions

This chapter describes the clock solution on the MBSC side, the clock solution on the MBTS side, and

the common clock solution on the MBTS side.

The synchronization techniques discussed in this chapter are frequency synchronization techniques.

4.1 MBSC Clock Solution

This section describes the obtainable reference clocks of the MBSC, the structure of the clock

synchronization subsystem of the MBSC, the process of clock synchronization in the MBSC, and the

RNC Frame Number (RFN) generation and reception.

This section is related to the feature MRFD-210502 BSC/RNC Clock.

4.1.1 Overview

The clock synchronization subsystem of the MBSC provides system clock for the MBSC and provides

reference clocks for base stations.

The clock synchronization subsystem of the MBSC consists of the clock board and the clock processing

units of each subrack. The clock board of the MBSC can be the GCUa or GCGa board. Users can run

the SET CLKTYPE command to set the type of a clock board.

The number of MBSCs is greater than the number of CN devices, and many MBSCs are not located in

the central telecommunications room. Therefore, an MBSC generally obtains the reference clock from

an upper-level CN device through the transmission links. The accuracy of the local clock of an MBSC is

generally 4.6 ppm.

4.1.2 Clock Sources

The MBSC can use the following reference clocks: external clocks (BITS clock and external 8 kHz clock),

line clock, GPS clock, and local oscillator.

External clocks

− BITS clock

The BITS clock signals are of three types: 2 MHz, 2 Mbit/s, and 1.5 Mbit/s. The 2 MHz and 2 Mbit/s

clock signals are E1 clock signals, and the 1.5 Mbit/s clock signals are T1 clock signals.

The BITS clock has two input modes: BITS0 and BITS1. BITS0 and BITS1 correspond to the

CLKIN0 and CLKIN1 ports on the clock board respectively. The MBSC obtains the BITS clock

signals through the CLKIN0 or CLKIN1 port.

The parameters REF2MCLKSW1 and REF2MCLKSW2 are used to enable the switch of BITS clock

on a transport interface board.

− External 8 kHz clock

Through the COM1 port on the clock board, the MBSC obtains 8 kHz standard clock signals from an

external device.

Line clock

The line clock signals are extracted from the CN by an interface board of the MPS. The line clock

signals are transmitted to the clock board through the backplane channel of the MPS. The line clock

signals are phase-locked by the clock module to generate 8 kHz clock signals.

The line clock has two input modes, LINE0 and LINE1. LINE0 and LINE1 correspond to backplane

channel 1 and backplane channel 2 respectively.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

The parameters BACK8KCLKSW1 and BACK8KCLKSW2 are used to enable the switch of the line

clock on the backplane.

GPS clock

The GPS clock provides 1PPS clock signals for the MBSC. The MBSC receives the GPS signals at

the ANT port on the GCGa board that is configured with a GPS satellite card. If the MBSC is

configured with the GCUa board that is not configured with a GPS satellite card, the GPS clock is not

applicable to the MBSC.

Local oscillator

If the MBSC fails to obtain any external clock, the MBSC obtains its working clock signals from the

local oscillator.

You can run the MML command ADD CLKSRC to configure the parameter SRCT to set the clock source

type.

The reference clock has three operating modes:

Automatic mode

Users need not specify the reference clock. The MBSC can automatically select the reference clock

with the highest priority.

Manual mode

Users need to specify the reference clock. The MBSC cannot change the reference clock even when

the current specified reference clock is faulty.

Self-oscillation mode

The self-oscillation mode is the initial operating mode of the MBSC clock.

Users can run the SET CLKMODE command to set the clock mode.

4.1.3 Structure of Clock Synchronization Subsystem

Figure 4-1 shows the structure of the clock synchronization subsystem.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-2

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-1 Structure of clock synchronization subsystem

The structure of the MBSC clock synchronization subsystem is described as follows:

If the MPS is used to extract the clock signals, the clock signals can obtained in the following ways:

− The clock signals can be obtained by the port on the panel of the clock board.

− Theclock signals can be obtained by the port on the panel of an interface board that can extract line

clock signals. The interface board then transmits the clock signals to the clock board through the

backplane.

− The clock signals can be generated by the oscillator on the clock board.

If the EPS is used to extract the clock signals, an interface board rather than an Ethernet interface

board is used to obtain the clock signals. The clock signals extracted by the EPS are transmitted to the

clock board through clock signal cables.

If the MBSC is configured with the Gb interface board, the Gb interface board extracts clock signals

from either the backplane or the CN. The Gb interface board, however, cannot extract clock signals

from them simultaneously. If the PS services and CS services use different reference clocks and the

clock signals are extracted from the CN, the Gb interface board serves only the Gb interface. If the PS

services and CS services use different reference clocks, the CS services can use the reference clock

of the PS services only when the parameter REFUSELOCALCLK is set to YES.

Figure 4-2 shows the connections of the clock signal cables between the clock boards in the MPS and

the SCUa boards in the EPS when the MBSC is configured with active and standby clock boards and

SCUa boards.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-3

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-2 Connections of clock signal cables

The active and standby clock boards in the MPS are connected to the active and standby SCUa boards

in the EPS through the Y-shaped clock signal cables. This connection mode ensures that the system

clock of the MBSC works properly in the case of a single-point failure of the clock board, Y-shaped clock

signal cable, or SCUa board. In addition, the Y-shaped clock signal cables ensure the proper working of

the SCUa boards during the switchover of the active and standby clock boards.

In the MPS, the clock board transmits clock signals to the SCUa boards through the backplane channel. Therefore, the

Y-shaped clock signal cable is not required.

4.1.4 Clock Synchronization Process

The MBSC processes external clock signals before transmitting them to the boards in the MBSC. The

clock synchronization process varies slightly from one subrack to another.

MPS/EPS Clock Synchronization Process

The clock signals of the MPS/EPS are provided by the clock board. The clock board can extract clock

signals from an external device or extract line clock signals from the Iu-CS or A interface.

Figure 4-3 shows the process of clock synchronization in the MPS/EPS when the clock board extracts

clock signals from an external device or from the GPS.

Figure 4-4 shows the process of clock synchronization in the MPS/EPS when the clock board extracts

line clock signals from the Iu-CS or A interface.

In BM/TC separated configuration mode, the TransCoder (TC) subrack extracts the line clock signals from the A interface

and then the clock board in the BM subrack extracts the clock signals from the Ater interface.

The MPS and the EPS are collectively known as Basic Module (BM) subrack, and the TCS is known as TC subrack.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-4

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-3 MPS/EPS clock synchronization (1)

Figure 4-4 MPS/EPS clock synchronization (2)

As illustrated in Figure 4-3 and Figure 4-4, the process of clock synchronization in the MPS/EPS is as

follows:

1. The clock signals are obtained from the external reference clock.

If an external clock is used, external clock signals travel to the clock board through the port on the

panel of the clock board. If the GPS clock is used, clock signals travel to the clock board through the

GPS antenna port. When the external reference clock is the line clock, the clock signals travel to the

clock board through the backplane channel after extracted by the MPS or through clock signal cables

after extracted by the EPS.

2. The reference clock is phase-locked in the clock board to generate clock signals.

3. The clock board in the MPS transmits the clock signals to the SCUa board in the MPS through the

backplane and in each EPS through the clock signal output ports on the clock board.

4. The SCUa board in the MPS/EPS transmits the clock signals to the other boards in the same subrack

through the backplane.

The clock synchronization subsystem of the MBSC transmits reference clock signals to a base station through the Iub or

Abis interface board.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-5

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

TCS Clock Synchronization Process

Figure 4-5 shows the process of clock synchronization in the TCS when the TCS extracts line clock

signals from the A interface in A over TDM mode.

Figure 4-5 TCS clock synchronization

1. The TCS extracts line clock signals from the A interface. Then, the line clock signals are processed

by the A interface board to generate the required clock signals.

2. In the TCS, the A interface board transmits the clock signals to the SCUa board through the

backplane channel. Then, the SCUa board transmits the clock signals to the other boards in the TCS.

In A over IP over Ethernet mode, the MBSC can extract only external clock signals.

In A over IP over E1/T1 mode, the MBSC can extract only line clock signals.

4.1.5 RFN Generation and Reception

RFN is used to synchronize NodeBs with the MBSC. The node synchronization frames from the MBSC

to the NodeBs carry the RFN information.

Figure 4-6 shows the process of RFN generation and reception. This figure takes the GCUa board as an

example.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-6

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-6 Process of RFN generation and reception

The clock board in the MPS sends the 1PPS signals and synchronization time packets to the SCUa

board in each subrack. The SCUa board in each subrack then transmits the 1PPS signals and

synchronization time packets to the other boards in the same subrack. The boards generate the required

RFN signals based on the received 1PPS signals and synchronization time packets. The 1PPS signals

can be generated by the clock board.

4.2 MBTS Clock Solution

This section describes the reference clocks and clock synchronization process of the MBTS.

This section is related to the feature MRFD-210501 BTS/NodeB Clock.

4.2.1 Overview

In GSM and WCDMA networks, base stations do not need to be synchronized with each other. Each

base station can obtain the reference clock from the MBSC. The clock accuracy requirement of a base

station is generally 0.05 ppm.

Clock synchronization provides the reference clock for the normal operation of the MBTS and generates

NodeB Frame Number (BFN) or GSM FN (GFN). The BFN or GFN is the basis for frame synchronization.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-7

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

The MBTS obtains the reference clock through the clock synchronization for the internal frame

synchronization.

4.2.2 Clock Sources

The MBTS can use the following reference clocks: Iub/Abis clock, GPS clock, BITS clock, IP clock, and

internal clock. Users can run the SET CLKMODE command to set the reference clock of a NodeB or the

SET BTSCLK command to set the reference clock of a BTS.

Iub/Abis Clock

The MBTS is synchronized with the line reference clock of its upper-level NE such as the MBSC.

The synchronization with the Abis clock (also known as the BSC tracing clock) can be enabled by setting

ClkType to TRCBSC_CLK, and the synchronization with the Iub clock can be enabled by setting

CLKSRC to LINE. In line clock synchronization, the MBTS receives the clock signals from an

upper-level NE through the E1/T1/Ethernet port. Clock signals must be available on the E1/T1/Ethernet

link for the MBTS to obtain the line reference clock.

GPS Clock

If there is no upper-level clock or the upper-level clock is unstable, the GPS clock can be used as the

reference clock of an MBTS.

The synchronization with the GPS clock for a BTS can be enabled by setting ClkType to TRCGPS_CLK,

and the synchronization with the GPS clock for a NodeB can be enabled by setting CLKSRC to

GPSCARD. In GPS clock synchronization, the GPS clock serves as the reference clock of the MBTS

and a GPS satellite card is required. In the case of a DBS3900/BTS3900/BTS3900A, the Universal

Satellite card and Clock Unit (USCU) needs to be configured.

For a BTS, the parameter CFGFLAG must be set to YES. The parameters relevant to this clock

synchronization mode are listed below:

GPSORGLONASS: specifies whether the GPS clock or the Glonass clock works as the reference

clock when two satellite cards are used.

ANTENNALONG: specifies the length of the feeder cable, which connects the GPS satellite card to

the antenna. The actual delay of the signals transmitted on the feeder can be calculated based on the

length of the feeder cable, thus improving the timing accuracy of the GPS satellite card.

ANTENNAPOWERSWITCH: specifies whether to supply power to the GPS antenna. When the GPS

antenna requires power supply, this parameter needs to be set to SENDPOWER. When the GPS

antenna does not require power supply, this parameter needs to be set to NOPOWER.

The GPS clock signals are processed and synchronized as follows:

The GPS antenna receives and transmits the GPS satellite signals to the GPS satellite card for

processing. The GPS satellite card then forwards the signals from the USCU to the main control board.

The main control board synchronizes the clock signals with the MBTS clock signals.

A GPS antenna can simultaneously trace up to eight satellites.

BITS Clock

The synchronization with the BITS clock for a BTS can be enabled by setting ClkType to EXTSYN_CLK,

and the synchronization with the BITS clock for a NodeB can be enabled by setting CLKSRC to BITS. In

BITS clock synchronization, the external BITS clock works as the reference clock of the MBTS. In the

case of a DBS3900/BTS3900/BTS3900A, the USCU must be configured.

The BITS clock signals are processed and synchronized as follows:

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-8

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

The BITS clock output port is connected to the BITS clock input port on the USCU. The master clock

module of the MBTS performs phase-locking and frequency division on the received clock signals to

generate clock signals required by the MBTS.

IP Clock

The MBTS supports IP clock synchronization. In an all-IP network, the MBTS can obtain clock signals

from the IP network. IP clocks can be classified into the synchronous Ethernet clock and the IEEE1588

V2 clock.

The IP network clock signals are processed and synchronized as follows:

The MBTS obtains clock signals from the FE/GE link. After local selection or frequency division, the

signals are sent to the clock module in the main control board as the reference clock. The clock module

in the main control board then converts the signals through phase-locking to generate clock signals

required by the MBTS. The 10 Mbit/s FE port of the MBTS does not support synchronization with the

Ethernet clock.

Internal Clock

The internal clock of the MBTS is generated by the main control board. The internal clock of the MBTS

can work in free-run mode to keep the MBTS running if the external reference clock is disabled or lost.

The enhanced stratum 3 OCXO with high accuracy works as the system clock of the MBTS. The OCXO

can ensure the normal operation of the MBTS for up to 90 days.

4.2.3 Clock Synchronization Process

The clock subsystem of the MBTS provides the timing synchronization function for the transmission

subsystem, baseband subsystem, and RF subsystem of the MBTS. The MBTS supports multiple

reference clocks. The clock module in the WMPT/GTMU implements clock synchronization for the

MBTS. This module distributes timing signals for the entire MBTS.

Figure 4-7 NodeB clock synchronization process

As shown in Figure 4-7, the process of clock synchronization in the NodeB is as follows:

1. The clock signals are obtained from the external reference clock.

If the external reference clock is the line clock, the WMPT extracts the clock signals from the

transmission links over the Iub interface. If the external reference clock is the GPS clock, the GPS

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-9

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

antenna receives and transmits the GPS clock signals to the GPS satellite card for processing before

forwarding them to the WMPT. If the external reference clock is the BITS clock, the BITS port on the

USCU receives and forwards the clock signals to the WMPT.

2. The WMPT delivers the clock signals to its clock module.

3. In the WMPT, the clock module performs phase-locking and frequency division on the clock signals,

and then generates various clock signals required by the NodeB.

4. The WMPT distributes the clock signals to the other boards of the NodeB. Note that the clock signals

are forwarded to the MRRU/MRFU through the WBBP.

Figure 4-8 BTS clock synchronization process

As shown in Figure 4-8, the process of clock synchronization in the BTS is as follows:

1. The clock signals are obtained from the external reference clock.

If the external reference clock is the line clock, the GTMU extracts the clock signals from the

transmission links over the Abis interface. If the external reference clock is the GPS clock, the GPS

antenna receives and sends the GPS clock signals to GPS satellite card for processing before

forwarding them to the GTMU. If the external reference clock is the BITS clock, the BITS port on the

USCU receives and forwards the clock signals to the GTMU.

2. The GTMU delivers the clock signals to its clock module.

3. In the GTMU, the clock module performs phase-locking and frequency division on the clock signals,

and then generates various clock signals required by the BTS.

4. The GTMU distributes the clock signals to the other boards of the BTS.

If the MBTS is configured with the Universal BaseBand Radio Interface Board (UBRI), the clock signals are forwarded to

the MRRU/MRFU through the UBRI.

4.3 MBTS Common Clock Solution

4.3.1 Overview

This section describes the common clock solution on the MBTS side. The common clocks involved are

the GSM and UMTS (GU) common reference clock, GSM and LTE (GL) common reference clock, and

UMTS and LTE (UL) common reference clock.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-10

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

The common clock solution enables two base stations using different radio access technologies (RATs)

to share the same clock source. In a common clock scenario, only one set of clock equipment is required.

After the base station using a RAT obtains the reference clock, this base station shares its reference

clock with the base station using a different RAT. For example, a BTS can share its reference clock with

an eNodeB, and an eNodeB can also share its reference clock with a BTS. If the base station using a

RAT uses the reference clock shared by the base station using a different RAT, the reference clock of the

former base station needs to be configured as the peer reference clock. For example, if a BTS uses the

reference clock shared by an eNodeB, the parameter ClkType of the BTS needs to be set to

PEER_CLK.

The GU/GL/UL common clock solution is supported by Huawei MBTSs that share a common baseband

unit (BBU). The common clock solution corresponds to the features MRFD-221601 Multi-mode BS

Common Reference Clock (NodeB) and MRFD-211601 Multi-mode BS Common Reference Clock

(GBTS).

When the base stations using different RATs share a BBU, the boards of the base stations are installed in the same BBU.

4.3.2 Common GPS Reference Clock

As shown in Figure 4-9, Figure 4-10 and Figure 4-11, the Universal Satellite card and Clock Unit (USCU)

of the MBTS receives the GPS clock signals and then distributes them to the base stations using

different RATs as the reference clock. In such a case, only one GPS antenna system is required. This

reduces deployment costs.

Figure 4-9 Example of a common GPS reference clock for GU

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-11

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-10 Example of a common GPS reference clock for GL

Figure 4-11 Example of a common GPS reference clock for UL

4.3.3 Common BITS Reference Clock

As shown in Figure 4-12, Figure 4-13, and Figure 4-14, the USCU of the MBTS receives the BITS clock

signals and then distributes them to the base stations using different RATs as the reference clock. In

such a case, only one set of external equipment is required. This reduces deployment costs.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-12

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-12 Example of a common BITS reference clock for GU

Figure 4-13 Example of a common BITS reference clock for GL

Figure 4-14 Example of a common BITS reference clock for UL

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-13

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

4.3.4 Common E1/T1 Reference Clock

As shown in Figure 4-15, Figure 4-16 and Figure 4-17, the base station using a RAT obtains the

reference clock from an E1/T1 link. The base station using a different RAT synchronizes its clock signals

with this reference clock through the backplane of the multi-mode BBU. In this scenario, only one clock

server needs to be configured.

Figure 4-15 Example of a common E1/T1 reference clock for GU

Figure 4-16 Example of a common E1/T1 reference clock for GL

Figure 4-17 Example of a common E1/T1 reference clock for UL

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

To use a common E1/T1 reference clock, the following conditions must be met:

The base station using a RAT needs to be connected to the transport network through an E1/T1 link,

on which clock signals are transmitted.

This base station obtains the E1/T1 reference clock through the Abis/Iub/S1 interface.

The base station using a different RAT can use this synchronous E1/T1 reference clock through the

backplane channels of the multi-mode BBU.

Table 4-1 describes the typical deployment scenarios of a common E1/T1 reference clock.

Table 4-1 Typical deployment scenarios of a common E1/T1 reference clock

Deployment Scenario Description

Common E1/T1 When TDM over E1/T1 transmission is used over the Abis interface and IP

reference clock on the over FE/GE transmission is used over the S1 interface, the eNodeB can

BTS side obtain the reference clock from the E1/T1 link of the Abis interface.

When TDM over E1/T1 transmission is used over the Abis interface and IP

over FE/GE transmission is used over the Iub interface, the NodeB can obtain

the reference clock from the E1/T1 link of the Abis interface.

Common E1/T1 When TDM over E1/T1 transmission is used over the Iub interface and IP over

reference clock on the GE transmission is used over the S1 interface, the eNodeB can obtain the

NodeB side reference clock from the E1/T1 link of the Iub interface.

When the Iub and Abis interfaces use common transmission (co-transmission)

based on IP over E1/T1 or IP-based hybrid transmission on the MBTS side,

the BTS can obtain the reference clock from the E1/T1 link of the Iub interface.

The Universal Transmission Processing unit (UTRP) in GSM mode does not support E1/T1 clock synchronization.

The UTRP in LTE/UMTS mode supports E1/T1 clock synchronization.

For details about co-transmission, see the Common Transmission Feature Parameter Description of the SingleRAN

4.3.5 Common IEEE1588 V2 Reference Clock

The IP transport network supports the IEEE1588 V2 clock synchronization. As shown in Figure 4-18,

Figure 4-19 and Figure 4-20, the base station using a RAT is configured with an IEEE1588 V2 clock

client and connected to the transport network through an FE/GE port to obtain the IEEE1588 V2

reference clock. The clock module of this base station phase-locks the obtained reference clock and

then transmits the clock to the base station using a different RAT through the backplane channels of the

multi-mode BBU. The base station using a different RAT synchronizes its clock with this phase-locked

reference clock. In this solution, only one set of an IEEE1588 V2 clock server and a client is required.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-2

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-18 Example of a common IEEE1588 V2 reference clock for GU

Figure 4-19 Example of a common IEEE1588 V2 reference clock for GL

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-3

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-20 Example of a common IEEE1588 V2 reference clock for UL

The multicast IEEE1588 V2 clock is not supported in GU, GL, and UL co-transmission through FE port interconnection.

A BTS supports the common IEEE1588 V2 clock only when it has a GTMUb board.

Table 4-2 describes the typical deployment scenarios of a common IEEE1588 V2 reference clock.

Table 4-2 Typical deployment scenarios of a common IEEE1588 V2 reference clock

Deployment Description

Scenario

Common IEEE1588 When the Abis and S1 interfaces use IP-based co-transmission on the MBTS

V2 reference clock on side and the IP network supports IEEE1588 V2 clock synchronization, the BTS

the eNodeB side can obtain the reference clock from the LMPT through the backplane channels

of the multi-mode BBU.

When the Iub and S1 interfaces use IP-based co-transmission on the MBTS

side and the IP network supports IEEE1588 V2 clock synchronization, the

NodeB can obtain the reference clock from the LMPT through the backplane

channels of the multi-mode BBU.

Common IEEE1588 When the Iub and Abis interfaces use IP-based co-transmission on the MBTS

V2 reference clock on side and the IP network supports IEEE1588 V2 reference clock, the BTS can

the NodeB side obtain the reference clock from the WMPT through the backplane channels of

the multi-mode BBU.

4.3.6 Common Synchronous Ethernet Reference Clock

The IP transport network support Ethernet clock synchronization. As shown in Figure 4-21, Figure 4-22

and Figure 4-23, the base station using a RAT obtains a synchronous Ethernet reference clock from the

FE/GE link. The base station using a different RAT synchronizes its clock with this synchronous Ethernet

reference clock through the backplane channels of the multi-mode BBU.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-4

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Figure 4-21 Example of a common synchronous Ethernet reference clock for GU

Figure 4-22 Example of a common synchronous Ethernet reference clock for GL

Figure 4-23 Example of a common synchronous Ethernet reference clock for UL

Table 4-3 describes the typical deployment scenarios of a synchronous Ethernet reference clock.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-5

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 4 SingleRAN Clock Solutions

Table 4-3 Typical deployment scenarios of a synchronous Ethernet reference clock

Deployment Scenario Description

Common synchronous When the Abis and S1 interfaces use IP-based co-transmission on the MBTS

Ethernet reference side and the IP network supports Ethernet clock synchronization, the BTS can

clock on the eNodeB obtain the reference clock from the LMPT or LTE UTRP through the

side backplane channels of the multi-mode BBU.

When the Iub and S1 interfaces use IP-based co-transmission on the MBTS

side and the IP network supports Ethernet clock synchronization, the NodeB

can obtain the reference clock from the LMPT or LTE UTRP through the

backplane channels of the multi-mode BBU.

Common synchronous When the Iub and Abis interfaces use IP-based co-transmission on the MBTS

Ethernet reference side and the IP network supports synchronous Ethernet clock, the BTS can

clock on the NodeB obtain the reference clock from the WMPT or UMTS UTRP through the

side backplane channels of the multi-mode BBU.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 4-6

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

5 Appendix Synchronization Process in the UTRAN

5.1 Overview

The synchronization process in the UTRAN consists of:

Network synchronization

Node synchronization

Frame synchronization

Radio interface synchronization

Figure 5-1 shows the relationships among synchronization functions.

Figure 5-1 Relationships among synchronization functions

Network synchronization is responsible for the distribution of clocks and allows the clocks to operate at

the same frequency in different network nodes.

Node synchronization is responsible for the measurement of phase difference between the RNC and the

NodeB. Node synchronization is the basis for the numbering of frames between the RNC and the NodeB

and for frame timing. The correct operation of node synchronization is dependent on the proper

operation of network synchronization.

Frame synchronization is responsible for the numbering and transmission of frames between the RNC

and the NodeB at the correct time, thus compensating for transmission delay and processing delay on

the RNC-NodeB path. The correct operation of frame synchronization within the radio network

subsystem (RNS) is dependent on the proper operation of node synchronization.

Radio interface synchronization is responsible for the alignment of frames between the NodeB and the

UE.

For the synchronization process in the UTRAN, see 3GPP TS 25.402.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-1

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

5.2 Network Synchronization

5.2.1 Overview

The network synchronization function allocates the common time and frequency to all the network

elements (NEs).

A synchronization network is a network that provides clock signals to traffic networks. The

synchronization network is composed of nodes that are connected through synchronization links.

Network synchronization involves:

Clock selection

Clock generation

Clock holdover

Clock distribution within a network node

5.2.2 Network Synchronization Modes

Figure 5-2 Network synchronization modes

The network synchronization modes shown in Figure 5-2 are described as follows:

Plesiochronous synchronization

In a plesiochronous network, each node has an independent clock.

Master-slave synchronization

Master-slave synchronization is the most commonly used synchronization mode. A master-slave

synchronization network has a single PRC, to which all other clocks on the network are locked.

Mutual synchronization

In a mutual synchronization network, there is no PRC. Each clock can receive the clock signals from

another.

5.2.3 Network Synchronization in the UTRAN

Network synchronization in the UTRAN synchronizes the NEs in the UTRAN either with the transport

network (for example, the SDH/PDH network or IP network) or with an external high-stability reference

clock (such as the GPS). The purpose is to ensure the stability of clocks and to meet the requirements of

the Iub and Iu interfaces.

Clock signals are distributed in a master-slave manner within the UTRAN, as shown in Figure 5-3.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-2

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

Figure 5-3 Network synchronization in the UTRAN

The RNC and NodeB need to synchronize the frequencies of their internal timing units (TUs) with a

common and traceable reference clock. The TU generates accurate and stable clock signals, distributes

them within the RNC or NodeB, and provides them for the outgoing PDH/SDH links or the radio interface.

In IP over Iub transmission mode, the RNC also generates time stamped IP packets.

5.3 Node Synchronization

5.3.1 Overview

The node synchronization function measures and compensates for the time offset between the RNC and

the NodeB and provides identical time reference for different network nodes.

The task of node synchronization is to measure the phase difference between the RFN counter and the

BFN counter. The measurement result is used in frame synchronization to minimize delays and buffer

sizes on the network.

5.3.2 Node Synchronization Procedure

Figure 5-4 shows the procedure for node synchronization between the RNC and the NodeB.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-3

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

Figure 5-4 Node synchronization procedure

Table 5-1 Parameters involved in node synchronization

Parameter Description

t1 RFN indicating the time when the RNC sends a DL Node Synchronization control frame to

the transport network layer

t2 BFN indicating the time when the NodeB receives the DL Node Synchronization control

frame from the transport network layer

t3 BFN indicating the time when the NodeB sends a UL Node Synchronization control frame

to the transport network layer

t4 RFN indicating the time when the RNC receives the UL Node Synchronization control

frame from the transport network layer

The node synchronization procedure is described as follows:

1. To measure the time offset between the RNC and the NodeB, the RNC sends the NodeB a DL Node

Synchronization control frame, including the time parameter t1 (RFN).

2. After receiving the DL Node Synchronization control frame, the NodeB responds with a UL Node

Synchronization control frame, including the time parameters t2 (BFN), t3 (BFN), and t1.

3. After receiving the UL Node Synchronization control frame, the RNC records the time t4 (RFN).

Then, the RNC calculates (t2 - t1) + (t4 - t3) to obtain the round trip delay (RTD) between the RNC and the

NodeB.

5.4 Frame Synchronization

5.4.1 Overview

The frame synchronization function synchronizes and monitors the data frames transmitted between

RNCs and between the RNC and the NodeB. Frame synchronization helps reduce the buffering time,

lower the requirement for the buffer sizes of network nodes, and thus minimize the transmission delay in

the UTRAN.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-4

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

In the downlink, the RNC needs to perform frame synchronization before sending data frames on the

radio interface. With frame synchronization, a common data frame reference, that is, a Connection

Frame Number (CFN), is provided between a transport channel on the UTRAN side and a transport

channel on the UE side to identify the transmission sequence of a Transport Block Set (TBS).

Each TBS has a CFN. The CFN at the transmission end must be the same as that at the reception end.

This consistency is ensured through the mapping between the CFN and the System Frame Number

(SFN) of the cell, considering that the CFN is not transmitted on the radio interface whereas the SFN is

transmitted on the broadcast channel.

5.4.2 Frame Timing Supervision

The QoS of radio links is affected if data frames from the RNC arrive at the NodeB too early or too late.

The frame synchronization supervision function compares the actual arrival time of data frames with the

supervision window. This function ensures that data frames arrive at the NodeB within a proper

supervision window by supervising and adjusting the Time of Arrival (TOA) of data frames on the Iub and

Iur interfaces.

The NodeB is responsible for supervising the TOA of downlink data frames, and the RNC is responsible

for supervising the TOA of uplink data frames. A supervision window is defined for the uplink and another

is defined for the downlink. Frame synchronization ensures that data frames arrive within the

corresponding supervision window. When a transport channel is established, a supervision window is

allocated to this channel. Figure 5-5 shows downlink TOA supervision. Uplink TOA supervision is similar

to downlink TOA supervision and therefore it is not further discussed in this document.

Figure 5-5 Downlink TOA supervision

Table 5-2 Parameters involved in downlink TOA supervision

Parameter Description

TOAE Specifies the earliest time that the RNC can send a data frame to the NodeB.

TOAWS Specifies the start point of the optimum data receiving window, that is, the

desired window.

TOAWE Specifies the end point of the desired window.

If a data frame arrives before this point, the TOA is greater than zero. If a data

frame arrives after this point, the TOA is smaller than zero.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-5

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

Parameter Description

tproc Specifies the time taken to process a data frame by the physical layer of the

NodeB before transmission on the air interface.

LTOA Specifies the latest time that the RNC can send a data frame to the NodeB.

The terms shown in Figure 5-5 are defined as follows:

Too early

If a data frame sent by the RNC arrives at the NodeB before the TOAE, it indicates that the RNC sends

the data frame too early, and thus the NodeB does not have a sufficient buffer area to receive this data

frame.

Early

If a data frame sent by the RNC arrives at the NodeB before the desired window, it indicates that the

RNC sends the data frame earlier than expected.

OK

If a data frame sent by the RNC arrives at the NodeB within the desired window, it indicates that the

RNC sends the data frame at a proper time.

Late

If a data frame sent by the RNC arrives at the NodeB after the desired window and before the LTOA, it

indicates that the RNC sends the data frame later than expected.

Too late

If a data frame sent by the RNC arrives at the NodeB after the LTOA, it indicates that the RNC sends

the data frame too late and the NodeB does not have time for frame processing, such as channel

coding and spreading. As a result, the data frame cannot be sent to the UE in time.

Using the TOA supervision function, the RNC adjusts the timing for transmitting a data frame to meet the

requirement of the desired window established at the NodeB. If data frames sent by the RNC arrive at

the NodeB outside the desired window, the NodeB prompts the RNC to advance or postpone the

transmission of data frames.

5.4.3 Frame Timing Adjustment

In the case of downlink data transmission, the data reception time of the lower-level network node, for

example the NodeB, is taken as the reference time to adjust the data transmission time of the

upper-level network node, for example the RNC. In the case of uplink data transmission, the receiving

window in the upper-level network node is adjusted.

If a data frame transmitted on the transport channel arrives at the NodeB or RNC outside the desired

window, the frame timing adjustment function responds with a Timing Adjustment control frame,

including the CFN and TOA. The RNC then adjusts the timing based on the Timing Adjustment control

frame.

Figure 5-6 shows an example of frame timing adjustment. In this example, a data frame sent by the RNC

arrives at the NodeB outside the receiving window and the TOA is smaller than zero. In this case, the

NodeB responds with a Timing Adjustment control frame, prompting the RNC to advance data

transmission.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-6

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

Figure 5-6 An example of frame timing adjustment

5.5 Radio Interface Synchronization

5.5.1 Overview

The radio interface synchronization function monitors the synchronization status of radio links. Data can

be transmitted and received in the uplink and downlink in sequence only after the synchronization is

complete. When multiple users transmit data simultaneously in a network, this function schedules and

coordinates them for transmission.

One purpose of radio interface synchronization is to ensure that the radio signals sent over the radio

interface arrive at a UE within an ideal time range. For example, in the case of a soft handover, this

function ensures that multipath signals simultaneously arrive at the UE. The other purpose is to ensure

the orthogonality between physical channels.

5.5.2 Radio Interface Synchronization Procedure

In the process of establishing a radio link, the radio link can be used by the UE only after the

synchronization is complete. Figure 5-7 shows the radio interface synchronization procedure during the

establishment of a single radio link.

Issue 01 (2010-10-15) Huawei Proprietary and Confidential 5-7

Copyright © Huawei Technologies Co., Ltd

SingleRAN

Synchronization 5 Appendix Synchronization Process in the UTRAN

Figure 5-7 Radio interface synchronization procedure

Table 5-3 describes the parameters involved in radio interface synchronization.

Table 5-3 Parameters involved in radio interface synchronization

Parameter Description

DOFF Specifies the default DPCH offset value, containing the frame offset and chip offset.

When the first radio link is established for a UE, the frame offset and chip offset are

defined for the radio link.

Frame offset Specifies the mapping between the SFN and the CFN.

The frame offset involved in radio interface synchronization refers to the frame offset of

the DL DPCH relative to the P-CCPCH at both the NodeB and the UE.

Chip offset Specifies the chip offset of the DL DPCH relative to the P-CCPCH.

The radio interface synchronization procedure is described as follows:

1. The UE sends an RRC CONNECTION REQUEST message to the RNC.

2. The RNC obtains the DOFF. If the RNC decides to allocate a radio link, the RNC also calculates the