Professional Documents

Culture Documents

ESElect 162023 ESD

ESElect 162023 ESD

Uploaded by

Fırat Kağıtçı0 ratings0% found this document useful (0 votes)

3 views65 pagesOriginal Title

ESElect162023ESD

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

3 views65 pagesESElect 162023 ESD

ESElect 162023 ESD

Uploaded by

Fırat KağıtçıCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 65

Lecture 16

Prof. Eros Pasero

HC00 data sheet

ESD Protection? Human Body Model? Machine

Model? Charge Device Model?

Latch Up?

2023 Electronic System Engineering™ - Prof. Eros Pasero 2

Electro Static Discharge (ESD)

Static Energy

Triboelectric effect

ESD definition

ESD Failures

ESD Studies

Standard Models:

Human Body Model

Machine Model

Charged Device Model

2023 Electronic System Engineering™ - Prof. Eros Pasero 3

Static energy

It’s an electric charge coming from

an electrons imbalance on the

surface of an object

When 2 objects have different

electrical potentials you have a fast

charge transfer when the 2 objects

are in contact

Static electricity creation =>

triboelectric effect

2023 Electronic System Engineering™ - Prof. Eros Pasero 4

Parameters influencing electrical

discharge

Environment conditions: humidity…

Scrub speed

Contact area

Material:

Positive charge: nylon, hairs, fur….

Negative charge: teflon, silicon, gold….

2023 Electronic System Engineering™ - Prof. Eros Pasero 5

Humidity

2023 Electronic System Engineering™ - Prof. Eros Pasero 6

ESD in Ics: definition

ESD is a transient discharge of static charge

that arises from either human handling or a

machine contact.

Although ESD is the result of a static

potential in a charged object, the energy

dissipated and damages made are mainly

due to the current flowing through ICs

during discharge.

2023 Electronic System Engineering™ - Prof. Eros Pasero 7

ESD

Becomes a problem when current densities closely

approach or exceed 500,000 A/cm2

For sub-micron width leads, this translates to

currents of only a few milliamps

Slow wearout of metallization caused by excessive

current densities

=>Electromigration

2023 Electronic System Engineering™ - Prof. Eros Pasero 8

Difficult to recognize

IC sometime don’t work: transient stress? No, ESD

Random problems, infant mortality, production

defects? NO, ESD

Different problems not immediately after the

discharge

You don’t have the right instrumentation to check the

problem

It’s economically profitable to replace the part!

2023 Electronic System Engineering™ - Prof. Eros Pasero 9

Failures

2023 Electronic System Engineering™ - Prof. Eros Pasero 10

ESD damages

pn-junction may melt.

Gate oxide may have void formation.

Metal interconnects & Vias may melt or

vaporization, leading to shorts or opens.

Gate-oxide breakdown is another form of

ESD damage.

2023 Electronic System Engineering™ - Prof. Eros Pasero 11

ESD failures in Ics

Gate oxide damage Junction breakdown

Metal/via damage

2023 Electronic System Engineering™ - Prof. Eros Pasero 12

ESD studies

2023 Electronic System Engineering™ - Prof. Eros Pasero 13

Why is ESD Critical ?

gate oxide thickness junction depth

The level of ESD stress, however, does not scale down

with the technology!

2023 Electronic System Engineering™ - Prof. Eros Pasero 14

Device: protection circuits

2023 Electronic System Engineering™ - Prof. Eros Pasero 15

Input:

Ci ≤ 5 pF and Ri = 1012 Ω High Zi

Electro static charges

Clamp diodes: Vi > Vcc + Vth CLAMP

Vi < GND + Vth CLAMP

Rs ≈250 Ω Current limit when high Vi is applied to inputs

2023 Electronic System Engineering™ - Prof. Eros Pasero 16

Xoxyde < 500 Å (1 Å = 10-10 m => Xox = 50 nm)

Dielectric strenght = 107 V/cm => 1 V/nm

=> Break down when Vgs>50V

22 nm technology

Gate length: 22 nm

Oxide Thickness: 0.8 nm (SiO2)=> higher leakage I:

High K dielectrics larger thickness with small Cox

Junction depth: 20 nm

2023 Electronic System Engineering™ - Prof. Eros Pasero 17

Principle Sources of ESD in ICs

Human Handling

A person walking on a synthetic floor can accumulate

up to 20 kV. (Icharge = 1-10 A @ ∆t =10-100 ns).This

voltage is discharged when the person touches an

object that is sufficiently at ground.

Test and Handling Systems

Equipment can accumulate static charge due to

improper grounding. The charge is transmitted

through ICs when it is picked up for placement in test

sockets.

2023 Electronic System Engineering™ - Prof. Eros Pasero 18

Principle Sources of ESD in ICs

IC Itself is Charged During Transport / Contact

With Charged Objects:

ICs remain charged until they come into contact

with a grounded surface (large metal plates /test

sockets). Charge is discharged through the pins of

ICs. Large currents in the internal interconnects

can result in high voltage inside the devices which

can cause damage to thin dielectrics and

insulators.

2023 Electronic System Engineering™ - Prof. Eros Pasero 19

Modelling: 3 Standard models

HBM: Human Body Model

MM: machine Model

CDM: Charged Device Model

2023 Electronic System Engineering™ - Prof. Eros Pasero 20

MIL-STD-883 Method 3015 - ESD STM5.1: Electrostatic Discharge

Sensitivity Testing -- Human Body Model

2023 Electronic System Engineering™ - Prof. Eros Pasero 21

2023 Electronic System Engineering™ - Prof. Eros Pasero 22

Resistance in a Wrist Strap System

2023 Electronic System Engineering™ - Prof. Eros Pasero 23

Anti-Static Products

2023 Electronic System Engineering™ - Prof. Eros Pasero 24

Real Model

2023 Electronic System Engineering™ - Prof. Eros Pasero 25

Destruction mechanisms

1. Short transition time: tr < 1 ns. The protection

circuit is not still active and the discharge

power can’t be dissipated.

2. High peak currents Ipeak > 1.5 A

3. High discharge energy

2023 Electronic System Engineering™ - Prof. Eros Pasero 26

How much energy is at stake?

You must dissipate:

E ≈ ½ V2 C

V = 2000V e C = 100 pF

=> E= 20 mJ

2023 Electronic System Engineering™ - Prof. Eros Pasero 27

ESD STM5.2: Electrostatic Discharge Sensitivity Testing -- Machine

Model

2023 Electronic System Engineering™ - Prof. Eros Pasero 28

Integrated circuit packaging

2023 Electronic System Engineering™ - Prof. Eros Pasero 29

Discharge Energy

E = ½ V2 C = ½ 5002 200 10-12 = 25 µJ

L = 500 nH depends on the length of

wire and series inductance of the wires

utilized

2023 Electronic System Engineering™ - Prof. Eros Pasero 30

V = .5 – 2 kV

ESD STM5.3.1: Electrostatic Discharge

Sensitivity Testing - Charged Device Model Metal Plate

2023 Electronic System Engineering™ - Prof. Eros Pasero 31

Pick place machine

Surface mount component feeder

2023 Electronic System Engineering™ - Prof. Eros Pasero 32

CDM test

2023 Electronic System Engineering™ - Prof. Eros Pasero 33

Test wave forms

2023 Electronic System Engineering™ - Prof. Eros Pasero 34

E= ½ V2 C =0.5 10002 1000 10-12 = 0.5 mWs (or mJ)

2023 Electronic System Engineering™ - Prof. Eros Pasero 35

Temperature growth

CS = 1.631 Ws/Kcm3 silicon thermal capacity

Si fusion temperature = 1600 °C; Al fusion temperature << 1600 °C

>> Al melts and spreads into Si => the protection circuit becomes a

short circuit

2023 Electronic System Engineering™ - Prof. Eros Pasero 36

JEDEC STANDARD

JESD22-A115C (Revision of JESD22-A115B, March 2010)

Electrostatic Discharge (ESD) Sensitivity Testing,

Machine Model (MM)

About JEDEC

JEDEC brings manufacturers and suppliers together to

participate in more than 50 committees and

subcommittees, with the mission to create standards to

meet the diverse technical and developmental needs of

the industry.

2023 Electronic System Engineering™ - Prof. Eros Pasero 37

2023 Electronic System Engineering™ - Prof. Eros Pasero 38

2023 Electronic System Engineering™ - Prof. Eros Pasero 39

2023 Electronic System Engineering™ - Prof. Eros Pasero 40

Reference regulations

2023 Electronic System Engineering™ - Prof. Eros Pasero 41

ECE – R10 Rev. 5

6.10.4

• Electrostatic discharge

– For vehicles fitted with tyres, the vehicle body/chassis

can be considered to be an electrically isolated structure.

Significant electrostatic forces in relation to the vehicle's

external environment only occur at the moment of

occupant entry into or exit from the vehicle. As the

vehicle is stationary at these moments, no type approval

test for electrostatic discharge is deemed necessary.

2023 Electronic System Engineering™ - Prof. Eros Pasero 42

IEC 61000-4-2 (EN 61000-4-2)

The EUT is subjected to three types of discharge.

Direct contact discharge is preferred either directly to

the EUT or indirectly through vertical or horizontal

coupling planes. Air discharge is used where direct

contact cannot be applied.

2023 Electronic System Engineering™ - Prof. Eros Pasero 43

Environmental conditions

2023 Electronic System Engineering™ - Prof. Eros Pasero 44

Generator

2023 Electronic System Engineering™ - Prof. Eros Pasero 45

Discharge

AD CD

2023 Electronic System Engineering™ - Prof. Eros Pasero 46

Discharge Networks

2023 Electronic System Engineering™ - Prof. Eros Pasero 47

Evaluation

No change, according to manufacturer specifications

Temporary loss of function, ending after the test

Temporary loss of function requiring operator

loss of function not recoverable

2023 Electronic System Engineering™ - Prof. Eros Pasero 48

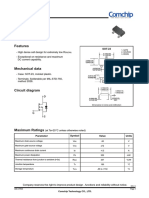

How to protect your inputs?

DVIULC6-4SC6Y: Automotive ultralow capacitance

ESD protection

4-line ESD protection (IEC 61000-4-2)

DVI ports up to 1.65 Gb/s

HDMI ports up to 1.65 Gb/s

IDB 1394

USB 2.0 ports up to 480 Mb/s (high speed),

backwards compatible with USB1.1 low and full

speed

Ethernet port: 10/100/1000 Mb/s

SIM card protection

Video line protection

2023 Electronic System Engineering™ - Prof. Eros Pasero 49

Silicon Controlled Rectifier

pnpn

A

A

K IG → Ic2 → Ic1 → Ib2 → Self

Distruction

2023 Electronic System Engineering™ - Prof. Eros Pasero 50

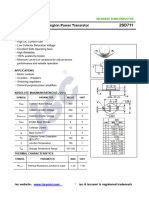

Thyristor

100 A 1200 V SCR

four-layered, three terminal semiconducting device,

with each layer consisting of alternately N-type or P-

type material, for example P-N-P-N.

arc welding machines

2023 Electronic System Engineering™ - Prof. Eros Pasero 51

TRIAC

Triode for Alternating Current

bidirectional triode thyristor

The bidirectionality makes TRIACs very

convenient switches for alternating

current circuits,

Light dimmers

2023 Electronic System Engineering™ - Prof. Eros Pasero 52

Latchup in Bulk CMOS

Electrostatic Discharge stress can cause

latch-up by injecting minority carriers from the

clamping device in the protection circuit into

either the substrate or the well.

β1β2 >1 =latchup

2023 Electronic System Engineering™ - Prof. Eros Pasero 53

2023 Electronic System Engineering™ - Prof. Eros Pasero 54

Shunted Rs and Rw

2023 Electronic System Engineering™ - Prof. Eros Pasero 55

2023 Electronic System Engineering™ - Prof. Eros Pasero 56

2023 Electronic System Engineering™ - Prof. Eros Pasero 57

2023 Electronic System Engineering™ - Prof. Eros Pasero 58

2023 Electronic System Engineering™ - Prof. Eros Pasero 59

2023 Electronic System Engineering™ - Prof. Eros Pasero 60

Buried contacts

The buried contact is a

method to make direct

ohmic contact between

the polysilicon gate

material and the

junctions, in silicon-gate

integrated circuits.

2023 Electronic System Engineering™ - Prof. Eros Pasero 61

The gate and source of a

depletion device can be

connected by a method

Butting contact known as butting contact.

Here metal makes contact

to both the diffusion

forming the source of the

depletion transistor and to

the poly silicon forming

this device’s gate.

Its advantage is that no

buried contact mask is

required and it avoids

associated processing.

2023 Electronic System Engineering™ - Prof. Eros Pasero 62

Preventing latchup: System approach

Make sure power supplies are off before plugging a board:

signal pins can see surge voltages greater than 0.7 V

higher than Vdd

Carefully protect electrostatic protection devices

associated with I/O pads with guard rings: Electrostatic

discharge can trigger latchup by means of the clamping

diodes which can inject minority carriers in the substrate

or well, potentially triggering latchup

Radiations can generate electron-hole pairs which can

contribute to well or substrate currents

Sudden transients on the power or ground bus (i.e. when

large numbers of transistors switch simultaneously)

2023 Electronic System Engineering™ - Prof. Eros Pasero 63

2023 Electronic System Engineering™ - Prof. Eros Pasero 64

2023 Electronic System Engineering™ - Prof. Eros Pasero 65

You might also like

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without GroundingRating: 4.5 out of 5 stars4.5/5 (2)

- Earthing Myths and FactsDocument67 pagesEarthing Myths and FactsPramode MishraNo ratings yet

- Applying Grounding and Shielding For Instrumentation PDFDocument44 pagesApplying Grounding and Shielding For Instrumentation PDFAnonymous zdCUbW8HfNo ratings yet

- ElectronicsDocument21 pagesElectronicsWirdan Alma NurillahNo ratings yet

- GroundingDocument32 pagesGroundingcharleselitb92100% (2)

- American Society of Irrigation Consultants: For The Latest Rev. Go ToDocument5 pagesAmerican Society of Irrigation Consultants: For The Latest Rev. Go Tosjameel66No ratings yet

- An5241 Fundamentals of Esd Protection at System Level StmicroelectronicsDocument19 pagesAn5241 Fundamentals of Esd Protection at System Level StmicroelectronicsAditya SrivatsavNo ratings yet

- Main Emt AssignmentDocument7 pagesMain Emt AssignmentDivijNo ratings yet

- Comchip ProductTraining ESD20121023Document23 pagesComchip ProductTraining ESD20121023Mastan ValiNo ratings yet

- A Current Measurement Procedure For The ESD Generators According To The EN 61000-4-2Document6 pagesA Current Measurement Procedure For The ESD Generators According To The EN 61000-4-2Alfredo CordovaNo ratings yet

- Iec 62305Document58 pagesIec 62305Rajeshkumar MathiyazhaganNo ratings yet

- Erico Master CatelogueDocument72 pagesErico Master CatelogueDokania AnandNo ratings yet

- ESDDocument60 pagesESDGopi PremalaNo ratings yet

- LT0359Document72 pagesLT0359jinyuan74No ratings yet

- Conceitos Basicos Automa Ç Ã o - Pea 3411 - v0Document9 pagesConceitos Basicos Automa Ç Ã o - Pea 3411 - v0Alexandre RamosNo ratings yet

- Analysis of Electrical Grounding Design of Substation and Lines - Journal PublishedDocument10 pagesAnalysis of Electrical Grounding Design of Substation and Lines - Journal PublishedJames UjamNo ratings yet

- Electrostatic Sensitive DevicesDocument7 pagesElectrostatic Sensitive Devicesvinay100% (1)

- Optical Fiber Cables Near High Voltage CircuitsDocument3 pagesOptical Fiber Cables Near High Voltage CircuitsAgustino84No ratings yet

- ESD Prevention For GSFC Hardware: Prepared byDocument12 pagesESD Prevention For GSFC Hardware: Prepared byNilesh NarkhedeNo ratings yet

- Presentation Lightning Protection System by JMV LPSDocument62 pagesPresentation Lightning Protection System by JMV LPSMahesh Chandra ManavNo ratings yet

- EMCoS - Modeling of Electrostatic Discharge (ESD)Document5 pagesEMCoS - Modeling of Electrostatic Discharge (ESD)Santhosh LingappaNo ratings yet

- Near Field Immunity Cartography Method To Characterize An IC To Fields Radiated by An ESDDocument6 pagesNear Field Immunity Cartography Method To Characterize An IC To Fields Radiated by An ESDhwa6jin6choiNo ratings yet

- Esa2010 c1 BerndtDocument13 pagesEsa2010 c1 BerndtAamer MohammedNo ratings yet

- A Study of Failure Mechanisms in CMOS & BJT ICs and Their Effect On Device ReliabilityDocument6 pagesA Study of Failure Mechanisms in CMOS & BJT ICs and Their Effect On Device ReliabilityCB MildredNo ratings yet

- Electrostatic Discharge Analysis of Multi Layer Ceramic CapacitorsDocument6 pagesElectrostatic Discharge Analysis of Multi Layer Ceramic CapacitorsZetocha MilanNo ratings yet

- Electrical Past PaperDocument14 pagesElectrical Past PaperdiciiuniverseNo ratings yet

- Brochure - Sika Technology - Concepts - For ESD - Conductive FlooringDocument20 pagesBrochure - Sika Technology - Concepts - For ESD - Conductive FlooringheshamNo ratings yet

- Analysis of Transfer Touch Voltages in Low-Voltage Electrical InstallationsDocument12 pagesAnalysis of Transfer Touch Voltages in Low-Voltage Electrical InstallationsMenaNo ratings yet

- 9 Recommended Practices For GroundingDocument6 pages9 Recommended Practices For Groundingsikander843562No ratings yet

- Design of Earthing SystemDocument5 pagesDesign of Earthing SystemNishant Sinha100% (1)

- 02 Pe 05 21 5-11Document8 pages02 Pe 05 21 5-11delta conceptNo ratings yet

- AN651Document10 pagesAN651Barun SahaNo ratings yet

- Design of Earthing - Grounding System in A Substation Grid - Electrical TechnologyDocument9 pagesDesign of Earthing - Grounding System in A Substation Grid - Electrical TechnologyThenul DisaraNo ratings yet

- Electrical Earthling: Construction, Faults & ProtectionDocument24 pagesElectrical Earthling: Construction, Faults & ProtectionsitanshumnitNo ratings yet

- Electrostatic Discharge (Esd)Document10 pagesElectrostatic Discharge (Esd)NurdianAsriNo ratings yet

- ELEC4611-15-Lec2 - Electric Stress in HV EquipmentDocument24 pagesELEC4611-15-Lec2 - Electric Stress in HV EquipmentPeterNo ratings yet

- ElecticalSafety HighVoltageDocument3 pagesElecticalSafety HighVoltagesiswoutNo ratings yet

- Ds162 e Foundation Earth ElectrodesDocument28 pagesDs162 e Foundation Earth ElectrodesplennyNo ratings yet

- Computer Modeling and Simulation of Grounding Systems in Power Stations and SubstationsDocument120 pagesComputer Modeling and Simulation of Grounding Systems in Power Stations and SubstationsIslam GolaćNo ratings yet

- Iot Based Underground Cable Fault Detector: Mr. N. SampathrajaDocument11 pagesIot Based Underground Cable Fault Detector: Mr. N. SampathrajaRenu RaiNo ratings yet

- Computer Aided Design of Transformer Station Grounding System Using CdegsDocument8 pagesComputer Aided Design of Transformer Station Grounding System Using CdegsAnwesh Kumar MaddikuntaNo ratings yet

- Underground Cable Fault Detection and Location Finding: XXXXXXX 1XxxxxxDocument38 pagesUnderground Cable Fault Detection and Location Finding: XXXXXXX 1Xxxxxxshaik shaNo ratings yet

- 00BA28Document9 pages00BA28Luis Adrián ElguézabalNo ratings yet

- Cahier 178Document31 pagesCahier 178Heri Tri SetiawanNo ratings yet

- Grounding Products and SystemsDocument84 pagesGrounding Products and SystemsEric Aarriaga AlpizarNo ratings yet

- White Paper On Cathodic Protection Sept 2000Document10 pagesWhite Paper On Cathodic Protection Sept 2000Jorge LunaNo ratings yet

- Iec Lab Report 1Document12 pagesIec Lab Report 1mahrabhasanchowdhury1No ratings yet

- "Watts Current" Technical Bulletin... Ground Resistance Testing Models 6422 & 6424 - Chauvin ArnouxDocument14 pages"Watts Current" Technical Bulletin... Ground Resistance Testing Models 6422 & 6424 - Chauvin ArnouxGustavo PérezNo ratings yet

- Aircraft EWIS Electromagnetic Interference Wiring Res 2011 Procedia EngineerDocument8 pagesAircraft EWIS Electromagnetic Interference Wiring Res 2011 Procedia EngineerEnsar OğuzNo ratings yet

- Transmission Line Tower Earthing Analysis Using SafeGridDocument5 pagesTransmission Line Tower Earthing Analysis Using SafeGridajrojas1359No ratings yet

- ESD Protection: Design and Layout Issues For VLSI Circuits: Ieee 25, 1989Document7 pagesESD Protection: Design and Layout Issues For VLSI Circuits: Ieee 25, 1989Donna AmbalongNo ratings yet

- A Primer On A Good Instrument Grounding SystemDocument26 pagesA Primer On A Good Instrument Grounding SystemwlmostiaNo ratings yet

- 02 Pe 05 21 5-11Document8 pages02 Pe 05 21 5-11AlairNo ratings yet

- Erratic Nature of Product ESD Immunity TestingDocument4 pagesErratic Nature of Product ESD Immunity Testingari goldNo ratings yet

- Guia Soluciones Parque FotovoltaicoDocument18 pagesGuia Soluciones Parque FotovoltaicoEnrique MirandaNo ratings yet

- Design of Grounding System For A.C. Substations With Critical Consideration of The Mesh, Touch and Step PotentialsDocument15 pagesDesign of Grounding System For A.C. Substations With Critical Consideration of The Mesh, Touch and Step PotentialsGhhNo ratings yet

- On-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsFrom EverandOn-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsNo ratings yet

- Fundamentals of Electromigration-Aware Integrated Circuit DesignFrom EverandFundamentals of Electromigration-Aware Integrated Circuit DesignNo ratings yet

- ESElect152023 - FinalPCB ChecksDocument28 pagesESElect152023 - FinalPCB ChecksFırat KağıtçıNo ratings yet

- ESElect1tris2023 CADENCEDocument5 pagesESElect1tris2023 CADENCEFırat KağıtçıNo ratings yet

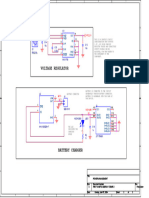

- POWERDocument1 pagePOWERFırat KağıtçıNo ratings yet

- SENSORDocument1 pageSENSORFırat KağıtçıNo ratings yet

- Guidelines Appointment LMDocument2 pagesGuidelines Appointment LMFırat KağıtçıNo ratings yet

- RCAGLOBALDocument153 pagesRCAGLOBALsergecheshut100% (1)

- Fundamentals of CMOS VLSI QBDocument6 pagesFundamentals of CMOS VLSI QBharshithaNo ratings yet

- Fabless ManufacturingDocument4 pagesFabless ManufacturingballisticanaNo ratings yet

- NPN Silicon: Semiconductor Technical DataDocument4 pagesNPN Silicon: Semiconductor Technical DataRicardo VieraNo ratings yet

- Lec 11 Sequential Logic CircuitsDocument49 pagesLec 11 Sequential Logic CircuitsDeependra NigamNo ratings yet

- Data Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorDocument9 pagesData Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorMiloud ChouguiNo ratings yet

- Transistor - Transistor Logic (TTL) : I LowDocument17 pagesTransistor - Transistor Logic (TTL) : I LowwisamNo ratings yet

- Ec1461 Vlsi DesignDocument17 pagesEc1461 Vlsi DesignArunkumarNo ratings yet

- Design of A 100 V High-Side NCH LDMOS Breakdown EnhanceDocument4 pagesDesign of A 100 V High-Side NCH LDMOS Breakdown EnhanceRon HuangNo ratings yet

- AN005 PCB Guidelines TRINAMIC Packages Rev1.02Document32 pagesAN005 PCB Guidelines TRINAMIC Packages Rev1.02bahmanbdsNo ratings yet

- JefetDocument6 pagesJefetSoumyadipNo ratings yet

- Complex GateDocument44 pagesComplex Gatemisbahforu09No ratings yet

- Testing TransistorDocument15 pagesTesting TransistorElarrio Arel Perez ToribioNo ratings yet

- Chapter1 ASIC Design Flow EE3165Document98 pagesChapter1 ASIC Design Flow EE3165Sư LưuNo ratings yet

- VK BecDocument16 pagesVK BecDevdas JadhavNo ratings yet

- Special Purpose DiodesDocument4 pagesSpecial Purpose DiodesArvinALNo ratings yet

- CMP 2019Document5 pagesCMP 2019uam22No ratings yet

- AE25Document3 pagesAE25nandyindyNo ratings yet

- FETDocument75 pagesFETVenkateswara ReddyNo ratings yet

- 2SD711 InchangeDocument2 pages2SD711 InchangeJoseNo ratings yet

- TIP47/TIP48/TIP49/TIP50: NPN Silicon TransistorDocument5 pagesTIP47/TIP48/TIP49/TIP50: NPN Silicon TransistorPaola ElizabethNo ratings yet

- Auto Power Supply Control From 4 Different Sources Solar, Mains, Generator & Inverter To Ensure No Break PowerDocument23 pagesAuto Power Supply Control From 4 Different Sources Solar, Mains, Generator & Inverter To Ensure No Break PowerAnonymous QIuAGIadXm69% (13)

- CMOS Process FlowDocument39 pagesCMOS Process FlowYashaswa JainNo ratings yet

- Afn3400 Alpha-Mos PDFDocument7 pagesAfn3400 Alpha-Mos PDFdoraemon007No ratings yet

- Power BJT: Darlington TransistorsDocument2 pagesPower BJT: Darlington TransistorsKarteekNo ratings yet

- Equivalentes SMD X ConvencionalDocument134 pagesEquivalentes SMD X Convencionaldiney m e willemen100% (2)

- CJ3401-HF RevB289632Document5 pagesCJ3401-HF RevB289632alteromr mrNo ratings yet

- Obsolete - Part Discontinued: General Description FeaturesDocument10 pagesObsolete - Part Discontinued: General Description FeaturesamitNo ratings yet

- 454 Final Cheat SheetDocument4 pages454 Final Cheat SheetJoe MorganNo ratings yet

- Plastic Silicon Infrared Phototransistor QSC112 QSC113 QSC114Document4 pagesPlastic Silicon Infrared Phototransistor QSC112 QSC113 QSC114raveendraNo ratings yet