Professional Documents

Culture Documents

Outline-CS-Morning-SEction A

Outline-CS-Morning-SEction A

Uploaded by

athermaqsood26Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Outline-CS-Morning-SEction A

Outline-CS-Morning-SEction A

Uploaded by

athermaqsood26Copyright:

Available Formats

PIR MEHR ALI SHAH ARID AGRICULTURE UNIVERSITY

University Institute of Information Technology

CS-430 Digital Logic Design

Credit Hours: 4(3 2) Prerequisites:

Course Contents:

Introduction to concept and definitions used in digital logic design. Difference between

analog and digital system along with TTL and CMOS logics. Number systems, Boolean

algebra and logic gates. Analysis of gate level minimization with 2-level networks and

Karnaugh maps. Combinational logic systems that includes encoders, decoders,

multiplexers, demultiplexers. Sequential logic systems are gated latch and flip-flop i.e.

SR, JK, D and T. Design of sequential modules consist of registers, shift registers and

universal registers along with counters i.e. synchronous and asynchronous counters.

Programmable devices: microcontroller, ROM and programmable aarays.

Course Objective:

The aim of this course is to introduce the students with the electronics components of

modern digital world that includes the combinational and sequential logic circuits

analysis and design. Digital circuits are merger of logic gates, encoder, decoder,

multiplexers, registers, counters and programmable logic arrays.

Teaching Methodology:

Lectures, Assignments, labs, Projects, Presentations, etc. Major component of the

course should be covered using conventional lectures. Practical contact hours are

compulsory.

Courses Assessment:

Exams, Assignments, Quizzes, Project, Presentations. Course will be assessed using a

combination of written examinations and project(s). Practical evaluation, using rubrics,

is encouraged and suggested to make up around 20% of the course.

Reference Materials:

Digital Design by Morris Mano (Book).

Digital Fundamentals by Thomas Floyd (Book).

DLD Lab Manual

Software tools: Logisim or Lattice diamond software.

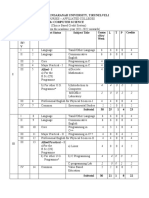

Week/Lecture # Theory Practical

Lecture-I Introduction to analog and digital systems.

Week 1 Lecture-II Number system conversions.

Lecture-III Conversion and compliments.

Lecture-I Binary, octal & Hexa addition/subtraction.

Week 2 Lecture-II Logic level. BCD addition.

Lecture-III Even odd parity bits. ASCII codes.

Lecture-I Logic gates, types, symbol & truth table.

Lecture-II Introduction to Boolean algebra & analysis

Week 3

Identities of Boolean algebra &

Lecture-III

simplification.

Week 4 Lecture-I Standard forms min-terms, max-terms,

sum of product (SOP) and product of sum

(POS).

Logic operations. Introduction to

Lecture-II

Karnaugh-map.

Two, three & four variable k-map

Lecture-III

simplifaction.

Two, three & four variable k-map

Lecture-I

manipulation.

Two level implementation and selection of

Week 5 Lecture-II

prime implicates and

Don’t care conditions (two, three & four

Lecture-III

variable k- map).

Lecture-I NAND & NOR as Universal gates.

AND, OR, NOT implementation using

Lecture-II

Week 6 NAND & NOR gates.

Combinational logic implementation using

Lecture-III

gates.

Introduction to DLD

Lecture-I

tools.

Verification of AND,

Lecture-II OR and NOT gate

Week 7

according to truth table.

Verification of NAND,

Lecture-III and NOR gate

according to truth table.

Verification of XOR

Lecture-I gate according to truth

table.

Week 8 Verification of universal

Lecture-II

gates.

Verification of universal

Lecture-III

gates.

Midterm Exam

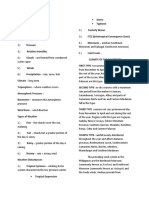

Lecture-I Design procedure for multilevel circuits.

Week 9 Lecture-II Half, full and parallel adder.

Lecture-III Half and full subtractor.

Encoder, decoder and magnitude

Lecture-I

comparator.

Week 10

Lecture-II Multiplexer, demultiplexer and ROM.

Lecture-III Sequential logic circuits implementation.

Lecture-I Flip Flop and their types. Clock.

Week 11 Lecture-II Triggering of Flip Flops.

Lecture-III Conversion of Flip Flops.

Lecture-I Registers and their types.

Week 12 Lecture-II Serial addition and shift registers.

Lecture-III Uni and bi-directional registers.

Lecture-I Universal shift registers.

Week 13 Lecture-II Introduction to counters. Ripple counter.

Lecture-III Synchronous and asynchronous counters.

Design half and full

Lecture-I

adder.

Design half and full

Week 14 Lecture-II

subtractor.

Design BCD seven-

Lecture-III

segment decoder.

To check operation of

Lecture-I

multiplexer.

Design basic RS flip

Week 15 Lecture-II

flop operations.

Design basic JK flip

Lecture-III

flop operations.

Lecture-I Registers.

Week 16 Lecture-II Counters.

Lecture-III Project demo.

Final term Exam

Course Learning Outcomes (CLOs)

At the end of course the students will be able to:

1. Deal with the tools and techniques for the design of digital electronic circuits.

2. Understand and analyze both combinational and sequential logic circuits.

3. Design small scale digital circuits through logical reasoning.

You might also like

- DLD ContentsDocument5 pagesDLD Contentsiabdurrehman12345No ratings yet

- Course Handout: Amity University RajasthanDocument5 pagesCourse Handout: Amity University RajasthanKaran MaanNo ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) Bhopalकिशोरी जूNo ratings yet

- EC6302Document107 pagesEC6302AJ ADNo ratings yet

- DLD Labs1Document1 pageDLD Labs1venkateswararao mNo ratings yet

- Data Structure and Algorithms (CS-443) : University Institute of Information TechnologyDocument6 pagesData Structure and Algorithms (CS-443) : University Institute of Information TechnologyHahsadasdNo ratings yet

- Course Objectives:: Topic Course Code Course Name SemesterDocument3 pagesCourse Objectives:: Topic Course Code Course Name Semesterabhishekash502No ratings yet

- DPCO Syllabus (Theory Cum Practical)Document2 pagesDPCO Syllabus (Theory Cum Practical)yogeshwaran.r2022lcseNo ratings yet

- CS8501 - THEORY OF COMPUTATION - by LearnEngineering - inDocument162 pagesCS8501 - THEORY OF COMPUTATION - by LearnEngineering - inKrisHnA 2kNo ratings yet

- Gamut National High School 11 Janelkris E. Plaza 3 Quarter IDocument2 pagesGamut National High School 11 Janelkris E. Plaza 3 Quarter IJanelkris PlazaNo ratings yet

- DSA - Course OutlineDocument5 pagesDSA - Course OutlineMuhammad AbubakarNo ratings yet

- Bubt Eee-304 Lab Manual - Edited 25-12-21 v2Document73 pagesBubt Eee-304 Lab Manual - Edited 25-12-21 v2Md. Arif Hasan MasumNo ratings yet

- M.Tech VLSISD R21 Final 6.3.21Document21 pagesM.Tech VLSISD R21 Final 6.3.21DrBhoopal RaoNo ratings yet

- DLD Final ManualDocument32 pagesDLD Final ManualM. Rayyan DawoodNo ratings yet

- A Theory of Objects by AbdaliDocument412 pagesA Theory of Objects by AbdaliAmitabhaPramanikNo ratings yet

- Ee429 Programmable Logic Controllers (Dept. Elective - IV) : Course Description & ObjectivesDocument1 pageEe429 Programmable Logic Controllers (Dept. Elective - IV) : Course Description & Objectivespilotvivek1087No ratings yet

- Mobile and Pervasive Computing 2008 RegDocument5 pagesMobile and Pervasive Computing 2008 RegaddssdfaNo ratings yet

- Manonmaniam Sundaranar University, Tirunelveli B.SC Computer ScienceDocument18 pagesManonmaniam Sundaranar University, Tirunelveli B.SC Computer ScienceTNEA TFC-51No ratings yet

- Lab Manual: Digital System Design (PR) : COT-215 Digital Electronics (P) : IT-211Document7 pagesLab Manual: Digital System Design (PR) : COT-215 Digital Electronics (P) : IT-211rajeshforallNo ratings yet

- Digital Logic Design Course Coordinator: Dr. Habibulla Khan Course Detail: Theory and Lab Lecture Hours: 45Document6 pagesDigital Logic Design Course Coordinator: Dr. Habibulla Khan Course Detail: Theory and Lab Lecture Hours: 45Sai PraveenNo ratings yet

- CO204 - Design of Digital Systems Lab (B. Tech, 3 Semester) : X y X yDocument4 pagesCO204 - Design of Digital Systems Lab (B. Tech, 3 Semester) : X y X yKeerti ChaudharyNo ratings yet

- R22M.tech - CSE SyllabusDocument50 pagesR22M.tech - CSE SyllabusSravan Kumar BNo ratings yet

- Syllabus DLCDocument3 pagesSyllabus DLCSuresh Kumar NandigamNo ratings yet

- Datapath ComponentsDocument78 pagesDatapath ComponentsDƯƠNG NGUYỄN THÁI BÌNHNo ratings yet

- EE206 DigitalSystemDesignDocument2 pagesEE206 DigitalSystemDesignRajalearn2 Ramlearn2No ratings yet

- Ldco CRB - 22-23 Sem I (Replica)Document25 pagesLdco CRB - 22-23 Sem I (Replica)Siddharth DarwadeNo ratings yet

- STLD LP - VparDocument4 pagesSTLD LP - VparVenkat ChadalavadaNo ratings yet

- Department of Education: Republic of The PhilippinesDocument2 pagesDepartment of Education: Republic of The Philippinescarren salenNo ratings yet

- Template Course Outline EXEMPLE DE SYLLABUSDocument5 pagesTemplate Course Outline EXEMPLE DE SYLLABUSGary ReyNo ratings yet

- R19 M.Tech. Digital Systems and Computer Electronics: Audit Course - IIDocument52 pagesR19 M.Tech. Digital Systems and Computer Electronics: Audit Course - IIchinthapatla YashwanthNo ratings yet

- 15CS202 - Digital System DesignDocument2 pages15CS202 - Digital System DesignRaut Amit DattatrayNo ratings yet

- Lab MANUAL - EDLD - July2022Document68 pagesLab MANUAL - EDLD - July2022darshanpote005No ratings yet

- DPSD 2022 - 23oct 19V1Document3 pagesDPSD 2022 - 23oct 19V1PRANAV VIKRAMAN S S ECE DEPTNo ratings yet

- List Of: Semester Examination PA - Progressive AssessmentDocument6 pagesList Of: Semester Examination PA - Progressive AssessmentrushilNo ratings yet

- PF LAB Course OutlineDocument3 pagesPF LAB Course OutlineZain IkramNo ratings yet

- Robotics: Course CurriculumDocument2 pagesRobotics: Course Curriculumsantosh malkhedkarNo ratings yet

- VLSI Lab Man CMPLTDocument52 pagesVLSI Lab Man CMPLTŞøfţbóý HãřîNo ratings yet

- EE-227 Electronics Engineering (Course Outline)Document4 pagesEE-227 Electronics Engineering (Course Outline)Dawood AbdullahNo ratings yet

- Cmos Analog Ic Design Course Plan NewDocument9 pagesCmos Analog Ic Design Course Plan Newjim2001No ratings yet

- R22M.Tech - CSE CSSyllabusDocument49 pagesR22M.Tech - CSE CSSyllabuspavansamudralaNo ratings yet

- Obe Curriculum For The Course: RGPV (Diploma Wing) BhopalDocument22 pagesObe Curriculum For The Course: RGPV (Diploma Wing) BhopalHarshit Sahu CS-26No ratings yet

- DLD Lesson PlanDocument3 pagesDLD Lesson Planjy yusufiNo ratings yet

- Department: ECE Staff Name: Logic Design Lab 10ESL38: Course PlanDocument7 pagesDepartment: ECE Staff Name: Logic Design Lab 10ESL38: Course PlansrijaNo ratings yet

- Btech 4th Cem - RemovedDocument15 pagesBtech 4th Cem - Removedroll ringaNo ratings yet

- 20EC1157Document2 pages20EC1157Parthiban VelusamyNo ratings yet

- Cs8501 - Theory of Computation - by DR W T ChembianDocument167 pagesCs8501 - Theory of Computation - by DR W T ChembianClash ClanNo ratings yet

- Digital Design Lab Course Code:-Cse256PDocument38 pagesDigital Design Lab Course Code:-Cse256PYash JaiswalNo ratings yet

- 2.digital ElectronicsDocument9 pages2.digital ElectronicsanupNo ratings yet

- Lab Practice 7Document3 pagesLab Practice 7Angel HernándezNo ratings yet

- Programming in CDocument127 pagesProgramming in CAryan JaanNo ratings yet

- CSE 1004 CSE OBE Computer Architecture LabDocument3 pagesCSE 1004 CSE OBE Computer Architecture LabThe Bong BoyNo ratings yet

- B.tech 3 Cse SyllabusDocument65 pagesB.tech 3 Cse SyllabusVijayendra GoudNo ratings yet

- 15SE205JDocument3 pages15SE205JTarun MittalNo ratings yet

- Experiment 2 - Boolean AlgebraDocument5 pagesExperiment 2 - Boolean AlgebraMustafa MaherNo ratings yet

- r19 Mtech Emb Full-1-9Document9 pagesr19 Mtech Emb Full-1-9saikanna427No ratings yet

- FIRST SEMESTER 2020 - 2021 17-08-2020: Course Handout (Part Ii)Document3 pagesFIRST SEMESTER 2020 - 2021 17-08-2020: Course Handout (Part Ii)Soumil AgarwalNo ratings yet

- Arduino Lab ManualDocument79 pagesArduino Lab Manualkk9015No ratings yet

- The Neumann Problem for the Cauchy-Riemann Complex. (AM-75), Volume 75From EverandThe Neumann Problem for the Cauchy-Riemann Complex. (AM-75), Volume 75Rating: 4 out of 5 stars4/5 (2)

- RectiDocument7 pagesRectiaskj78100% (1)

- ICoT 5200 - 5300 - 5400 Ordering GuideDocument1 pageICoT 5200 - 5300 - 5400 Ordering GuidePeter RhoadsNo ratings yet

- Resume - Shubhanjali Srivastava - Component Dev. - UpdateDocument3 pagesResume - Shubhanjali Srivastava - Component Dev. - Updatesurjitrajput8No ratings yet

- Cover Letter Sample Interpreter JobDocument5 pagesCover Letter Sample Interpreter Jobqwaskmrmd100% (1)

- Lien 2020Document11 pagesLien 2020Puraghan cahya herawanNo ratings yet

- Atlas 3CR12 DatasheetDocument3 pagesAtlas 3CR12 DatasheettridatylNo ratings yet

- Being Aware of Being AwareDocument12 pagesBeing Aware of Being AwareChanchal LNo ratings yet

- Kahn's Light: The Measurable and The Unmeasurable of The Bangladesh National Assembly BuildingDocument14 pagesKahn's Light: The Measurable and The Unmeasurable of The Bangladesh National Assembly BuildingbilibiliNo ratings yet

- QGD 20-50 ManualDocument76 pagesQGD 20-50 Manualnanditos75392No ratings yet

- Reciprocating Compressor Power Calculation Part 2Document6 pagesReciprocating Compressor Power Calculation Part 2Rifka Aisyah0% (1)

- Ms Iso 16120 42008 Non Alloy SteelDocument13 pagesMs Iso 16120 42008 Non Alloy SteelINSTECH Consulting100% (1)

- Full Ebook of The Mediated World A New Approach To Mass Communication and Culture 1St Edition David T Z Mindich Online PDF All ChapterDocument24 pagesFull Ebook of The Mediated World A New Approach To Mass Communication and Culture 1St Edition David T Z Mindich Online PDF All Chapternacidealyani100% (18)

- Vent-O-Mat - Nozzle Check ValveDocument8 pagesVent-O-Mat - Nozzle Check Valvefrankz89No ratings yet

- Transactional Analysis: Greeshma. T S4 MSWDocument42 pagesTransactional Analysis: Greeshma. T S4 MSWSridhar KodaliNo ratings yet

- Ap43 Access Point DatasheetDocument6 pagesAp43 Access Point DatasheetPaisarn UmpornjarassaengNo ratings yet

- Erection Steel Structure ProcedureDocument15 pagesErection Steel Structure ProcedureOussama Sissaoui100% (2)

- Magazine of Concrete ResearchDocument11 pagesMagazine of Concrete ResearchKathlene Lacosta LastimosaNo ratings yet

- Edison Robot BarcodesDocument4 pagesEdison Robot BarcodesethanNo ratings yet

- Act1102 - Cfas - Course SyllabusDocument19 pagesAct1102 - Cfas - Course SyllabusFrancein CequenaNo ratings yet

- Why Nokia FailedDocument4 pagesWhy Nokia FailedNational Star Montessori SchoolNo ratings yet

- Midterm Examination - Entrepreneurial LeadershipDocument5 pagesMidterm Examination - Entrepreneurial LeadershipDINO DIZONNo ratings yet

- Weather and ClimateDocument2 pagesWeather and ClimateLouise GermaineNo ratings yet

- 3D CamDocument16 pages3D CamShin EscaresesNo ratings yet

- A Review of RhomboidityDocument10 pagesA Review of RhomboidityShrey GulatiNo ratings yet

- Environmental Compliance Certificate EccDocument3 pagesEnvironmental Compliance Certificate EccPogi AkoNo ratings yet

- 1st Year Exam (Re-Exam) 1. Årsprøve (Reeksamen) : August 2021Document14 pages1st Year Exam (Re-Exam) 1. Årsprøve (Reeksamen) : August 2021SafridNo ratings yet

- Economics:Presentation On Law of Equi Marginal Utility...Document11 pagesEconomics:Presentation On Law of Equi Marginal Utility...vinay rakshithNo ratings yet

- 6in Double Petal ShellDocument7 pages6in Double Petal ShellOscar PamosNo ratings yet

- Population Control Measures in India Explained PointwiseDocument8 pagesPopulation Control Measures in India Explained PointwiseGAUTAM NATHNo ratings yet

- Research/Capstone Project RubricDocument4 pagesResearch/Capstone Project RubricMark Alvin Jay CarpioNo ratings yet