Professional Documents

Culture Documents

Atom LA-A994P - HP 250 G3, Pavilion 15-R

Atom LA-A994P - HP 250 G3, Pavilion 15-R

Uploaded by

rohit.ydv.8368Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atom LA-A994P - HP 250 G3, Pavilion 15-R

Atom LA-A994P - HP 250 G3, Pavilion 15-R

Uploaded by

rohit.ydv.8368Copyright:

Available Formats

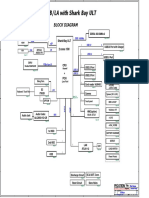

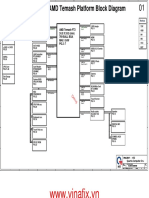

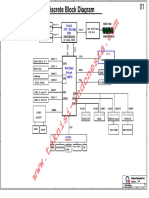

A B C D E

204pin DDRIII-SO-DIMM X1

Memory BUS(DDR3) Single Channel page15

BANK 0, 1, 2

1.35V DDR3L 1333MHz

Digital Display Interfaces (DDI)

1 USB2.0 1

Port 1 Port 0

LVDS Conn. LVDS Translater HDMI Conn. Port 0 Port 1 Port 2 Port 3

page17 RTS2132R page16 page18 USB3.0 USB3.0 USB2.0 USB HUB USB

VGA VALLEYVIEW-M Conn.X1 Conn. FE1.1s(STT) Camera

page24 page24 page25 page17

VGA Conn.

page19

SOC Debug port Port 0 Port 1 Port 2

PCIE USB2.0 WLAN

Touch Screen

Conn. BT Combo

GPP2 GPP1 GPP0 FCBGA 1170 Pin page24 page24 page21

HD Audio(AZ)

10/100

2 Card Reader MINI Card 2

LAN Controller

RTS5239 (WLAN/BT)

page23 RTL8166-CG page6~13

page21 page23

SATA III SATA I

Port 0 Port1

SPI LPC Audio

Card Reader HDD ODD ALC3227

Transformer page20

Conn. Conn. Conn.

page23 RJ45 BIOS (8M) page22 page22

page23

ENE

KBC9012

FAN/LED page26

page28 Int. Speaker Combo Jacks

3 3

Conn. page20 page20

Int.KBD Touch Pad

Sub-borad page27 page27

USB/B

page24

PWR BTN/B

page28

4 4

TP BTN/B Security Classification Compal Secret Data Compal Electronics, Inc.

page27 2012/12/01 2013/07/10 Title

Issued Date Deciphered Date Block Diagrams

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size Document Number Rev

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Custom 0.1

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

LA-A994P

Date: Friday, February 21, 2014 Sheet 2 of 43

A B C D E

A B C D E

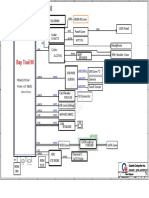

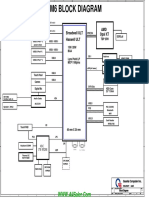

Voltage Rails BOARD ID Table

Power Plane Description S0 S3 S4/S5 USOC1 217@ USOC1 186@

Board ID PCB Revision

VIN 19V Adapter power supply ON ON ON

DB 0.1

BATT+ 12V Battery power supply ON ON ON

SI 0.2 B3 2.17G B3 1.86G

B+ AC or battery power rail for power circuit. (19V/12V) ON ON ON

SA00007E920 SA00007EO10

1

+VSB +VSBP to +VSB always on power rail for sequence control ON ON ON

PV 0.3 1

+RTCVCC RTC Battery Power ON ON ON

MV 1.0 USOC1 CR1@ USOC1 PR1@

+1.0VALW +1.0v Always power rail ON ON ON

+1.2VALW +1.2v Always power rail ON ON ON BOM Option Table

+1.8VALW +1.8v Always power rail ON ON ON BTO Item BOM Structure CeleronR N2815 Dual 7.5W 2C PentiumR N3520 Quad 7.5W 4C

SA00007EO30 SA00007E940

+3VALW +3.3v Always power rail ON ON ON Unpop @

+5VALW +5.0v Always power rail ON ON ON USOC1 CR3@ USOC1 PR3@

Connector CONN@

+1.35V +1.35V power rail for DDR3L ON ON OFF XDP (Debug Port) XDP@

+SOC_VCC Core voltage for SOC ON OFF OFF EMI requirement EMI@

+SOC_VNN GFX voltage for SOC ON OFF OFF EMI requirement unpop @EMI@ CeleronR N2815 Dual 7.5W 2C PentiumR N3520 Quad 7.5W 4C

SA00007EO60 SA00007E950

+0.675VS +0.675V power rail for DDR3L Terminator ON OFF OFF ESD requirement ESD@

+1.0VS +1.0v system power rail ON OFF OFF ESD requirement unpop @ESD@

2 2

+1.05VS +1.05v system power rail ON OFF OFF 8161 LAN controller 8161@

+1.35VS +1.35v system power rail ON OFF OFF 8166 LAN controller 8166@

+1.5VS +1.5v system power rail ON OFF OFF LVDS LVDS@

+1.8VS +1.8v system power rail ON OFF OFF LVDS LDO mode LVDSLDO@

+3VS +3.3v system power rail ON OFF OFF LVDS SWR mode LVDSSWR@

+5VS +5.0v system power rail ON OFF OFF Translator RTS2132S 2132S@

Translator RTS2132R 2132R@

Short Pad RS@

Clean CMOS CMOS@

Note : ON* means that this power plane is ON only with AC power available, otherwise it is OFF. Jump JP@

3 3

EC SM Bus1 address EC SM Bus2 address

Device Address Device Address

Smart Battery 0001 011X b

SOC SM Bus address

Device Address

ChannelA DIMM0 JDIMM1(SPD)

43 level BOM table

A0 1010 000X

43 Level Description BOM Structure

4319P6BOL01 SMT MB AA231 V1UE3 HDMI

4 4

Security Classification Compal Secret Data Compal Electronics, Inc.

2012/12/01 2013/07/10 Title

Issued Date Deciphered Date Notes List

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Size Document Number Rev

B 0.1

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC. LA-A994P

Date: Monday, February 24, 2014 Sheet 3 of 43

A B C D E

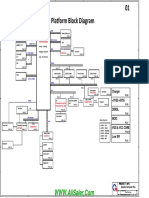

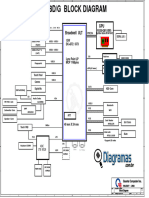

5 4 3 2 1

G3->S0 S0->S3 S3->S0 S0->S5

D D

ACIN

ACIN

+3VLP

+3VLP

EC_ON

EC_ON 1.53ms

+3VALW

+3VALW 1.58ms

+5VALW

+5VALW

SPOK

SPOK 7.28ms

+1.0VALW

+1.0VALW 8.23ms

+1.8VALW

+1.8VALW

ON/OFF

ON/OFF 95.38ms

101ms EC_RSMRST#

EC_RSMRST#

101ms PBTN_OUT#

PBTN_OUT#

102ms

EC_SLP_S4#

C

EC_SLP_S4# C

102ms

EC_SLP_S3#

EC_SLP_S3#

222ms 204ms

SYSON

SYSON 0.6ms

3.29ms

+1.35V

+1.35V 1.71ms

3.29ms

33.68ms DDR_PWROK

DDR_PWROK 21ms 22.32ms 36.20ms

VR_ON

VR_ON 2.49ms 2.50ms

8.85ms 9.81ms

+SOC_VCC

+SOC_VCC 2.50ms 2.50ms

10.55ms 11.5ms

+SOC_VNN

+SOC_VNN 0.28ms 279us

VGATE

VGATE 42.56ms

263ms 11.71ms 5.57ms

SUSP#

SUSP# 31.28us 31.12us

2.56ms 2.18ms

+1.0VS

+1.0VS 1.30ms 1.29ms

1.56ms 1.52ms

+1.05VS

+1.05VS 1.84ms 1.83ms

8ms 8.12ms

+1.35VS

+1.35VS 2.79ms 2.8ms

B 10.71ms 10.71ms B

+1.5VS

+1.5VS 2.11ms 2.08ms

16.59ms 16.63ms

+1.8VS

+1.8VS 3.77ms 3.77ms

15.31ms 15.34ms

+3VS

+3VS 4.41ms 4.41ms

20.48ms 20.27ms

+5VS

+5VS 12.83ms 12.77ms

19.61ms 19.60ms

+0.675VS

+0.675VS 49.83ms 49.87ms

148.3ms

144ms KBRST#

KBRST# 110ms 110ms

11.71ms

PMC_CORE_PWROK

MC_CORE_PWROK 110ms 110ms

11.71ms

DDR_CORE_PWROK

DR_CORE_PWROK 116ms 116ms

584ms 8.8ms SUSP#

PMC_PLTRST#

PMC_PLTRST#

2.38ms

NOTE:

1. T1 and T2 are recommended time for all the VR rails

A A

unless specified otherwise. The VR ramp up time T2 and

subsequent rail delay T3 are put in place to avoid

inrush current which may be caused by multiple loads

turning on simultaneously or fast charging of VR output

decoupling.

2. Platform devices other than SOC sequencing are not

Security Classification Compal Secret Data Compal Electronics, Inc.

2012/12/01 2013/07/10 Title

explicitly shown as they are not limited by the SOC

Issued Date Deciphered Date Power Sequence

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

sequencing requirement. AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D Size Document Number Rev

C 0.1

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC. LA-A994P

Date: Friday, February 21, 2014 Sheet 4 of 43

5 4 3 2 1

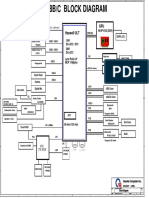

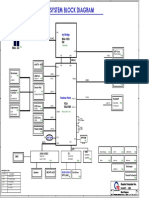

5 4 3 2 1

B+ PU801 +SOC_VCC

AC Adapter PWM +SOC_VNN

ISL95833HRTZ

19V Page. 37

Charger PU301 PU501 +0.675VS

PWM

D

BQ24725ARGRR RT8207MZQW +1.35V D

Page. 32 Page. 34

CHG_B+ +VBATT U37 +1.35VS

MOSFET

DMN3030LSS

Page. 28

BATTERY

8V~12V PU604 +1.0VALW

Regulator

SY8206DQNC

Page. 35

U36 +1.0VS

MOSFET

AO4304L

Page. 28

C PU401 +3VALW C

Regulator

SY8208BQNC

Page. 33

U35 +3VS

MOSFET

DMN3030LSS

Page. 28

PU601 +1.05VS

Regulator

SY8032ABC

Page. 35

PU701 +1.2VALW

Regulator

SY8032ABC

Page. 36

B B

PU703 +1.8VALW

Regulator

SY8033BDBC

Page. 36

U38 +1.8VS

MOSFET

DMN3030LSS

PU402 Page. 28

Regulator +5VALW PU702

SY8208CQNC LDO +1.5VS

APL5930KAI

Page. 33

U33 Page. 36

MOSFET +5VS

DMN3030LSS

Page. 28

A A

Security Classification Compal Secret Data Compal Electronics, Inc.

2012/12/01 2013/07/10 Title

Issued Date Deciphered Date Power Map

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

Size Document Number Rev

B 0.1

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC. LA-A994P

Date: Friday, February 21, 2014 Sheet 5 of 43

5 4 3 2 1

You might also like

- Asus X750LA - X750LB Pegatron X750LB - LA Rev 1.1 СхемаDocument83 pagesAsus X750LA - X750LB Pegatron X750LB - LA Rev 1.1 СхемаYes YesyesNo ratings yet

- MS-14C11 MS-14C1 Rev1.0 PDFDocument56 pagesMS-14C11 MS-14C1 Rev1.0 PDFDurbala IosifNo ratings yet

- Sualaptop365.Edu - VN - Acer Aspire 10 SW5-011 (SW5-012) Pegatron P0JAC2Document49 pagesSualaptop365.Edu - VN - Acer Aspire 10 SW5-011 (SW5-012) Pegatron P0JAC2André Hipnotista100% (8)

- ESP32 Programming for the Internet of Things: JavaScript, AJAX, MQTT and WebSockets SolutionsFrom EverandESP32 Programming for the Internet of Things: JavaScript, AJAX, MQTT and WebSockets SolutionsRating: 5 out of 5 stars5/5 (2)

- NM-A901 Agera-SVT LO Rev1.0 - LENOVODocument37 pagesNM-A901 Agera-SVT LO Rev1.0 - LENOVOCarlos Gomes0% (1)

- Inspiron 3043 DAQF2AMB6A0 Foxglove MB A00 0328Document47 pagesInspiron 3043 DAQF2AMB6A0 Foxglove MB A00 0328Khánh Gia100% (1)

- DA0X81MB6E0Document66 pagesDA0X81MB6E0Asterman SaidiNo ratings yet

- Quanta QK3B 1ADocument33 pagesQuanta QK3B 1ANuno CarvalhoNo ratings yet

- Plunger Pump ManualDocument23 pagesPlunger Pump Manualgovindharajalu75% (4)

- 052 Iczelions - Win32 - Assembly - Tutorials PDFDocument273 pages052 Iczelions - Win32 - Assembly - Tutorials PDFz4rm4rNo ratings yet

- Quanta Ui2h Rev 1b (Acer Aspire z1-621g Aio)Document48 pagesQuanta Ui2h Rev 1b (Acer Aspire z1-621g Aio)Lalu KurniawanNo ratings yet

- Mystique-1 Shark Bay Block Diagram: Project Code: 91.4LY01.001 PCB (Raw Card) : 12298-2Document80 pagesMystique-1 Shark Bay Block Diagram: Project Code: 91.4LY01.001 PCB (Raw Card) : 12298-2Ion PetruscaNo ratings yet

- 0p1 BSW So-Dimm 0308aDocument35 pages0p1 BSW So-Dimm 0308aTomas Arturo Maldonado100% (2)

- HP 14-bs000 Quanta 0P1 DA00P1MB6D0 SchematicsDocument35 pagesHP 14-bs000 Quanta 0P1 DA00P1MB6D0 Schematicsmrdabton100% (1)

- Lenovo X1 Corbon 12298-2Document80 pagesLenovo X1 Corbon 12298-2Ion PetruscaNo ratings yet

- Lenovo g40 45 - Aclu5 Aclu6 NM A281Document60 pagesLenovo g40 45 - Aclu5 Aclu6 NM A281Bersama UkhuwahNo ratings yet

- Qf2a-Dell Inspiron 3043 Aio-Daqf2amb6a0Document47 pagesQf2a-Dell Inspiron 3043 Aio-Daqf2amb6a0Jirawat KusolpredeeNo ratings yet

- New Updated Power On SequenceDocument17 pagesNew Updated Power On SequenceYeri Tagima100% (3)

- Wistron LSZ-2 15202-1 Rev2Document109 pagesWistron LSZ-2 15202-1 Rev2Radosavljevic Milan KissiNo ratings yet

- Lenovo E460 Be460 Nm-A551 Rev1.0Document82 pagesLenovo E460 Be460 Nm-A551 Rev1.0ipod nano16gNo ratings yet

- HP 245 G3 ZSO41 LA-A997P r1.0Document46 pagesHP 245 G3 ZSO41 LA-A997P r1.0Mirgen Miranda100% (2)

- HP ProBook 450 G4 Quanta X63 DA0X83MB6H1 REV H SchematicsDocument67 pagesHP ProBook 450 G4 Quanta X63 DA0X83MB6H1 REV H Schematicsedwar cardenasNo ratings yet

- Compal La-2691 r1.0 SchematicsDocument53 pagesCompal La-2691 r1.0 SchematicsmtorresptNo ratings yet

- Ms-14b1 - Ms-14b11 Ver0c ShematicDocument57 pagesMs-14b1 - Ms-14b11 Ver0c ShematicnorbertoNo ratings yet

- Lenovo Wistron LMQ-2 Mystique-2 13268-1Document79 pagesLenovo Wistron LMQ-2 Mystique-2 13268-1Julio MinaNo ratings yet

- Lenovo Ideapad 120S-14IAP Winbook 120S - MB - V1.0Document63 pagesLenovo Ideapad 120S-14IAP Winbook 120S - MB - V1.0samasca_serbanNo ratings yet

- LenovoIdeapad 120S-14IAPDocument63 pagesLenovoIdeapad 120S-14IAPDiego GallardoNo ratings yet

- LCFC NM-A321 r1.0Document37 pagesLCFC NM-A321 r1.0Ngipik Komp PatiNo ratings yet

- Asus E402na Rev2.0 PDFDocument71 pagesAsus E402na Rev2.0 PDFIlham NurhikmatNo ratings yet

- Compaq Laptop Schematic DiagramDocument35 pagesCompaq Laptop Schematic DiagramErmirio MarquesNo ratings yet

- Lenovo Thinkpad Yoga 900-13isk LCFC Nm-A411 Byg40 Rev1.0 SchematicDocument37 pagesLenovo Thinkpad Yoga 900-13isk LCFC Nm-A411 Byg40 Rev1.0 SchematicMax Repar0% (1)

- 5 6061890504834944285Document52 pages5 6061890504834944285ابو جعفر الحمصيNo ratings yet

- Dell OptiPlex 990 - Dell KATSIKI-USFF RA00 Schematic-1Document72 pagesDell OptiPlex 990 - Dell KATSIKI-USFF RA00 Schematic-1Yared TarikuNo ratings yet

- Acer E5-421 Quanta ZQN DA0ZQNMB6D0 R1aDocument37 pagesAcer E5-421 Quanta ZQN DA0ZQNMB6D0 R1aAdhiezzz GamingNo ratings yet

- NGFF (Key E) : 4GB/8GB DDR4Document81 pagesNGFF (Key E) : 4GB/8GB DDR4kolargol72No ratings yet

- P3449 B01 Concept SchematicsDocument23 pagesP3449 B01 Concept Schematicssrikarbharadwaj0No ratings yet

- Lenovo Thinkpad T570 Wistron LTS-1 16820-1 Rev 1 SchematDocument103 pagesLenovo Thinkpad T570 Wistron LTS-1 16820-1 Rev 1 SchematMichal MíkaNo ratings yet

- Quanta N69 R1aDocument32 pagesQuanta N69 R1aKelvin LimNo ratings yet

- Dell V5470 Dell Vostro 5470 DAJW8CMB8E1 REV E BIOS JW8B - JW8C PDFDocument55 pagesDell V5470 Dell Vostro 5470 DAJW8CMB8E1 REV E BIOS JW8B - JW8C PDFFOX UIONo ratings yet

- Pinebook Mainboard Schematic 1.0Document16 pagesPinebook Mainboard Schematic 1.0Lee MerovíngioNo ratings yet

- Zhra 1aDocument47 pagesZhra 1aWarren DonaldsonNo ratings yet

- Dell Vostro 5470 DAJW8CMB8E1 REV.E PDFDocument55 pagesDell Vostro 5470 DAJW8CMB8E1 REV.E PDFBárbaraNo ratings yet

- Esquema DAJW8CMB8E1 REV. E PDFDocument55 pagesEsquema DAJW8CMB8E1 REV. E PDFTalmoTec100% (1)

- NM-A901 Yoga 910Document37 pagesNM-A901 Yoga 910Martin MarottaNo ratings yet

- Schematic Design Dell-Inspiron-7548-AM6Document58 pagesSchematic Design Dell-Inspiron-7548-AM6Alexis Jonathan Bautista BaqueroNo ratings yet

- OrangePi Lite2 Schematics v2.0Document14 pagesOrangePi Lite2 Schematics v2.0Yuber RaptorazorNo ratings yet

- Quanta Y02 HP MARIO-R1ADocument29 pagesQuanta Y02 HP MARIO-R1AHUBERT GENG SILVA CUBASNo ratings yet

- G41T M7 PDFDocument30 pagesG41T M7 PDFAlex Melo50% (2)

- Dell Vostro 5460 Schematics Version A Quanta Jw8b Jw8c Lapptop SchematicsDocument56 pagesDell Vostro 5460 Schematics Version A Quanta Jw8b Jw8c Lapptop SchematicsCid Patrick HwfNo ratings yet

- Banan Pi BPI-R1 MP Schematic-SD - V3-20140922Document14 pagesBanan Pi BPI-R1 MP Schematic-SD - V3-20140922Tuan AnhNo ratings yet

- Dell Inspiron 15 7000 Series 7547 7548 Quanta AM6 DA0AM6MB8F1 Rev F SchematicsDocument58 pagesDell Inspiron 15 7000 Series 7547 7548 Quanta AM6 DA0AM6MB8F1 Rev F SchematicsSüleyman yavruşahinNo ratings yet

- Quanta JW8D - G Dajw8gmb8c1 RaDocument55 pagesQuanta JW8D - G Dajw8gmb8c1 RaSydney SantosNo ratings yet

- HP Probook 450 g3 Da0x63mb6h1 Revh Quanta x63 R1aDocument67 pagesHP Probook 450 g3 Da0x63mb6h1 Revh Quanta x63 R1aidrissiabdouslmNo ratings yet

- Acer P3 Daee3mb1ae0Document32 pagesAcer P3 Daee3mb1ae0Fixpro Laptop ServiceNo ratings yet

- LH532 Da0fj8mb6f0 - FJ8Document44 pagesLH532 Da0fj8mb6f0 - FJ8oppo cloud007No ratings yet

- Acer Chromebook C740 - Quanta ZHNB DAZHNMB1AD0 RADocument39 pagesAcer Chromebook C740 - Quanta ZHNB DAZHNMB1AD0 RAmike onciucNo ratings yet

- Colour Banding: Exploring the Depths of Computer Vision: Unraveling the Mystery of Colour BandingFrom EverandColour Banding: Exploring the Depths of Computer Vision: Unraveling the Mystery of Colour BandingNo ratings yet

- CompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101From EverandCompTIA A+ CertMike: Prepare. Practice. Pass the Test! Get Certified!: Core 1 Exam 220-1101No ratings yet

- Pasolink Plus ModifiedDocument86 pagesPasolink Plus ModifiedIftikhar Ahmad AhmadNo ratings yet

- Bk51x0en PDFDocument138 pagesBk51x0en PDFLuis LopezNo ratings yet

- Military Full Catalog PDFDocument30 pagesMilitary Full Catalog PDFNicholas MahoneyNo ratings yet

- LT3-00058-2 P6-7-8S ServiceDocument48 pagesLT3-00058-2 P6-7-8S ServiceJorge Andres PozoNo ratings yet

- Basic Computer CourseDocument1 pageBasic Computer CourseMonica SainiNo ratings yet

- MP C2004/MP C2504/MP C2094/MP C2594 Series (D243/D244) Parts CatalogDocument240 pagesMP C2004/MP C2504/MP C2094/MP C2594 Series (D243/D244) Parts CatalogToner DepotNo ratings yet

- GT 610 1GBDocument1 pageGT 610 1GBjohnNo ratings yet

- ER1000 Remote Terminal Unit: ApplicationDocument8 pagesER1000 Remote Terminal Unit: Application1981todurkarNo ratings yet

- HP500 Technical Specifications Instructions TD7 B114 E 05Document4 pagesHP500 Technical Specifications Instructions TD7 B114 E 05Arturo Ramos NuñezNo ratings yet

- Shure 2 Channel MixerDocument6 pagesShure 2 Channel MixerElectra/Off TraxNo ratings yet

- First and Last NamesDocument4 pagesFirst and Last NamesLidijaSpaseskaNo ratings yet

- ManualDocument17 pagesManualGNo ratings yet

- Engineering Utilites: Polytechnic University of The Philippines Sta. Mesa, ManilaDocument13 pagesEngineering Utilites: Polytechnic University of The Philippines Sta. Mesa, ManilaLance Andrew LagmanNo ratings yet

- SSL Certificates For Cisco IOS SSL VPN (2911 Router)Document2 pagesSSL Certificates For Cisco IOS SSL VPN (2911 Router)Cassandra ShafferNo ratings yet

- HOW To Perform A Hardware Independent Restore (HIR)Document22 pagesHOW To Perform A Hardware Independent Restore (HIR)Darren RadonsNo ratings yet

- Unix NohupDocument3 pagesUnix NohupsanyahvNo ratings yet

- Airport Management SystemDocument21 pagesAirport Management SystemSupriya Anand ANo ratings yet

- 4.1.2.9 Resuelto Packet Tracer - Documenting The Network InstructionsDocument3 pages4.1.2.9 Resuelto Packet Tracer - Documenting The Network InstructionsDaniela Alejandra OchoaNo ratings yet

- Verilog A UsersDocument408 pagesVerilog A Usersc_raskumarNo ratings yet

- Project Report On Oregano 8051 (June 2017)Document8 pagesProject Report On Oregano 8051 (June 2017)Talal Khaliq0% (1)

- Installation Manual: PT-Series HDDocument47 pagesInstallation Manual: PT-Series HDFelipe Perez EsquivelNo ratings yet

- WINTEL L2 or L3 Interview QuestionsDocument4 pagesWINTEL L2 or L3 Interview QuestionsStephanie Flores100% (1)

- Cpu Tutorial 2Document53 pagesCpu Tutorial 2rktiwary256034No ratings yet

- DM70 Hand-Held Dewpoint Meter: Accessories: Order CodeDocument1 pageDM70 Hand-Held Dewpoint Meter: Accessories: Order CodeBobNo ratings yet

- Line Follower Robot Using LabVIEWDocument6 pagesLine Follower Robot Using LabVIEWTrần Huy Vinh QuangNo ratings yet

- Aiptek a-HD 1080p Video CameraDocument20 pagesAiptek a-HD 1080p Video Camerajames70094No ratings yet

- 3500 Software Datasheet 141527e PDFDocument3 pages3500 Software Datasheet 141527e PDFSoumen PaulNo ratings yet

- Low Power Consumption Fan San Ace 80 GA Type: 3. Product FeaturesDocument5 pagesLow Power Consumption Fan San Ace 80 GA Type: 3. Product FeaturesDaud Simon ANo ratings yet