Professional Documents

Culture Documents

Wa0006.

Wa0006.

Uploaded by

rohit.ydv.8368Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Wa0006.

Wa0006.

Uploaded by

rohit.ydv.8368Copyright:

Available Formats

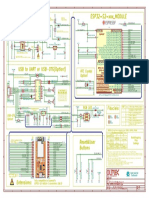

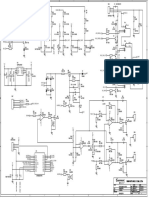

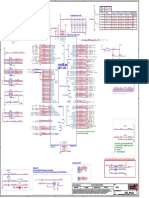

5 4 3 2 1

56

AC IN --> EC LOAD CODE

D D

ACIN

+3VPCU

EC load code finish

+3V_WAKE_ON

DEEP_EC_EN

S5_ON

+3V_WAKE

+3V_S5_DSW

+3V_S5

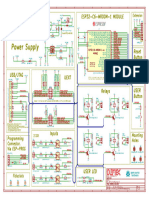

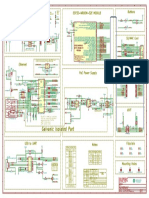

CFL Power-Up Sequencing (G3-->S0-->S3-->S4-->S5)

G3-->S5 Power button on S0-->S3-->S0

+3V_RTC

RTC_RST# tPCH01>9ms=54mS

ACIN

+3VPCU

NBSWON# S0-->G3

S5_ON (from EC)

5ms DC=OFF,AC=ON

(+3V_WAKE) (S5_ON)

(VCCPRIM_3p3) +3V_S5 3.65ms DC=1.0ms,AC OUT=20ms

DC=6.0ms,AC OUT=358ms

DC=10ms,AC

Load EC code form BIOS OUT=253ms 27us

(from +3V_S5 and +5V_S5 PG) the same DC=OFF,AC=ON

3V_5VPGD 10ms time

(S5_ON_2) Reserved VCCPRIM_1P0

(3V_5VPGD)

14.6ms

DC=20ms,AC

C

+1.05V_S5_VCCAMPHYPLL (3V_5VPGD) out=60.2ms C

+1.05V_S5 +1.05V_S5_VCCA_XTAL (3V_5VPGD)

+1.05V_S5_VCCAPLL

1V05S5_PWRGD

RSMRST#(And DSW_PWROK) (from EC, 1V05S5_PWRGD delay 15ms) (tPCH03 >10ms)

T3 15ms (Tu >40ns) 30.8ms

500us

(tPCH02 >10ms)

T4 50ms

AC_PRESENT(from EC,RSMRST# delay 50ms)

tPLT02<90ms

DNBSWON# T6 132ms S0-->S4-->S0 S0-->S5

T5 100ms

(tPCH43-1 >95ms=98ms)

(tPCH43-2 >16ms=132ms)

SLP_S4#(SUSC#) (T09 >30us) 52us 40us (Ta >30us)

SLP_S3#(SUSC#) (T10 >30us) 44us 52us (Tb >30us)

(S4 will be turn off) Note

SUS_ON_2.5V (from EC) T7 5ms 5ms

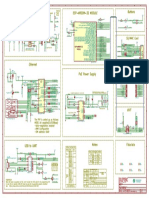

8.6ms

Befor SUS_ON 5ms

(from EC)

SUS_ON 5ms 5ms

(SUS_ON_2.5V+RC) (+3V_S5) (ALL_SYS_PWRGD) 363us 10ms

+2.5V_SUS After +1.2V_SUS

(SUS_ON+RC) (VIN) (ALL_SYS_PWRGD)

+1.2V_SUS

(from EC) 10ms (S3 will be turn off) 11.8ms

20.4ms 9.3ms

6.65ms

RUN_ON

+5V (X) (+5V_S5)

+3V (X) (+3V_S5)

+3V_SSD (X) (+3V_S5)

57.8ms

+1.5V(VDS) (100K+0.1U) (+3V_S5)

+1.2V(VM) (+1.2V_SUS)

+0.95V_VCCIO (X)

(VIN) (ALL_SYS_PWRGD)

B ALL_SYS_PWRGD (from +1.2V_SUS and +2.5V_SUS and VCCIO PG to EC) B

2ms

VR_ON (from EC)

H_VCCST_PWRGD (To CPU)

+0.675V_DDR_VTT (VR_ON)

VR_READY(To EC) 704us

+VCCSA (VR_ON)

5ms

EC_PWROK ( From EC to PCH_PWROK) (tPLT04>1ms)

10ms

VR_SVID_DATA

+VCC_GFX 1.68s

+VCC_CORE

(T14 >99ms)

(T14 99ms)

SYSPWROK (EC to SYS_PWRGD) 1ms

(T20 >2ms)

102.8ms

(0>tPCH33

PLTRST# >99ms)

(To EC) (0>tPCH33

SM_DRAMRST# >99ms)

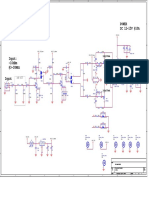

DC mode for GC6

DGPU_PWR_EN (From PCH)

OR FBVDDQ_PD (From FBVDDQ Power GOOD)

1V8_AON_EN

+1.8V_GPU_AON (x) (+3V_S5) (ALL_SYS_PWRGD)

A

After +1.8V_GPU_AON high, the ALL_SYS_PWRGD will high)? A

1V8_MAIN_EN

+1.8V_GPU(1V8_MAIN)

NVVDD

Quanta Computer Inc.

PROJECT : FX506L/FX706L

Size Document Number Rev

POWER UP SEQUENCE 2A

Date: Thursday, March 26, 2020 Sheet 57 of 59

5 4 3 2 1

You might also like

- 16PinBox HW2Document1 page16PinBox HW2Ney AndradeNo ratings yet

- Learning CentOS - A Beginners Gu - Nathan NeilDocument109 pagesLearning CentOS - A Beginners Gu - Nathan NeilDavid Llanes100% (2)

- MAX8774Document1 pageMAX8774Tim O BrienNo ratings yet

- Opencm904 Rev 10 Final SchematicDocument1 pageOpencm904 Rev 10 Final SchematicIvan SutiosoNo ratings yet

- Fas MB V1 2302Document7 pagesFas MB V1 2302RajeshMedidhiNo ratings yet

- MAC 250 Entour SchematicsDocument13 pagesMAC 250 Entour SchematicsThierry MoretNo ratings yet

- Stm32f4 CANDocument1 pageStm32f4 CANkars_jk4943100% (1)

- ESP32 S2 DevKit Lipo - Rev - B1Document1 pageESP32 S2 DevKit Lipo - Rev - B1Inventor TestNo ratings yet

- ESP32-GATEWAY Rev C ColorDocument1 pageESP32-GATEWAY Rev C ColorAlexNo ratings yet

- Lampiran Skematik ArduinoDocument1 pageLampiran Skematik ArduinoRizalfariz HasbiNo ratings yet

- A20 A1高速启动控制板40 035SDocument1 pageA20 A1高速启动控制板40 035S易行胜No ratings yet

- It8586e PDFDocument1 pageIt8586e PDFFacundo TorresNo ratings yet

- Msi Ms-N7y1 r0.1 SchematicsDocument12 pagesMsi Ms-N7y1 r0.1 SchematicsEnzoNo ratings yet

- ESP32-C6-EVB Rev ADocument1 pageESP32-C6-EVB Rev AGhiban ConstantinNo ratings yet

- Kickall V1C SchematicDocument1 pageKickall V1C SchematicJames SpadavecchiaNo ratings yet

- +/-0-15V, 0-1A CV/CC Lab Power Supply: PIQ103 PIU201 PIU3012 PIU3012 PIQ103 PIU201Document1 page+/-0-15V, 0-1A CV/CC Lab Power Supply: PIQ103 PIU201 PIU3012 PIU3012 PIQ103 PIU201marco9991No ratings yet

- Res RP Wdo WP WDI VDDDocument2 pagesRes RP Wdo WP WDI VDDspamail73887No ratings yet

- iAMT EC Strapping Need To Check: For IT8541 PowerDocument1 pageiAMT EC Strapping Need To Check: For IT8541 PowerkasimkaNo ratings yet

- SY8286BDocument1 pageSY8286BSakrie ElsimateNo ratings yet

- Phone K33a42 Schematics L3 RepairDocument35 pagesPhone K33a42 Schematics L3 Repairprashanth handral0% (1)

- QSC rmx2Document1 pageQSC rmx2dorianescalona1No ratings yet

- Esp32-Gateway Rev e ColorDocument1 pageEsp32-Gateway Rev e ColoraaaaNo ratings yet

- Power Supply Buttons Esp-Wroom-32 Module: Lipo ChargerDocument1 pagePower Supply Buttons Esp-Wroom-32 Module: Lipo ChargerSan SadNo ratings yet

- CM-900 REV B Schematic20120906Document1 pageCM-900 REV B Schematic20120906jokowisNo ratings yet

- ESP32-PoE Rev KDocument1 pageESP32-PoE Rev KTamás SzabóNo ratings yet

- ESP32-PoE Rev B2 ColorDocument1 pageESP32-PoE Rev B2 ColorAlexNo ratings yet

- 505 GX3235S-SCH MXL608Document6 pages505 GX3235S-SCH MXL608bbmp302No ratings yet

- RF Amp 2078 SCH V306Document1 pageRF Amp 2078 SCH V306Sanyel Saito100% (2)

- Turbo-Ups Intn'L 640-0218Document1 pageTurbo-Ups Intn'L 640-0218shalkuNo ratings yet

- Micro Inverter Rev01Document9 pagesMicro Inverter Rev01download_cruxNo ratings yet

- Power Input: PDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿDocument16 pagesPower Input: PDF 文件以 "PDF 制作工厂" 试用版创建 ÿÿÿÿ ÿkadirov01No ratings yet

- Fe2 QFP48 V2 0Document1 pageFe2 QFP48 V2 03degreesNo ratings yet

- E360 Schematics Rev20 051201Document9 pagesE360 Schematics Rev20 051201yura19100% (2)

- ESP32 CNCDocument1 pageESP32 CNCDada AndryNo ratings yet

- Lenovo Ideapad 300-15ISK NM-A481Document1 pageLenovo Ideapad 300-15ISK NM-A481Moriel EverNo ratings yet

- ChargerDocument1 pageChargerkhasan.khomilov.84No ratings yet

- Esquema Placa Yup-E STDocument1 pageEsquema Placa Yup-E STMarcio Antonio MachadoNo ratings yet

- L6E PE LW7190R 2 - SemaDocument9 pagesL6E PE LW7190R 2 - SemaSimon StoneNo ratings yet

- Samyung Enc Co.,Ltd.: Front InterfaceDocument1 pageSamyung Enc Co.,Ltd.: Front InterfacejasonelectronicsphilNo ratings yet

- Sanyo DCG-105 Sistema Audio CD-MP3 Manual SimpleDocument11 pagesSanyo DCG-105 Sistema Audio CD-MP3 Manual Simplecharly36No ratings yet

- CB2 1516 CEP0365 OACircuits PDFDocument2 pagesCB2 1516 CEP0365 OACircuits PDFAgila Panneerselvam100% (1)

- ESP32-PoE-ISO Rev KDocument1 pageESP32-PoE-ISO Rev KTamás SzabóNo ratings yet

- Pci-Express Edge Connector: BI INDocument20 pagesPci-Express Edge Connector: BI INLeonel GalliNo ratings yet

- Tidrbe 1Document11 pagesTidrbe 1Om VermaNo ratings yet

- TI MicroInverter SchemeticDocument9 pagesTI MicroInverter Schemeticpuspendu janaNo ratings yet

- PV Input Voltage Sense (Isolated) : C47 0.1u C97 0.1uDocument10 pagesPV Input Voltage Sense (Isolated) : C47 0.1u C97 0.1uPhani ArvapalliNo ratings yet

- ESP32-PoE2 Rev BDocument1 pageESP32-PoE2 Rev Bnathantshama1No ratings yet

- Gigabyte Radeon HD 7770 Gv-R775d5-1gi Gddr5 Rev 0.1Document20 pagesGigabyte Radeon HD 7770 Gv-R775d5-1gi Gddr5 Rev 0.1Ivan Andres Fuentes RamirezNo ratings yet

- Esp32-Poe Rev C ColorDocument1 pageEsp32-Poe Rev C ColorBhupendra SutharNo ratings yet

- DifferentialProbe PDFDocument1 pageDifferentialProbe PDFAlbe CibiaNo ratings yet

- Praise To The Lord The Almighty - 05 - OboeDocument1 pagePraise To The Lord The Almighty - 05 - OboeMichael DiazNo ratings yet

- Datasheet Tarjeta DigiDocument5 pagesDatasheet Tarjeta DigiJhon NogueraNo ratings yet

- IT8586EDocument1 pageIT8586EJivko IvanovNo ratings yet

- DM-3000 Stepper Driver Board SchematicDocument1 pageDM-3000 Stepper Driver Board SchematicJuan De la cruzNo ratings yet

- Power Board Icc20 PDFDocument4 pagesPower Board Icc20 PDFSaber AbidiNo ratings yet

- Schematic Diagram-CompressedDocument10 pagesSchematic Diagram-Compressedhuy bùiNo ratings yet

- TCL 27A71-L LCDDocument2 pagesTCL 27A71-L LCDRicardo DolceNo ratings yet

- There Is A Fountain - Orch - 10 - Trombone 2Document1 pageThere Is A Fountain - Orch - 10 - Trombone 2Rosa PerezNo ratings yet

- 13 12 15Document10 pages13 12 15steven liuNo ratings yet

- Is Dd&co Q1Document1 pageIs Dd&co Q1padmNo ratings yet

- A Beginner's Introduction To Windows PowerShellDocument5 pagesA Beginner's Introduction To Windows PowerShellDavidHauwertNo ratings yet

- AZ 900 DemoDocument12 pagesAZ 900 DemoAdam NIezgudkaNo ratings yet

- USR TCP232 302 User Manual - V1.0.3.01 PDFDocument22 pagesUSR TCP232 302 User Manual - V1.0.3.01 PDFmcgeezer1No ratings yet

- Alfresco - Community Versus EnterpriseDocument18 pagesAlfresco - Community Versus EnterpriseivanpmnNo ratings yet

- Purity Installation QuickGuideDocument5 pagesPurity Installation QuickGuideSamuel PincusNo ratings yet

- CS500 Hardware GuideDocument84 pagesCS500 Hardware GuidesamNo ratings yet

- N4. VLAN & Inter VLAN Step-By-Step Routing ConfigurationDocument7 pagesN4. VLAN & Inter VLAN Step-By-Step Routing ConfigurationMd Saidur Rahman Kohinoor100% (4)

- ECT v3.0.0 User Guide v001Document17 pagesECT v3.0.0 User Guide v001Manches jlNo ratings yet

- RationShop Management SystemDocument7 pagesRationShop Management SystemMohan RajNo ratings yet

- Solution:: 1. Find Subnet Mask and Complement Subnet Mask From The IP Address 175.231.232.116/27Document3 pagesSolution:: 1. Find Subnet Mask and Complement Subnet Mask From The IP Address 175.231.232.116/27Saidur Rahman SidNo ratings yet

- Network Automation Using Ansible For Cisco Routers Basic ConfigurationDocument5 pagesNetwork Automation Using Ansible For Cisco Routers Basic ConfigurationCarlos IsraelNo ratings yet

- Archer C20 (EU&US) 6.0 - DatasheetDocument6 pagesArcher C20 (EU&US) 6.0 - DatasheetjervaiospeniNo ratings yet

- Web Server BasicsDocument2 pagesWeb Server BasicsShadab malik shahNo ratings yet

- Manual Arduino UnoDocument8 pagesManual Arduino UnoNuwando IbrahimaNo ratings yet

- Lab Answer Key - Module 7 - Implementing Domain Name SystemDocument11 pagesLab Answer Key - Module 7 - Implementing Domain Name SystemAndres CarreñoNo ratings yet

- FFDocument30 pagesFFJuan Carlos Quintana CernaqueNo ratings yet

- Figure: Transcoder Free Operation (Trfo)Document5 pagesFigure: Transcoder Free Operation (Trfo)aqahmedNo ratings yet

- 10000004379ea PSI 300 Connection To Automation SystemDocument27 pages10000004379ea PSI 300 Connection To Automation SystemJuan Miguel RodriguezNo ratings yet

- AIX Performance TuningDocument42 pagesAIX Performance Tuningmcfaria20009603No ratings yet

- MoshellPresentation Frank LatestDocument92 pagesMoshellPresentation Frank LatestHai LeNo ratings yet

- Networking ConceptsDocument10 pagesNetworking ConceptsdrosbeastNo ratings yet

- AMTPxxM-Datasheet V1.1 20141216Document30 pagesAMTPxxM-Datasheet V1.1 20141216Mike ThomsonNo ratings yet

- Acer Aspire 5551 Newx5 Pew56Document45 pagesAcer Aspire 5551 Newx5 Pew56nikola1660No ratings yet

- Windows System Administrator Sample ResumeDocument2 pagesWindows System Administrator Sample ResumeDeepak ChouguleNo ratings yet

- Digi Connect DetailsDocument154 pagesDigi Connect DetailsShiva Prasad M PattarNo ratings yet

- Output LogDocument151 pagesOutput LogPotatooo “Potatooo”No ratings yet

- DBMS U4Document13 pagesDBMS U4slogeshwariNo ratings yet