Professional Documents

Culture Documents

MPMC Introduction

MPMC Introduction

Uploaded by

SwamyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

MPMC Introduction

MPMC Introduction

Uploaded by

SwamyCopyright:

Available Formats

MICROPROCESSOR AND MICROCONTROLLER

Mr. Anand H. D.

Department of Electronics & Communication Engineering

Dr. Ambedkar Institute of Technology

Bengaluru-56

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 1

Topics to be covered:

RISC & CISC CPU Architectures

Harvard & Von- Neumann CPU architecture

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 2

Lets look into:

RISC & CISC CPU Architectures

Harvard & Von- Neumann CPU architecture

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 3

RISC & CISC CPU Architectures

RISC Architecture

➢ The term RISC stands for ‘’Reduced Instruction Set Computer’’.

➢ This is a small or reduced set of instructions.

➢ Here, every instruction is expected to attain very small jobs.

➢ In this machine, the instruction sets are modest and simple.

➢ Each instruction is of a similar length; these are wound together to get compound tasks done in a single

operation.

➢ Most commands are completed in one machine cycle. This pipelining is a crucial technique used to speed

up RISC machines.

Characteristics

➢ Pipeline architecture

➢ The number of instructions is restricted as well as decrease

➢ The instructions like load as well as store have right of entry to memory

➢ Addressing modes are less

➢ Instruction is uniform and its format can be simplified

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 4

RISC & CISC CPU Architectures

Advantages:

➢ The performance of this processor is good because of the easy & limited no. of the

instruction set.

➢ This processor uses several transistors in the design and cheaper.

➢ it can finish its task within a single clock cycle.

Disadvantages:

➢ The performance of this processor may change based on the executed code because

the next commands may depend on the earlier instruction for their implementation

within a cycle.

➢ The complex instruction is frequently used by the compilers and programmers

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 5

RISC & CISC CPU Architectures

CISC Architecture

➢ The term CISC stands for ‘’Complex Instruction Set Computer’’.

➢ It is a CPU design plan based on single commands, which are skilled in executing multi-step

operations.

➢ CISC computers have small programs.

➢ It has a huge number of compound instructions, which takes a long time to perform.

➢ Maximum instructions are finished in two to ten machine cycles. In CISC, instruction pipelining is

not easily implemented.

Characteristics

➢ CISC may take more time to execute the code as compared with an only clock cycle.

➢ CISC supports high-level languages for simple compilation and complex data structure.

➢ It is collected with more addressing modes, fewer registers normally from 5 to 20.

➢ For writing an application, less instruction is required. The code length is very short, so it needs

extremely small RAM.

➢ Instructions are larger as compared with a single word.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 6

RISC & CISC CPU Architectures

Advantages:

➢ In the CISC processor, the compiler needs a small effort to change the program or

statement from high-level to assembly otherwise machine language.

➢ A single instruction can be executed by using different low-level tasks

➢ It doesn’t use much memory due to a short length of code.

➢ CISC utilizes less instruction set to execute the same instruction as the RISC.

➢ The instruction can be stored within RAM on every CISC

Disadvantages:

➢ As compared with the RISC processor, CISC processors are very slow while executing

every instruction cycle on every program.

➢ The pipeline execution within the CISC will make it difficult to use.

➢ The machine performance reduces because of the low speed of the clock.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 7

RISC & CISC CPU Architectures

RISC CISC

RISC stands for Reduced Instruction Set CISC stands for Complex Instruction Set

Computer. Computer.

RISC processors have simple instructions CSIC processor has complex instructions

taking about one clock cycle. that take up multiple clocks for execution.

Performance is optimized with more focus Performance is optimized with more focus

on software on hardware.

The instruction set is reduced i.e. it has The instruction set has a variety of different

only a few instructions in the instruction instructions that can be used for complex

set. Many of these instructions are very operations.

primitive.

Complex addressing modes are synthesized CISC already supports complex addressing

using the software. modes

Multiple register sets are present Only has a single register set

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 8

RISC & CISC CPU Architectures

RISC CISC

RISC processors are highly pipelined They are normally not pipelined or less

pipelined

Execution time is very less Execution time is very high

Code expansion can be a problem Code expansion is not a problem

The decoding of instructions is simple. It requires external memory for

calculations

The most common RISC microprocessors Examples of CISC processors are the

are Alpha, ARC, ARM, AVR, MIPS, PA- System/360, VAX, PDP-11, Motorola

RISC, PIC, Power Architecture, and 68000 family, AMD, and Intel x86 CPUs.

SPARC.

RISC architecture is used in high-end CISC architecture is used in low-end

applications such as video processing, applications such as security systems,

telecommunications, and image home automation, etc

processing.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 9

Lets look into:

RISC & CISC CPU Architectures

Harvard & Von- Neumann CPU architecture

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 10

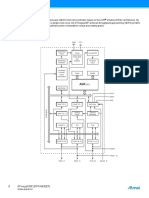

Harvard & Von- Neumann CPU architecture

Von Neumann Architecture:

➢ Von Neumann Architecture is a digital

computer architecture whose design is

based on the concept of stored program

computers where program and data are

stored in the same memory.

➢ This architecture was designed by the

famous mathematician and physicist John

Von Neumann in 1945.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 11

Harvard & Von- Neumann CPU architecture

Harvard Architecture:

➢ Harvard Architecture is the digital

computer architecture whose design is

based on the concept where there are

separate storage and separate buses (signal

path) for instruction and data.

➢ It was basically developed to overcome

the bottleneck of Von Neumann

Architecture.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 12

Harvard & Von- Neumann CPU architecture

VON NEUMANN ARCHITECTURE HARVARD ARCHITECTURE

It is ancient computer architecture based on It is modern computer architecture based on

stored program computer concept. Harvard Mark I relay based model.

Same physical memory address is used for Separate physical memory address is used for

instructions and data. instructions and data.

There is common bus for data and instruction Separate buses are used for transferring data

transfer. and instruction.

The decoding of instructions is simple. It requires external memory for calculations

It is cheaper in cost. It is costly than Von Neumann Architecture..

CPU can not access instructions and read/write CPU can access instructions and read/write at

at the same time. the same time

It is used in personal computers and small It is used in micro controllers and signal

computers. processing.

MICROPROCESSOR AND MICROCONTROLLER: INTRODUCTION

Prepared by Prof. Anand H. D., Dept. of ECE, Dr. AIT, Bengaluru-56 13

Thank You

Prof. Anand H. D.

M. Tech. (PhD.)

Assistant Professor,

Department of Electronics & Communication Engineering

Dr. Ambedkar Institute of Technology, Bengaluru-56

Email: anandanihd@gmail.com

Phone: 9844518832

14

You might also like

- Fa19 Bee 007, Fa19 Bee 047, Fa19 Bee 107, Fa19 Bee 118Document14 pagesFa19 Bee 007, Fa19 Bee 047, Fa19 Bee 107, Fa19 Bee 118danyalNo ratings yet

- Difference Between RISC and CISC ArchitectureDocument2 pagesDifference Between RISC and CISC ArchitectureakssahaNo ratings yet

- ES Unit-2Document28 pagesES Unit-2palaji pradeepNo ratings yet

- Session - 26 CISC and RISCDocument15 pagesSession - 26 CISC and RISCArnoldNo ratings yet

- Risc A Cisc PDocument10 pagesRisc A Cisc PAlexander KirosNo ratings yet

- Comparison of CISC Vs RISC Architectures 3.1.9Document5 pagesComparison of CISC Vs RISC Architectures 3.1.9fovov27364No ratings yet

- RISC and CISC - Eugene ClewlowDocument17 pagesRISC and CISC - Eugene Clewlowilg1No ratings yet

- Risc and Cisc: by Eugene ClewlowDocument17 pagesRisc and Cisc: by Eugene ClewlowRamnath PraveenNo ratings yet

- Risc and Cisc: by Eugene ClewlowDocument17 pagesRisc and Cisc: by Eugene ClewlowSampathhhhh Sai TadepalliNo ratings yet

- Risc and Cisc: Computer ArchitectureDocument17 pagesRisc and Cisc: Computer Architecturedress dressNo ratings yet

- CSC 315 PDF 1Document7 pagesCSC 315 PDF 1abdulwasiuwaris4No ratings yet

- Risc and Cisc: By: Farheen Masood Sania ShahzadDocument17 pagesRisc and Cisc: By: Farheen Masood Sania ShahzadAlia BashirNo ratings yet

- MCES-21CS43 Module-1 NotesDocument14 pagesMCES-21CS43 Module-1 NotesEdu techNo ratings yet

- Coa 9Document4 pagesCoa 9adadaNo ratings yet

- Risc and Cisc Processors: by Chimi DorjiDocument9 pagesRisc and Cisc Processors: by Chimi DorjiChencho DorjiNo ratings yet

- Risc and Cisc CasestudyDocument5 pagesRisc and Cisc CasestudyJAy ShahNo ratings yet

- Chapter 2 - Lecture 6 Risc vs. CiscDocument7 pagesChapter 2 - Lecture 6 Risc vs. CiscAlazar DInberuNo ratings yet

- (Computer Architecture CIA-3) : (By: Nikhil Kumar Yadav) (Roll. No.: 1847241) (Date of Submission: 06-09-2019)Document8 pages(Computer Architecture CIA-3) : (By: Nikhil Kumar Yadav) (Roll. No.: 1847241) (Date of Submission: 06-09-2019)NIKHIL KUMAR YADAV 1847241No ratings yet

- 5-Harvard Architecture - CISC & RISC Architectures-10!01!2024Document18 pages5-Harvard Architecture - CISC & RISC Architectures-10!01!2024shashank.reddy5804No ratings yet

- Assignment 1 SolutionDocument4 pagesAssignment 1 SolutionVirang PatelNo ratings yet

- Risc and CiscDocument17 pagesRisc and CiscAyazNo ratings yet

- Advanced Computer Architecture 1 1Document118 pagesAdvanced Computer Architecture 1 1SharathMenonNo ratings yet

- Risc and CiscDocument20 pagesRisc and Ciscprathapreddy420No ratings yet

- MC Module Questions With Key AnswersDocument15 pagesMC Module Questions With Key Answersrahulsda864No ratings yet

- Task 5Document3 pagesTask 5Fajri RahmanNo ratings yet

- Cisc ProcessorsDocument8 pagesCisc Processorsjjba93No ratings yet

- CISC Is An Acronym For Complex Instruction Set ComputerDocument44 pagesCISC Is An Acronym For Complex Instruction Set ComputerVantharAlaNo ratings yet

- Risc Cisc in Microcontroller and MicroprocessorDocument31 pagesRisc Cisc in Microcontroller and Microprocessormanvir kaurNo ratings yet

- 3-RISC ArchitectureDocument13 pages3-RISC Architectureafzal_a100% (1)

- Sr. No. Key Computer Architecture Computer OrganizationDocument11 pagesSr. No. Key Computer Architecture Computer OrganizationKashif ZamanNo ratings yet

- Risc Vs CiscDocument8 pagesRisc Vs CiscSameer SalamNo ratings yet

- Cisc and Risc NotesDocument3 pagesCisc and Risc NoteskavitaNo ratings yet

- Computer Architecture Assignment 1Document4 pagesComputer Architecture Assignment 1Emilia KullutweNo ratings yet

- Computer Architecture Unit-II by Khalid Amin AkhoonDocument19 pagesComputer Architecture Unit-II by Khalid Amin AkhoonNikita SabaleNo ratings yet

- Introduction To Computer Organization1-1-18Document18 pagesIntroduction To Computer Organization1-1-18Manisha MeenaNo ratings yet

- 04 Microprocessor Systems Lecture No 04 RISC ArchitectureDocument14 pages04 Microprocessor Systems Lecture No 04 RISC ArchitectureMuhammad ZubairNo ratings yet

- Structure of Computer SystemsDocument16 pagesStructure of Computer SystemsMussie KebedeNo ratings yet

- Microprocessors and Microcontrollers: Lecture-03Document9 pagesMicroprocessors and Microcontrollers: Lecture-03Ahmed ElshenawyNo ratings yet

- Binder 1Document46 pagesBinder 1Hemalatha K.N.No ratings yet

- 3.3.5 Reduced Instruction Set Computing Processors (RISC)Document11 pages3.3.5 Reduced Instruction Set Computing Processors (RISC)Rahil SarwarNo ratings yet

- Risc CiscDocument4 pagesRisc CiscSuraj PulamiNo ratings yet

- 1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Document63 pages1-Introduction 1.0 Motivation: Which Is Like A"blueprint" For Building The Machine)Manikanta Raja MedapatiNo ratings yet

- Difference Between Von Neumann and Harvard ArchitectureDocument6 pagesDifference Between Von Neumann and Harvard ArchitectureSuraj KhatalNo ratings yet

- Comparative Study of RISC AND CISC ArchitecturesDocument4 pagesComparative Study of RISC AND CISC ArchitecturesATSNo ratings yet

- Difference Between RISC and CISC Architectures and Its ApplicationsDocument10 pagesDifference Between RISC and CISC Architectures and Its ApplicationsAnonymous U8awvgZ3pDNo ratings yet

- Instruction Set ArchitectureDocument4 pagesInstruction Set ArchitectureashuNo ratings yet

- 11-CISC & RISC Architectures-11-01-2024Document7 pages11-CISC & RISC Architectures-11-01-2024ayuommishraNo ratings yet

- Difference Between Risc and Cisc Processor Gate Notes 79Document2 pagesDifference Between Risc and Cisc Processor Gate Notes 79haiqaabbas793No ratings yet

- CA Lecture 10 1Document5 pagesCA Lecture 10 1kalimNo ratings yet

- Computer Architect AssignmentDocument2 pagesComputer Architect AssignmentINAMNo ratings yet

- Cisc RiscDocument4 pagesCisc RiscRohini JosephNo ratings yet

- Chapter 07 RISCDocument62 pagesChapter 07 RISCBinod SAdhikariNo ratings yet

- Presentation RISC Vs CISCDocument13 pagesPresentation RISC Vs CISCafaakiNo ratings yet

- RISC Vs CISCDocument13 pagesRISC Vs CISCBehin SamNo ratings yet

- Fa20-Bcs-030 Mal A1Document6 pagesFa20-Bcs-030 Mal A1Waleed IlyasNo ratings yet

- MM Assignment 1 AnsDocument18 pagesMM Assignment 1 Ansys013330No ratings yet

- What Is RISC and CISC Architecture - EdgefxkitsDocument11 pagesWhat Is RISC and CISC Architecture - EdgefxkitsjeyasuthanjNo ratings yet

- C Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingFrom EverandC Programming for the PIC Microcontroller: Demystify Coding with Embedded ProgrammingNo ratings yet

- Intermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingFrom EverandIntermediate C Programming for the PIC Microcontroller: Simplifying Embedded ProgrammingNo ratings yet

- Computer& Laptop MasterDocument148 pagesComputer& Laptop MasterVikas SharmaNo ratings yet

- Debug 1214Document23 pagesDebug 1214Linh Lê Hồng DiệuNo ratings yet

- Log Book A4Document3 pagesLog Book A4api-352177591No ratings yet

- Industrial TrainingDocument14 pagesIndustrial TrainingAbhay SharmaNo ratings yet

- Microprocessor Experiment No.: 1 Use of Programming Tools Microprocessor Lab Experiment No.: 1 Use of Programming ToolsDocument8 pagesMicroprocessor Experiment No.: 1 Use of Programming Tools Microprocessor Lab Experiment No.: 1 Use of Programming ToolsrachanaypatilNo ratings yet

- Comsale Inventory Canada 20191107Document231 pagesComsale Inventory Canada 20191107Mahesh SkyzzNo ratings yet

- History of Information Systems TimelineDocument1 pageHistory of Information Systems TimelineKathleen BorjaNo ratings yet

- PSCAD Compatibility Charts V5Document18 pagesPSCAD Compatibility Charts V5windreader1No ratings yet

- Exam Circular. FH Summer April May 2022Document6 pagesExam Circular. FH Summer April May 2022Jeet SaveNo ratings yet

- Eprom Service BoschDocument5 pagesEprom Service BoschRick Castillo0% (1)

- Figure 2-1. Block DiagramDocument1 pageFigure 2-1. Block DiagramsalarNo ratings yet

- Category - ESP8266 Code Guide - ElectroDragonDocument3 pagesCategory - ESP8266 Code Guide - ElectroDragonJohn GreenNo ratings yet

- Account Statement As of 04-05-2020 19:48:27 GMT +0530Document11 pagesAccount Statement As of 04-05-2020 19:48:27 GMT +0530সোমনাথ মহাপাত্রNo ratings yet

- Classification of Computer WorksheetDocument3 pagesClassification of Computer Worksheetge5100% (1)

- HP EliteBook 855 G8 Parts LocatorDocument35 pagesHP EliteBook 855 G8 Parts LocatorArarat VardanyanNo ratings yet

- Debug 1214Document16 pagesDebug 1214Rizal MustofaNo ratings yet

- 8254: Programmable Interval Timer: Salient FeaturesDocument8 pages8254: Programmable Interval Timer: Salient Featureskannansuresh871376No ratings yet

- List of Supported Oracle Hardware (With Last Ship Dates Announced)Document16 pagesList of Supported Oracle Hardware (With Last Ship Dates Announced)Mikel RichieNo ratings yet

- Bios Beep CodesDocument6 pagesBios Beep CodesttrtNo ratings yet

- Introduction To AVR Microcontrollers: College of EngineeringDocument33 pagesIntroduction To AVR Microcontrollers: College of EngineeringAbdulla AshoorNo ratings yet

- 18EC46 Question BankDocument1 page18EC46 Question Bankdinesh M.A.100% (1)

- Bally MPU Compatibility Matrix v17Document3 pagesBally MPU Compatibility Matrix v17lzxpokemongoNo ratings yet

- GT-I9300 BRICKED UnBrickDocument9 pagesGT-I9300 BRICKED UnBrickIvan PušićNo ratings yet

- Classification of ComputerDocument11 pagesClassification of ComputerAjay KumarNo ratings yet

- College Arduino ProjectDocument22 pagesCollege Arduino ProjectAnurag DasNo ratings yet

- CHS Final Examination Answer KeyDocument2 pagesCHS Final Examination Answer Keyjoel lacayNo ratings yet

- MinaTool - Bypass MEID - NoMEID Iphone 5s To X Support To IOS 16.xDocument4 pagesMinaTool - Bypass MEID - NoMEID Iphone 5s To X Support To IOS 16.xYohan RodriguezNo ratings yet

- Assignment Q2 ESD MELZG526 2019HT80542Document8 pagesAssignment Q2 ESD MELZG526 2019HT80542Rahamtulla MohammadNo ratings yet

- Computing Cloze Notes Lesson 1Document3 pagesComputing Cloze Notes Lesson 1Toric BlockerNo ratings yet