Professional Documents

Culture Documents

Design and Implementation of 64-Bit SRAM and CAM o

Design and Implementation of 64-Bit SRAM and CAM o

Uploaded by

Lê TuấnCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Design and Implementation of 64-Bit SRAM and CAM o

Design and Implementation of 64-Bit SRAM and CAM o

Uploaded by

Lê TuấnCopyright:

Available Formats

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/353249027

Design and Implementation of 64-bit SRAM and CAM on Cadence and Open-

source environment

Article in International Journal of Circuits Systems and Signal Processing · July 2021

DOI: 10.46300/9106.2021.15.65

CITATIONS READS

3 1,389

4 authors:

Shylashree Nn Yatish D Vahvale

Rashtreeya Vidyalaya College of Engineering Rashtreeya Vidyalaya College of Engineering

49 PUBLICATIONS 141 CITATIONS 3 PUBLICATIONS 4 CITATIONS

SEE PROFILE SEE PROFILE

N. Praveena A. S. Mamatha

4 PUBLICATIONS 7 CITATIONS

St. Joseph Engineering College

3 PUBLICATIONS 5 CITATIONS

SEE PROFILE

SEE PROFILE

All content following this page was uploaded by Yatish D Vahvale on 08 September 2021.

The user has requested enhancement of the downloaded file.

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

Design and Implementation of 64-bit SRAM and

CAM on Cadence and Open-source environment

N. Shylashree1, Yatish D. Vahvale2, N. Praveena3, A. S. Mamatha4

1

Department of Electronics and communication Engineering, RV College of Engineering, Bengaluru, India.

2

Department of Electronics and communication Engineering, RV College of Engineering, Bengaluru, India

3

Department of Electronics and communication Engineering, RV College of Engineering, Bengaluru -560059 and affiliated to

VTU, Belagavi, Karnataka, India.

4

Department of Electronics & Communication Engineering, St.Joseph Engineering College, Mangaluru-5750 28, India.

Revised: May 27, 2021. Revised: July 5, 2021. Accepted: July 8, 2021. Published: July 14, 2021.

Abstract— Low-power IC design has become a priority in Large integrated storage is required for image processing and

recent years because of the growing proliferation of portable other multimedia applications. Approximate memory has

battery-operated devices, bringing Static Random-Access been proposed as a possible energy-efficient solution for

Memory (SRAM) and Content Addressable Memory (CAM) such error-tolerant applications in some previous studies.

into play. In today's SoCs, embedded SRAM units have When compared to normal 6-T SRAM cells with the same

become a necessary component. There is a lack of chips in the bit error rate, a single-ended 6-T (SE6T) static random-

current world and to manufacture chips there is the access memory (SRAM) cell has around 50% less dynamic

requirement of Electronic Design Automation(EDA) tools that power[1]. In the XNOR-SRAM bitcell, the ternary XNOR

can perform better. In this paper, the main motive is to

operations are accumulated on the read bit line (RBL) by

showcase the performance of open-source tools available

currently which can still generate the required output with no

turning on all 256 rows at the same time, resulting in a

cost. In this new era of fast mobile computing, traditional resistive voltage divider. The analog RBL voltage is digitized

SRAM cell designs are power-demanding and by a column-multiplexed 11-level flash analog-to-digital

underperforming. Rather than lowering manufacturing costs converter (ADC) at the XNOR-SRAM peripheral[2]. Yosys

through high-volume production, specialty memory give cost- for Verilog synthesis and nextpnr for placement, routing, and

effective alternatives through architecture. Specialty memory bitstream generation is introduced in the [3] paper as a fully

devices enable the designer to address issues like board area, free and open-source software (FOSS) architecture-neutral

important timing, data flow bottlenecks, and so on in ways that FPGA framework. A novel task-based parallel incremental

high-volume regular memory devices cannot. Implementation timing analysis engine to overcome the performance

of memory devices on Cadence environment and open-source bottleneck of traditional loop-based methods, a new

environment to check the compatibility and compare the application programming interface (API) approach to utilize

power, area, and delay of both 64-bit SRAM and CAM also high degrees of parallelism, and improved support for

analysing and validating the results of both the memory industry-standard design formats to increase user experience

devices in this paper. For SRAM in a cadence environment, the [4]. The high dynamic power consumption associated with

calculated power, area, and slack have improved values, traditional CAM design's massive and active parallel

namely 0.145mW, 1104.3µm2, and positive slack of 6636 for hardware has long been a problem. However, with multigate

pre-layout analysis. Furthermore, the power for 64-bit CAM in devices replacing planar MOSFETs, deeply scaled

a cadence context is nearly identical to those for an open-

technology nodes are projected to provide additional

source environment ~0.8mW. In an open-source environment,

the calculated slack for CAM is 4.74.

tradeoffs to CAM design [5-8]. By increasing the ratio to 4,

read stability is improved, and write stability is improved by

Keywords—Yosys, OpenSta, genus, Graywolf, innovus, charging and discharging the storage node using two

qflow tool transistors. The proposed 8T SRAM architecture is compared

to standard 6T, decoupled 8T, and 10T SRAM cells. To

write data into a cell at 1.2V supply voltage, a 6T SRAM cell

I. INTRODUCTION required 584.1mV word line voltage, but the suggested

Computer memory refers to any physical device capable SRAM cell requires just only 512mV [9]. The suggested

of temporarily storing information, such as RAM (random placement tool [10] begins by running a cutting-edge CMOS

access memory), or permanently storing information, such as placer, which arranges rows of fixed-height but variable-

ROM (read-only memory) (read-only memory). Memory width cells on the chip. Each row's cells are then clustered

devices use integrated circuits (ICs), which are used by together in groups of at least k cells with the same logic

operating systems, software, and hardware. A CAM is a level. Increasing k reduces chip area while also potentially

memory that implements the lookup-table function in a lowering performance. Place-and-route results of a 32-bit

single clock cycle using dedicated comparison circuitry. Kogge-Stone [10] adder for various values of k is provided

CAMs are often found in network routers for packet to evaluate the effectiveness of the suggested methodology.

forwarding and categorization, but they can also be found in When compared to the results of a standard CMOS

a wide range of other applications that require quick table placement with an H-tree clock net, the overall chip size can

searching. The key CAM design problem is to limit the be decreased by 27% employing this innovative design

amount of power consumed by the vast quantity of parallel process. Because of its parallel search accessibility, content

active circuitry without losing speed or memory density. addressable memory (CAM) is one of the most promising

E-ISSN: 1998-4464 586

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

HSEs. However, it suffers from significant dissipation, III. METHODOLOGY

which is exacerbated when several components, such as cells Before implementing the tool, it is of prime importance

and accompanying match lines (MLs), are accessed during to first understand the methodology of the design movement

each search [11-14]. A ternary content-addressable memory from Verilog code to generating synthesized netlist and then

(TCAM) cell with 12 transistors and two magnetic tunneling from the .sdc file to control the timing parameters. Finally,

junctions (MTJs) is presented. The suggested TCAM cell generating gds2 on both the environment. In the previous

consumes no static power during the search process, section, the learning about SRAM and CAM and also the

resulting in a very energy-efficient operation. The resistance tools used in both the environments is done. This section

of an MTJ in the anti-parallel state is compared to that of an demonstration of a better methodology of looking into the

MTJ in the parallel state for search operations [15-17]. flow of the project.

papers [18-20] discuss the implementation of memory

devices and their reaction to internal noise. In the paper [20- The process of converting a design into manufacturable

22] the authors discuss the various techniques used and the geometry is known as physical design. Floorplanning,

basic memory-based explanations required to understand the placement, clock tree synthesis, and routing are among the

GDS flow. The ASIC understanding and its flow has been steps involved. The physical design process begins with the

clearly explained in [23-25] these explanations have been creation of a netlist from RTL. The netlist is a diagram that

used in this project. Based on the above analysis and shows how a circuit's components are connected. The first

understanding, the project has been implemented and and most important stage is to plan the layout of the space. It

exploring of new open-source tools is done. entails determining which buildings should be put next to

one another while taking into account space constraints,

Through the continuous review of different journals and speed, and the numerous constraints imposed by

papers, concluding the behavior of memory architectures in components. Figure 1 shows the flow chart for generating

not yet been explored on open-source tools. So, the GDSII in a cadence environment. Figure 2 shows the flow

comparison can be done on cadence environment and open- chart for generating GDSII in an open-source environment.

source environment. The final values are to be expected to The open-source tool “qrourter” is used for the placement

have almost nearest value with respect to each other. This and detailed routing of the cells. To have a proper layout the

validation of the resulting power, area and delay of memory tool used is “magic”.

device on open-source environment is the new approach to

view the results in a perspective of VLSI EDA tools.

Design.v Nclaunch Functional

II. VLSI TOOLS testbench tool verificatio

.v n

A. Open source VLSI tools

First, the different open source tools available in the

market for generating gds2 files from scratch are yosys,

magic, gray wolf, qflow, and openSta to calculate the timing, .v .lib .sdc Genus Synthesis

area, and power parameters. The magic tool is used for the script.tcl tool for the

placement of the cells also qrouter is to route the cell nets to netlist.v design

connect to different parts of the design. The qflow is used to

process different backend aspects of design to generate a

gds2 file. These are the tools used to produce gds2 for

memory design CAM and SRAM.

.lef, Innovus Generating

B. Cadence environment for the development of the design .lib,.sdc,i tool gds2

o

Cadence's toolkit includes several programs for a variety

of tasks, including schematic sketching, layout, verification,

and simulation. These programs work on a variety of Fig. 1. The flow of cadence environment to generate gds2 from design.

computer platforms. The open architecture also enables the

incorporation of third-party or custom-built solutions. An The “open timer” tool is utilized for the final timing

application named Design Framework II is responsible for analysis; this tool uses C++ programming because it is an

integrating all of these tools (DFW). The layout is created object-oriented technique to solve highly complex numerical

using the Virtuoso Layout Editor. A layout is made up of problems. In a cadence set, the blocks above illustrate the

geometrical figures in various colors. It is then feasible to basic flow of code to the final GDS II of digital design. The

generate the final mask layers that are employed in the Nclaunch tool is used to verify the functionality of a Verilog

production of the design based on the size and color of these code with the DUT and testbench as inputs. The Genus tool

figures. Other cells can be included by instantiating their is used to build a netlist from a design, whereas Innovus is

layout views. PNR is the final stage in constructing a huge used to build a final GDS II file. “Yosys” tool is used to

design. This is when all of the chip's various components are verify the code, “BliFanout" is used for synthesis, Graywolf

positioned in their proper locations and connected. Because a is used for placement as shown in fig 2. A chip is partitioned

design can easily have hundreds of connection points, into functional blocks. The location of each component or

manually connecting them would be difficult and time- block on the die is determined by placement, which takes

consuming. The designer may also want to experiment with into account timing and connection length. Inserting buffers

other layouts for the components, output buffers, memory or inverters into a clock tree allows the clock to be

structures, amplifiers, and so on. distributed equally across consecutive parts in a design while

minimizing skew and latency. The different tools used in the

E-ISSN: 1998-4464 587

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

cadence environment are as shown in fig 1 i.e., genus and to discover a mistake than simulation. Interconnect

Innovus tools. The genus tool takes few files such as the pathways, including conventional cell and macro pins, are

Verilog design file, testbench file, constraint files to generate determined by routing. This stage completes all of the

synthesis files. This generated netlist from synthesis is then connections defined in the netlist in the most efficient and

used in the physical design of SRAM and CAM. The time-constrained manner possible. GDSII, a data format that

generated constraints file from synthesis is also used to clock represents layout information, is usually the final result of

constraint and liberty files and the lef file is used for floor the physical design process. Qrouter is a VLSI fabrication

planning and power planning. From the obtained files from tool that generates metal layers and vias to physically

synthesis and physical design to calculate area, power, and

connect a netlist. It's a maze router, sometimes known as a

timing report. The available open-source tools Icarus Verilog

"sea-of-gates" router or an "over-the-cell" router. That is,

is a simulation and synthesis tool for Verilog. It functions as

a compiler, converting Verilog (IEEE-1364) source code to a unlike a channel router, it starts with a description of where

target format. The compiler can generate an intermediate standard cells should be located, usually at the smallest

form called vvp assembly for batch simulation. The vvp possible spacing, and then builds metal routes over the

command is used to execute this intermediate form. The standard cells.

compiler generates netlists in the desired format for

synthesis. Magic is a VLSI layout tool with a long history. IV. IMPLEMENTATION ON VLSI ENVIRONMENT

Universities and small businesses continue to use Magic

VLSI. Even for folks who eventually rely on commercial A. 64-bit SRAM on cadence environment

tools for their product design flow, Magic is frequently rated

as the easiest tool to use for circuit designing. Netgen is a In this section, the discussion about the implementation

program that compares netlists, a process known as LVS of 64-bit SRAM in a cadence environment. Fig 3 shows the

(Layout vs. Schematic). generated netlist for SRAM on the genus tool of cadence

environment. The connection of the input registers to the

internal flip flops and LUT (lookup table) of the design is

Design.v and done in the netlist. The netlist contains details such as the

Yosys testbench.v number of inputs, outputs and intermediate gates, and flip

flops that are used to produce the functionality of the desired

design. Similarly, the design on the backend has been

continued on the innovus tool.

Synthesis of

BlifFanout code

Placement of

Graywolf cells

Qrouter and Routing and

magic layout tool

Timing

analysis

OpenSta (slack)

Fig. 2. Flow chart of generating gds2 from open-source VLSI tools for

both SRAM and CAM

Fig. 3. Generated netlist of 64 bit SRAM using genus tool.

This is a crucial phase in the integrated circuit design

process because it ensures that the laid-out geometry

matches the predicted circuit. By proving circuit operation Using the innovus tool, the placement of cells and routing of

through extraction and simulation, very tiny circuits can wires for the design are done. Also, the power and clock

skip this stage. Large digital circuits are typically created arrangements of the design will be performed on innovus

using tools that generate high-level descriptions and tools themselves. The 64-bit SRAM has been developed

compilers that ensure proper layout geometry. Large analog from innovus tool s shown in fig 4 & fig 5. Fig 5 shows the

or mixed-signal circuits that cannot be simulated in a final arrangements and placements of the clock, wires,

reasonable amount of time are the most in need of LVS. power grid, input and output location on the floor planning

LVS can be done considerably faster than simulation, even of the allotted area.

for small circuits, and offers feedback that makes it quicker

E-ISSN: 1998-4464 588

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

Fig. 4. Placement of 64 bit SRAM cells using Innovus tool.

Fig. 6. 64 bit CAM netlist on genus tool of cadence environment.

Fig. 5. Placement and routing did generate final gds2 for SRAM on the

Innovus tool. Fig. 7. 64 bit CAM placement of cells using innovus tool.

The fig 5 shows the final placement and routing defined for Also, generated a gds2 file for both SRAM and CAM. The

the SRAM on cadence environment. The section is ended calculation of power, area, and slack for the design is done

with the final implementation of SRAM on cadence on both genus and innovus tools of cadence environment for

environment, the final power, area and slack are discussed pre and post-validation. In the upcoming section, a

in the Result section. discussion about the implementation of open source tools

for both SRAM and CAM is shown.

B. 64-bit CAM on cadence environment

This section discusses the implementation of 64-bit CAM

on cadence environment with the tools shown in the fig1.The

64-bit CAM netlist has been shown in fig 6. The netlist

shows the connection of wires, gates, flip flops, lookup

tables from input to output of CAM design. The

arrangements of clock given to different parts of the design

and power grids to connect to different parts to distribute the

power equally without any loss of power over the design

without changing the functionality have been connected as

shown in fig 7 for CAM. Similarly, from fig 8 the placement

and routing of the CAM cells have been shown. In this

section, the conclusion of the implementation of SRAM and

CAM on cadence environment using genus and innovus tool.

From the latter and former section implementation of the

backend process for the design such as generating a netlist

file, sdc file, and placing the cells in the proper place. Fig. 8. Placement and Routing(PNR) done for 64 bit CAM on Innovus

tool.

E-ISSN: 1998-4464 589

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

C. 64-bit SRAM on the open-source environment

Open-source tools are mainly a solution to the new VLSI

generation as they can be downloaded free of cost and there

is always a community working on the development of the

tools. The open-source environment has been a newly

emerging tool in the VLSI field to generate gds2 for the

design to overcome the commercial problem of money to

students and design understanding enthusiasts. In this section

the discussion of implementation of 64-bit SRAM on open-

source environment using tools such as Yosys, OpenSta,

Qflow and Magic.

Fig 9 shows the cell placement of 64-bit SRAM on the

GRAYWOLF tool available as an open-source for

generating the area layout of the design SRAM. The cell

placement is done following the rules of the design so that, it

doesn’t encounter any DRC and LVS. Thus, the tool is

efficient in understanding of basic tool flow of the design.

Fig. 10. Placement and Routing did for SRAM using the magic tool.

Fig. 11. Generating gds2 using qflow tool for 64 bit SRAM.

D. 64-bit CAM on the open-source environment

Fig. 9. Cell placement of 64 bit SRAM on Graywolf tool.

The yosys tool is used to generate synth.v file which will

later be used to calculate power and area report for SRAM

design. The SRAM.ys file should contain a design file,

technology file path so that it can generate synth.v file. This

file is later used for calculating the power and area of the

design.

Fig 10 shows the placement and routing for SRAM on

the MAGIC tool. The placement of different cells and

routing the wires to proper cells and gates have been shown

in fig 10. This tool has explored the new connectivity for the

open-source environment and gives easy privilege to users.

Fig 11 shows the QFLOW tool used to generate gds2 for

SRAM, the process begins from selecting the design file and

technology osu035 to conduct. The process begins from

preparation, synthesis, placement, static timing analysis,

routing, post-STA, migration, DRC, LVS, and then final

generating gds2 file. Fig. 12. Placement of cells done on Graywolf tool for 64 bit CAM.

E-ISSN: 1998-4464 590

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

The implementation of CAM in an open-source integrated circuit makers. This creates an undesirable void in

environment is discussed in this section. fig 12 shows the which small enterprises and startups cannot afford to perform

arrangement of CAM cells in the layout. The arrangement is any type of integrated circuit design. Digital synthesis

done using the GRAYWOLF tool for 64-bit CAM. The PnR algorithms are completely locked up in closed-source

of CAM is shown in figure 13 using the MAGIC tool of software, and development is monopolized by a few EDA

open-source environment. software companies.

V. RESULTS AND DISCUSSION

As in the previous discussion of implementing SRAM

and CAM on both cadence and open-source tool, got the

values of power, area, and delay. Table I and Table II depicts

the values obtained from both the environment for 64-bit

SRAM and CAM. The pre-layout values of power, area, and

slack for SRAM and CAM are calculated using the GENUS

tool of cadence environment. The post-layout is calculated

after generating gds2 using the INNOVUS tool from

cadence.

For calculating the power, area, and slack from an open-

Fig. 13. Placement and Routing(PnR) done for 64 bit CAM using a magic source environment, using OPENSTA tool for calculated the

tool.

power and slack of the designs. YOSYS tool is used to

calculate the area of the chip in µm2.

TABLE I. SRAM VALUES COMPARISON OF POWER, AREA,

AND SLACK

Sl. SRAM Cadence Open-

No. environment source

Pre-layout Post- environment

layout

1. Power(mW) 0.145 0.431 1.78

2. Area(µm2) 1104.3648 1868 55808

3. slack 6636 5.672 17.84

Fig. 14. Generation of gds2 for 64 bit CAM using qflow tool.

. Table I shows the power values in mW for 64-bit

The QFLOW tool is used to process the technology SRAM. The power value is comparatively less in the

osu035 for the design and then synthesis of the CAM is also cadence tool with a ~10% saving to that of the open-source

done using the same design file. fig 14 shows the process tool. Similarly, the area can also be saved by ~50% when

that happens in the qflow tool to generate the gds2 file for cadence tools are used for demonstrating. As both power and

CAM. Once, the placement is done i.e the allotment of the area have the upper hand in using cadence tools, therefore it

pins on the different sides of the chip to reduce the is always preferable to use cadence tools to develop gds2 for

connectivity and unnecessary bias. The DRC(design rule 64-bit SRAM for their performance analysis. The osu035

check) and layout versus schematic are checked if the technology is used to generate the report for 64-bit SRAM on

design is anyway violating. Then as the last step gds2 file is the open-source tools. From the report we can conclude that

generated. the wires/nets used to connect the internal blocks of SRAM

is 1259 and wire bits is 1559. The number of public wires is

Qrouter accepts and outputs files in the open standard 6 and the total number of public wire nets is 299. The

LEF and DEF formats. It examines the geometry for each obtained internal power is 85.0497% of the total obtained

cell to detect contact points and route impediments, using power. It is better to reduce the internal power to reduce the

cell definitions from a LEF file. It then reads a DEF file for total power. Also, the sequential power in the block takes the

cell location, pin placement, and netlist, runs the detailed highest power i.e., 95.98% so reducing the power used by the

route, and outputs an annotated DEF file. Qflow is a sequential circuits will definitely be able to reduce the

complete toolchain for synthesizing digital circuits, from overall power used by SRAM after post-layout on cadence

Verilog source through physical layout for a specific environment. The power obtained for SRAM is 1.78mW

fabrication method. Digital synthesis with a goal application which comprises of internal power of 1.5mW and switching

of a chip design is frequently incorporated into large EDA power of 0.286mW. The most of the power is used from the

software packages like Cadence or Synopsys in the internal circuits. So, overall power of the block can be

commercial electronics market. Commercial toolchains are reduced if the internal power is taken care because it takes

becoming increasingly expensive as commercial electronics the power of almost 84% of the total power. Similarly, the

designers strive for cutting-edge performance, and have power taken from the sequential block is 75% as obtained on

largely priced themselves out of all but the most established open-source tools has the internal power is more. So, it better

E-ISSN: 1998-4464 591

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

to take care of the internal power that is generated from the VII. ACKNOWLEDGEMENT

sequential block.

Table II shows the different values obtained for the The authors thank the Principal and HOD of the Dept. of

parameters such as power, area, and slack for 64-bit CAM. ECE for the kind support extended to us on the project

The power values are almost the same for CAM on both the completion.

environment with just 2% variation for the post-layout value

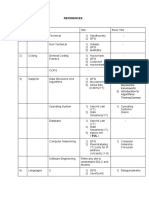

of cadence environment to that of one obtained from the REFERENCES

OpenSta tool. The area of CAM is increased ~18% in open-

[1] N. Surana and J. Mekie, "Energy Efficient Single-Ended 6-T SRAM

source tools to that compared to the value obtained using the for Multimedia Applications," in IEEE Transactions on Circuits and

innovus tool. Also, the timing values that are obtained have Systems II: Express Briefs, vol. 66, no. 6, pp. 1023-1027, June 2019,

met the slack in both the environment. The timing reports for doi: 10.1109/TCSII.2018.2869945.

CAM in an open-source environment are measured by the [2] D. Shah, E. Hung, C. Wolf, S. Bazanski, D. Gisselquist and M.

OpenSta tool. The slack is positive as shown i.e., 2. The Milanovic, "Yosys+nextpnr: An Open Source Framework from

input delay is 2000ns and the data path delay is 7852ns. Verilog to Bitstream for Commercial FPGAs," 2019 IEEE 27th

Annual International Symposium on Field-Programmable Custom

Fortunately, the setup time for the system is 136ns. The Computing Machines (FCCM), 2019, pp. 1-4, doi:

elements are considered to be on the critical path when the 10.1109/FCCM.2019.00010.

delay between them exceeds the clock cycle time. When the [3] Z. Jiang, S. Yin, M. Seok and J. Seo, "XNOR-SRAM: In-Memory

path delay exceeds the clock cycle delay, the circuit will not Computing SRAM Macro for Binary/Ternary Deep Neural

work, therefore the logic design engineer's responsibility is to Networks," 2018 IEEE Symposium on VLSI Technology, 2018, pp.

redesign the circuit to eliminate the timing failure (and 173-174, doi: 10.1109/VLSIT.2018.8510687.

therefore the critical path). The maximum delay in all of the [4] T. -W. Huang, G. Guo, C. -X. Lin and M. D. F. Wong, "OpenTimer

v2: A New Parallel Incremental Timing Analysis Engine," in IEEE

many register-to-register paths is likewise defined by the Transactions on Computer-Aided Design of Integrated Circuits and

critical path, and it does not have to be bigger than the clock Systems, vol. 40, no. 4, pp. 776-789, April 2021, doi:

cycle time. So carefully the paths must be chosen to calculate 10.1109/TCAD.2020.3007319.

the timing of the overall circuit. [5] E. V. Kuliev, V. V. Kureichik and I. O. Kursitys, "Decision making in

VLSI components placement problem based on grey wolf

optimization," 2019 IEEE East-West Design & Test Symposium

TABLE II. CAM VALUES COMPARISON OF POWER, AREA, (EWDTS), 2019, pp. 1-4, doi: 10.1109/EWDTS.2019.8884371.

AND SLACK

[6] D. Bhattacharya, A. N. Bhoj and N. K. Jha, "Design of Efficient

Content Addressable Memories in High-Performance FinFET

Technology," in IEEE Transactions on Very Large Scale Integration

Sl. CAM Cadence Open- (VLSI) Systems, vol. 23, no. 5, pp. 963-967, May 2015, doi:

10.1109/TVLSI.2014.2319192.

No. environment source

[7] S. Jeloka, N. B. Akesh, D. Sylvester and D. Blaauw, "A 28 nm

Pre- Post- environment Configurable Memory (TCAM/BCAM/SRAM) Using Push-Rule 6T

layout layout Bit Cell Enabling Logic-in-Memory," in IEEE Journal of Solid-State

1. Power(mW) 0.202 0.8287 0.832 Circuits, vol. 51, no. 4, pp. 1009-1021, April 2016, doi:

10.1109/JSSC.2016.2515510.

2. Area(µm2) 13861.1 13814.15 152316

[8] L. Sterpone and A. Ullah, "On the optimal reconfiguration times for

3. slack 2 2.65 4.74 TMR circuits on SRAM based FPGAs," 2013 NASA/ESA

Conference on Adaptive Hardware and Systems (AHS-2013), 2013,

pp. 9-14, doi: 10.1109/AHS.2013.6604220.

[9] B. N. K. Reddy, K. Sarangam, T. Veeraiah and R. Cheruku, "SRAM

VI. CONCLUSION AND FUTURE SCOPE cell with better read and write stability with Minimum area,"

TENCON 2019 - 2019 IEEE Region 10 Conference (TENCON),

2019, pp. 2164-2167, doi: 10.1109/TENCON.2019.8929593.

After implementing the design on both the environment [10] S. N. Shahsavani, T. Lin, A. Shafaei, C. J. Fourie and M. Pedram,

of VLSI tools concluding the following. The power, area, "An Integrated Row-Based Cell Placement and Interconnect

and slack calculated have better values i.e., 0.145mW, Synthesis Tool for Large SFQ Logic Circuits," in IEEE Transactions

on Applied Superconductivity, vol. 27, no. 4, pp. 1-8, June 2017, Art

1104.3µm2, and positive slack of 6636 for SRAM in cadence no. 1302008, doi: 10.1109/TASC.2017.2675889.

environment. Also, the power values for 64-bit CAM in [11] J. Lu and B. Taskin, "From RTL to GDSII: An ASIC design course

cadence environment are almost the same as that of open- development using Synopsys® University Program," 2011 IEEE

source environment i.e., 0.8mW. The calculated slack for International Conference on Microelectronic Systems Education,

CAM has a better value on the open-source environment of 2011, pp. 72-75, doi: 10.1109/MSE.2011.5937096.

4.74 value. Cadence environment has the upper hand when it [12] T. Venkata Mahendra, S. Wasmir Hussain, S. Mishra and A.

comes to implementing the design and generating gds2 file Dandapat, "Energy-Efficient Precharge-Free Ternary Content

Addressable Memory (TCAM) for High Search Rate Applications,"

as the environment is too old and well-experienced in in IEEE Transactions on Circuits and Systems I: Regular Papers, vol.

handling the tough corners of the design irrespective of the 67, no. 7, pp. 2345-2357, July 2020, doi:

number of bits used. 10.1109/TCSI.2020.2978295.

[13] Y. Jinsong, W. Chunlu and L. Chuanyi, "Performance Comparisons

The open-source tool as of today has given good results of a Content-Addressable Storage Network System and Other Typical

for the same design. In near future, there is a chance of IP-SAN Based Storage Systems," 2011 Fourth International

having better results because of the continuous improvement Conference on Intelligent Computation Technology and Automation,

happening on the open-source tools in the VLSI market. 2011, pp. 1142-1145, doi: 10.1109/ICICTA.2011.571.

Thus, appreciating the open source tools such as yosys, [14] V. M. Telajala, W. H. Sheikh, S. Mishra and A. Dandapat, "A Low-

OpenSta, qflow, Graywolf, and magic tools currently Power Split-Controlled Single Ended Storage Content Addressable

Memory," 2019 IEEE International Symposium on Smart Electronic

competing with the commercial tools available in the Systems (iSES) (Formerly iNiS), 2019, pp. 369-372, doi:

industry. 10.1109/iSES47678.2019.00091.

E-ISSN: 1998-4464 592

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

[15] M. Irfan and A. Ahmad, "Impact of Initialization on Gate-Based Area scholar category. She is a life member of ISTE, IETE,

Efficient Ternary Content-Addressable Memory," 2018 International

Conference on Computing, Electronics & Communications

fellow member of ISVE, Senior member of IEEE and

Engineering (iCCECE), 2018, pp. 328-332, doi: IEEE-CAS Bangalore section execom member

10.1109/iCCECOME.2018.8658961.

[16] K. Hinsen, "The Magic of Content-Addressable Storage," in Mr. Yatish D Vahvale is a post graduate student of VLSI

Computing in Science & Engineering, vol. 22, no. 3, pp. 113-119, 1 Design and Embedded systems. He is currently pursuing his

May-June 2020, doi: 10.1109/MCSE.2019.2949441.

final year in Master of Technology degree at RV College of

[17] D. Cho, K. Kim and C. Yoo, "A Non-Volatile Ternary Content-

Addressable Memory Cell for Low-Power and Variation-Toleration Engineering, Bengaluru, India. His areas of interest are

Operation," in IEEE Transactions on Magnetics, vol. 54, no. 2, pp. 1- VLSI, Analog and Digital design and IC manufacturing.

3, Feb. 2018, Art no. 9300103, doi: 10.1109/TMAG.2017.2763579.

[18] J. -W. Lee et al., "A 1.8 Gb/s/pin 16Tb NAND Flash Memory Multi- Prof. Praveena N is a part-time research scholar in the

Chip Package with F-Chip of Toggle 4.0 Specification for High Department of Electronics and Communication Engineering

Performance and High Capacity Storage Systems," 2020 IEEE

Symposium on VLSI Circuits, 2020, pp. 1-2, doi: at RV College of Engineering, Bengaluru and also she is

10.1109/VLSICircuits18222.2020.9163052. currently working as an Assistant Professor in the

[19] M. Saitoh et al., "Emerging Non-Volatile Memory and Thin-Film Department of Electronics and Communication Engineering

Transistor Technologies for Future 3D-LSI," 2018 48th European at Sir MVIT, Bangalore. She has 11 years of teaching

Solid-State Device Research Conference (ESSDERC), 2018, pp. 138-

141, doi: 10.1109/ESSDERC.2018.8486916.

experience. Her areas of interest are VLSI, Embedded

[20] M. Janai and I. Bloom, "Charge Gain, NBTI, and Random Telegraph

systems, HDL and Nano electronics etc. She has completed

Noise in EEPROM Flash Memory Devices," in IEEE Electron Device BE and M.Tech from VTU in the year 2004 and 2008

Letters, vol. 31, no. 9, pp. 1038-1040, Sept. 2010, doi: respectively.

10.1109/LED.2010.2058088.

[21] Cherry Bhargava; Gaurav Mani Khanal, "Basic VLSI Design Dr. Mamatha A.S is currently working as Associate

Technology: Technical Questions and Solutions," in Basic VLSI

Design Technology: Technical Questions and Solutions , River Professor in the Department of Electronics and

Publishers, 2020, pp.i-xx. Communication Engineering at St.Joseph Engineering

[22] Cherry Bhargava; Gaurav Mani Khanal, "2 IC Fabrication College, Mangalore. She has 22 years of teaching

Technology," in Basic VLSI Design Technology: Technical experience. She is the author of four international journals

Questions and Solutions , River Publishers, 2020, pp.91-112.

and six international conferences in the field of

[23] Cherry Bhargava; Gaurav Mani Khanal, "4 Verilog Hardware

Descriptive Language," in Basic VLSI Design Technology: Technical

Multispectral Image Compression. She is the author of the

Questions and Solutions , River Publishers, 2020, pp.153-200. Network Theory textbook, Engineering Statistics & Linear

[24] H. Chu et al., "An ASIC Design of Multi-Electrode Digital Basket Algebra textbook and Control Engineering text book. Her

Catheter Systems with Reconfigurable Compressed Sampling," 2018 areas of interest are Signal Processing, Image Compression,

31st IEEE International System-on-Chip Conference (SOCC), 2018, and Control Engineering etc. She is a Senior IEEE member

pp. 124-129, doi: 10.1109/SOCC.2018.8618535.

[25] C. Zhao, Y. Yan and W. Li, "An efficient ASIC Implementation of

QARMA Lightweight Algorithm," 2019 IEEE 13th International

Conference on ASIC (ASICON), 2019, pp. 1-4, doi:

10.1109/ASICON47005.2019.8983618.

Dr. Shylashree N is currently working as Associate

Professor in the Department of Electronics and

Communication Engineering at RV College of Engineering,

Bengaluru. She is having 15 years of teaching experience.

She was a recipient of the best PhD thesis award for the year

2016-2017 in Electronics and Communication Engineering

from BITES. She has received the best IEEE researcher

award in IEEE-AGM meeting held during 2021 from

Bangalore IEEE section. She has also received the best

paper award in IEEE-ICERECT held during 2015 at

Mandya. She has research publication in 18 International

Journals (out of which 5 journals are Springer-SCI journals),

4 Springer book chapters and 9 International conferences.

She has published 2 patents and filed 1 German patent in the

area of cryptography. She has also published 2 patents in the

area of VLSI out of which one of them got a grant. She is

also the author of the Network Theory textbook,

Engineering Statistics & Linear Algebra text book and

Control Engineering textbook. She has funded project on

chalcogenide materials & consultancy projects on FPGA

and has delivered many technical talks on VLSI. She has

delivered lectures as a subject matter expert in VTU e-

shikshana and EDUSAT program. She is a recipient of

international travel grant under SERB young research

E-ISSN: 1998-4464 593

INTERNATIONAL JOURNAL OF CIRCUITS, SYSTEMS AND SIGNAL PROCESSING

DOI: 10.46300/9106.2021.15.65 Volume 15, 2021

Creative Commons Attribution License 4.0

(Attribution 4.0 International, CC BY 4.0)

This article is published under the terms of the Creative

Commons Attribution License 4.0

https://creativecommons.org/licenses/by/4.0/deed.en_US

E-ISSN: 1998-4464 594

View publication stats

You might also like

- bsbxcs402 Task 1Document5 pagesbsbxcs402 Task 1Maliha Qureshi100% (1)

- Multicore Processors and Systems PDFDocument310 pagesMulticore Processors and Systems PDFwkfzar100% (1)

- Maths Competition PDFDocument49 pagesMaths Competition PDFABCNo ratings yet

- NC Studio User Manual enDocument117 pagesNC Studio User Manual enAdeng Esteibar60% (5)

- Design and Implementation of 64-Bit SRAM and CAM On Cadence and Open-Source EnvironmentDocument9 pagesDesign and Implementation of 64-Bit SRAM and CAM On Cadence and Open-Source EnvironmentChandra Shekar MedarNo ratings yet

- X-SRAM Enabling In-Memory Boolean Computations in CMOS Static Random Access MemoriesDocument14 pagesX-SRAM Enabling In-Memory Boolean Computations in CMOS Static Random Access Memoriesshri1098No ratings yet

- 6t Sram ThesisDocument8 pages6t Sram Thesisfjdqvrcy100% (2)

- AreviewonSRAM Basedcomputingin Memory Circuitsfunctionsandapplications3Document27 pagesAreviewonSRAM Basedcomputingin Memory Circuitsfunctionsandapplications3예민욱No ratings yet

- Dagatan Nino PRDocument12 pagesDagatan Nino PRdagatan.ninoNo ratings yet

- IEEE-Spin Transfer Torque MemoriesDocument40 pagesIEEE-Spin Transfer Torque MemoriesScott Backster ClarckNo ratings yet

- Electronics 12 00834Document15 pagesElectronics 12 00834Dat Nguyen ThanhNo ratings yet

- 11BrijeshSampath ICDCOM2011Document6 pages11BrijeshSampath ICDCOM2011Hưng Nguyễn ThànhNo ratings yet

- Lab Report 5Document3 pagesLab Report 5SagorNo ratings yet

- A Low Power 10T SRAM Cell With Extended Static Noise Margins Is Used To Implement An 8 by 8 SRAMDocument10 pagesA Low Power 10T SRAM Cell With Extended Static Noise Margins Is Used To Implement An 8 by 8 SRAMIJRASETPublicationsNo ratings yet

- Smart Memories A Seminar Report: A.Rana Pratap (14761A0506)Document15 pagesSmart Memories A Seminar Report: A.Rana Pratap (14761A0506)Hari KrishNo ratings yet

- Verification of Open-Source Memory Compiler Framework With A Practical PDKDocument7 pagesVerification of Open-Source Memory Compiler Framework With A Practical PDKJack GengNo ratings yet

- 7f99 PDFDocument8 pages7f99 PDFSubhadeep Deb RoyNo ratings yet

- An Efficient Test Design For Verification of Cache Coherence in CmpsDocument7 pagesAn Efficient Test Design For Verification of Cache Coherence in CmpsSHIBU M RNo ratings yet

- A Fully Pipelined and Dynamically Composable Architecture of CGRADocument9 pagesA Fully Pipelined and Dynamically Composable Architecture of CGRABanusha chandranNo ratings yet

- Design of Multiplexer Based 64-Bit SRAM Using QCA: Australian Journal of Basic and Applied Sciences January 2016Document8 pagesDesign of Multiplexer Based 64-Bit SRAM Using QCA: Australian Journal of Basic and Applied Sciences January 2016Raghavendra SinghNo ratings yet

- Microelectronics Reliability: A. Islam, Mohd. HasanDocument6 pagesMicroelectronics Reliability: A. Islam, Mohd. Hasantemp759No ratings yet

- VLSI ProjectsDocument4 pagesVLSI ProjectsMallisetty YaswanthNo ratings yet

- Design 3 S4P8NDocument12 pagesDesign 3 S4P8NL S Krishna MaanasNo ratings yet

- Ieee Research Paper On VlsiDocument6 pagesIeee Research Paper On Vlsiebvjkbaod100% (1)

- Low Power Approaches in SRAM: Vikas Nehra and Rajeev KamalDocument5 pagesLow Power Approaches in SRAM: Vikas Nehra and Rajeev KamalRakeshconclaveNo ratings yet

- TC 2019 06 0318finalDocument14 pagesTC 2019 06 0318finaldewufhweuihNo ratings yet

- Asap7: A 7-Nm Finfet Predictive Process Design Kit: Microelectronics Journal July 2016Document12 pagesAsap7: A 7-Nm Finfet Predictive Process Design Kit: Microelectronics Journal July 2016Léo RibeiroNo ratings yet

- Cray XC Scalability Advantage White PaperDocument16 pagesCray XC Scalability Advantage White PaperadwausNo ratings yet

- A Novel Column-Decoupled 8T Cell For Low-PowerDocument14 pagesA Novel Column-Decoupled 8T Cell For Low-PowerSaikiran RaghuNo ratings yet

- Neuromorphic Computing-From Devices To IntegratedcircuitsDocument21 pagesNeuromorphic Computing-From Devices To Integratedcircuits322203359001No ratings yet

- PRIYANKA KUMARI (Low Power SRAM)Document15 pagesPRIYANKA KUMARI (Low Power SRAM)Rekha KumariNo ratings yet

- Vlsi Implementation of 32KB Sleepy Sram ThesisDocument50 pagesVlsi Implementation of 32KB Sleepy Sram ThesisNikhil Manohar GhoradkarNo ratings yet

- Dayananda Sagar College of Engineering, Bangalore, Karnataka Department of Electronics & Communication EngineeringDocument17 pagesDayananda Sagar College of Engineering, Bangalore, Karnataka Department of Electronics & Communication Engineeringsri harshaphaniNo ratings yet

- Low Power Sram ThesisDocument5 pagesLow Power Sram ThesisBestWriteMyPaperWebsiteSingapore100% (2)

- Cell Multproc Comm NTWK - Built For SPDDocument14 pagesCell Multproc Comm NTWK - Built For SPDlycankNo ratings yet

- Rapid Memory-Aware Selection of Hardware Accelerators in Programmable Soc DesignDocument12 pagesRapid Memory-Aware Selection of Hardware Accelerators in Programmable Soc DesignBanusha chandranNo ratings yet

- Architecture and Physical Implementation of A Third Generation 65 NM, 16 Core, 32 Thread Chip-Multithreading SPARC ProcessorDocument11 pagesArchitecture and Physical Implementation of A Third Generation 65 NM, 16 Core, 32 Thread Chip-Multithreading SPARC ProcessorRoshdy AbdelRassoulNo ratings yet

- A Review of 018-spl Mum Full Adder Performances FoDocument12 pagesA Review of 018-spl Mum Full Adder Performances FoShaik Abdul Salam BatchaNo ratings yet

- ERA AppnoteDocument19 pagesERA AppnoteAbhishek ChauhanNo ratings yet

- Electrical Engineering and Computer Science Department: Chip Multiprocessor Cooperative Cache Compression and MigrationDocument23 pagesElectrical Engineering and Computer Science Department: Chip Multiprocessor Cooperative Cache Compression and Migrationeecs.northwestern.eduNo ratings yet

- 10T SRAM Using Half-V Precharge and Row-Wise Dynamically Powered Read Port For Low Switching Power and Ultralow RBL LeakageDocument11 pages10T SRAM Using Half-V Precharge and Row-Wise Dynamically Powered Read Port For Low Switching Power and Ultralow RBL LeakageDr. Pullareddy AvulaNo ratings yet

- Kumar 2023 Eng. Res. Express 5 035057Document10 pagesKumar 2023 Eng. Res. Express 5 035057eceaitsrajampetNo ratings yet

- Design of Fault Tolerant Algorithm For Network On Chip Router Using Field Programmable Gate ArrayDocument8 pagesDesign of Fault Tolerant Algorithm For Network On Chip Router Using Field Programmable Gate ArrayIJRES teamNo ratings yet

- The Tera Computer SystemDocument6 pagesThe Tera Computer SystemJohn WestonNo ratings yet

- Radiation Tolerant SRAM Cell Design in 65nm TechnologyDocument8 pagesRadiation Tolerant SRAM Cell Design in 65nm Technologyameed shahNo ratings yet

- Parallel Efficient Sparse Matrix-Matrix Multiplication On Multicore PlatformsDocument11 pagesParallel Efficient Sparse Matrix-Matrix Multiplication On Multicore PlatformsSatya Gautam VadlamudiNo ratings yet

- Batch 3 1Document23 pagesBatch 3 1TAMMANENI NAVYANo ratings yet

- Distributed Memory Compiler Design For Sparse Problems: IEEE Transactions On Computers July 1995Document49 pagesDistributed Memory Compiler Design For Sparse Problems: IEEE Transactions On Computers July 1995Aritra DattaguptaNo ratings yet

- Designing Energy-Efficient Intermittently Powered Systems Using Spin-Hall-Effect-Based Nonvolatile SRAMDocument14 pagesDesigning Energy-Efficient Intermittently Powered Systems Using Spin-Hall-Effect-Based Nonvolatile SRAMSinchana GuptaNo ratings yet

- Venkata Lakshmi 2021 J. Phys. Conf. Ser. 1804 012185Document8 pagesVenkata Lakshmi 2021 J. Phys. Conf. Ser. 1804 012185seshu bradyNo ratings yet

- Wearout Resilience in Nocs Through An Aging Aware Adaptive Routing AlgorithmDocument5 pagesWearout Resilience in Nocs Through An Aging Aware Adaptive Routing AlgorithmNguyen Van ToanNo ratings yet

- Design and VLSI Implementation of 8 MB Low Power SRAM in 90nmDocument10 pagesDesign and VLSI Implementation of 8 MB Low Power SRAM in 90nmcnnprem_eeeNo ratings yet

- Counter Braids: A Novel Counter Architecture For Per-Flow MeasurementDocument12 pagesCounter Braids: A Novel Counter Architecture For Per-Flow MeasurementAmit ChandakNo ratings yet

- A Fast Reliable and Wide-Voltage-Range In-Memory Computing ArchitectureDocument6 pagesA Fast Reliable and Wide-Voltage-Range In-Memory Computing ArchitecturezywNo ratings yet

- Literature ReviewDocument4 pagesLiterature ReviewShraddha MaheshwariNo ratings yet

- A 4x4 Modified 8T SRAM Cell Array Using Power Gating TechniqueDocument7 pagesA 4x4 Modified 8T SRAM Cell Array Using Power Gating TechniqueArvind ChakrapaniNo ratings yet

- Low-Leakage Asymmetric-Cell SRAM1Document4 pagesLow-Leakage Asymmetric-Cell SRAM1api-19668941No ratings yet

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDocument7 pagesPerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapNo ratings yet

- V3 Issue 1 423 427Document5 pagesV3 Issue 1 423 427dubeyNo ratings yet

- Pal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008Document11 pagesPal 2021 IOP Conf. Ser. Mater. Sci. Eng. 1187 012008seshu bradyNo ratings yet

- Improving The Scalabiliy of Neutron Cross-Section Lookup Codes On Multicore NUMA SystemDocument9 pagesImproving The Scalabiliy of Neutron Cross-Section Lookup Codes On Multicore NUMA SystemPeter LiuNo ratings yet

- 8k Bit Using 6t SramDocument8 pages8k Bit Using 6t SramSwati Navdeep AggarwalNo ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Times-NIE-Web-Ed-MARCH 31Document4 pagesTimes-NIE-Web-Ed-MARCH 31supritaNo ratings yet

- Macos (Up To Ver.11) Cups Driver: How To Install For Brother Dcp-T420WDocument1 pageMacos (Up To Ver.11) Cups Driver: How To Install For Brother Dcp-T420WClarine Kyla BautistaNo ratings yet

- Macks Animation Credits TutorialDocument6 pagesMacks Animation Credits Tutorialapi-646257156No ratings yet

- Participation, Access and InteractionDocument15 pagesParticipation, Access and InteractionMaría Isabel Villa MontoyaNo ratings yet

- Presentation5 3Document16 pagesPresentation5 3Abhirami SNo ratings yet

- Linear Regression in Real Life - Towards Data ScienceDocument16 pagesLinear Regression in Real Life - Towards Data ScienceMatthew MhlongoNo ratings yet

- Social Media Strategy WorkbookDocument28 pagesSocial Media Strategy WorkbookGamelinio 13No ratings yet

- Fabian Firpo (Fabi) - RESUME-1Document1 pageFabian Firpo (Fabi) - RESUME-1lucornet9No ratings yet

- Pmac2a PC104 Axis HRMDocument55 pagesPmac2a PC104 Axis HRMhuseyintopcuNo ratings yet

- Editing Tower Data: Design CodeDocument15 pagesEditing Tower Data: Design CodeErik MahonNo ratings yet

- DATACOM Ethernet Switches DM1200E Enterprise FamilyDocument4 pagesDATACOM Ethernet Switches DM1200E Enterprise FamilySEA Telecom NMC - OperaçõesNo ratings yet

- 194-914-0010-EN2 - Configuration Manager Installation and User ManualDocument12 pages194-914-0010-EN2 - Configuration Manager Installation and User ManualTony KututoNo ratings yet

- Integration of Drive Systems Via PROFINET in PCS7 enDocument37 pagesIntegration of Drive Systems Via PROFINET in PCS7 enPeter UhuleNo ratings yet

- Last ExceptionDocument2 pagesLast ExceptionNataly PerezNo ratings yet

- Chapter 2 - Working Principle of Hillstone Firewall - 5.5R7Document32 pagesChapter 2 - Working Principle of Hillstone Firewall - 5.5R7Heshitha PushpawelaNo ratings yet

- Study ReferencesDocument2 pagesStudy ReferencesParth NavaleNo ratings yet

- Conbox TutorialsDocument292 pagesConbox TutorialsRam Nepali50% (2)

- Sisweb Servlet Cat - Cis.sis - Pcontroller.cssiDocument2 pagesSisweb Servlet Cat - Cis.sis - Pcontroller.cssiJose F Rivera Morales100% (1)

- Uchebnik Chast Vtoraya SBDocument203 pagesUchebnik Chast Vtoraya SBDaniela TigerNo ratings yet

- Automation API TM14 PDFDocument72 pagesAutomation API TM14 PDFMihaiLeonteNo ratings yet

- SOAP API Scenario in RO2Document11 pagesSOAP API Scenario in RO2Ilirian RexhoNo ratings yet

- Pac 6x00 8x00 Technical Manual 9033742 Ifu enDocument24 pagesPac 6x00 8x00 Technical Manual 9033742 Ifu enstefan robertoNo ratings yet

- Essential Computer Maintenance TipsDocument2 pagesEssential Computer Maintenance TipsLEXUS CCTVNo ratings yet

- Snort InstallationDocument637 pagesSnort InstallationNik SukiNo ratings yet

- N3015 007 - Integrators Guide AD2CP - 0322Document117 pagesN3015 007 - Integrators Guide AD2CP - 0322Marcos Antonio da Rocha FerreiraNo ratings yet

- COMMANDER Products Data Sheet: PC Configuration SoftwareDocument4 pagesCOMMANDER Products Data Sheet: PC Configuration SoftwareTawanda MandazaNo ratings yet