Professional Documents

Culture Documents

Divyanshu Resume

Divyanshu Resume

Uploaded by

Divyanshu Angram0 ratings0% found this document useful (0 votes)

3 views2 pagesOriginal Title

Divyanshu_Resume (1)

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

3 views2 pagesDivyanshu Resume

Divyanshu Resume

Uploaded by

Divyanshu AngramCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 2

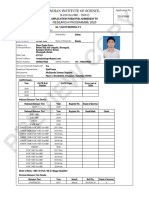

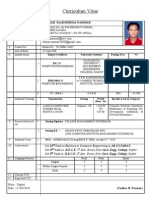

PERSONAL INFORMATION

Full Name (Full Name as in

DIVYANSHU ANGRAM

Pan card application) :

Date of Birth (DD-MM-YY) 14-07-2001

Permanent Address VILLAGE BAHLOLPUR POST BAHLOLPUR DISTRICT BULANDSHAHR

Temporary Address MNIT JAIPUR, JLN MARG MALVIYA NAGAR JAIPUR

Mobile contact number 8630374503

Home Contact number 8534048901

Email Address 2023PEV5327

EDUCATION

Post Graduate Degree Mtech College Name MNIT JAIPUR

(Mtech/M.E./M.Sc/MCA/MBA)

Branch VLSI DESIGN

CGPA (avg till last 9.00 (I SEM)

sem)

Current year & Sem (eg PG Start Date

1ST YEAR,2ND SEM 08/23

3rd year, 5th Sem) (MM/YY)

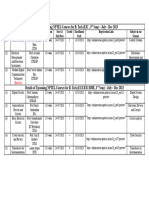

A GM/ID METHODOLOGY FOR DESIGNING COMMON SOURCE

AMPLIFIER BY USING 180 NM TECHNOLOGY

(Simulated this amplifier using Cadence Virtuoso and analyzed

different graphs like Id/w, gain, bandwidth, Gm/id vs Vgs.)

Project Details (if any) IMPLEMENTED 8-BIT CARRY LOOK-AHEAD ADDER USING VERILOG

(Fastest addition performed without taking the previous stage carry

input.)

Graduate Degree RAJKIYA ENGINEERING COLLEGE

Btech College Name

(Btech/B.E./B.Sc/BCA) (BANDA)

ELECTRICAL CGPA (avg till last

Branch 8.35

ENGINEERING sem)

Current year & Sem (eg Grad Start

08/2018

3rd year, 5th Sem) Date(MM/YY)

SMART LOCKING SYSTEM (PATENTED PROJECT)

PATENTED BY REPUBLIC OF SOUTH AFRICA

(A smart IoT-based security system, providing multi-layered security

for authorized users and remotely monitor the system to give access to

Project Details (if any) other unauthorized users after proper authentication.)

REAL TIME SIMULATION

(Collection of power requirements of a hostel during a season and

estimating the cost per unit of electricity by using the best resources of

electricity available.)

UP Year of

10th (Percentage) Board Name

88.16 BOARD Passing 2016

UP Year of

12th (Percentage) Board Name

89 BOARD Passing 2018

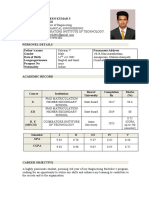

Technical Certifications/Trainings/Skills

• Tools: Cadence virtuoso, Xilinx Vivado

• Hardware Description Language: Verilog

• Computer Programming Language: Basics of C

• Courses studied: Digital Electronics, Digital CMOS ICs.,

• Basics of STA

SCHOLARSHIPS/AWARDS/PUBLICATIONS/ACHIEVEMENTS

• Awarded with District Aligarh Ratna prize and “Medhavi Chhatra Puruskar” by UP Chief •

Minister for being topper of the Mathematics group in Class XII (2018).

• Top 5th student of my department in B.Tech.

• Research paper published on Smart Locking System based on Arduino and Raspberry Pi and

project patented.

Any Former Internship Experience/Prior Work Experience

• Coordinator of the Cultural Organizing Committee of the college

• Vice Chairperson of the IEEE student chapter (2020-2022)

You might also like

- Personal Summary/ Career Objective:: Curriculum VitaeDocument5 pagesPersonal Summary/ Career Objective:: Curriculum VitaeEr Satabdi ChowdhuryNo ratings yet

- FLM Cisco Apprenticeship Shortlisted Resume SampleDocument2 pagesFLM Cisco Apprenticeship Shortlisted Resume SampleNikitha BaikanNo ratings yet

- Prakash Resume Updated PDFDocument2 pagesPrakash Resume Updated PDFPrakashrajNo ratings yet

- Intern CV FormatDocument2 pagesIntern CV FormatSumit GargNo ratings yet

- GMRC AdvertisementDocument11 pagesGMRC AdvertisementSHAH VIRALNo ratings yet

- CR No LIET PO 2023 37Document1 pageCR No LIET PO 2023 37amansyed675No ratings yet

- Namrata (CV)Document1 pageNamrata (CV)Namrata MohantyNo ratings yet

- Indian Institute of Technology Patna BIHTA PATNA-801106 Research & Development UnitDocument2 pagesIndian Institute of Technology Patna BIHTA PATNA-801106 Research & Development UnitA23ABHIGYA HAZRANo ratings yet

- Scrutiny Result of Application Form For Admission in M.tech - and M.SC - Programmes Through Institute Level Spot Round For AY 2023 24Document15 pagesScrutiny Result of Application Form For Admission in M.tech - and M.SC - Programmes Through Institute Level Spot Round For AY 2023 24KärthïçkNo ratings yet

- Naval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Document3 pagesNaval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Adarsh BhartiNo ratings yet

- Naval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Document3 pagesNaval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Priya Ranjan SharmaNo ratings yet

- Naval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Document3 pagesNaval Science & Technological Laboratory DRDO, Ministry of Defence, Visakhapatnam - 530027Ajay DasNo ratings yet

- Student Data For TCS ION - Placement Assistance 27.09.2022Document8 pagesStudent Data For TCS ION - Placement Assistance 27.09.2022A. AKASH 4001-UCE-TKNo ratings yet

- Ann 04Document1 pageAnn 04ankeet3No ratings yet

- Faculty Biodata - NGP - SMT Neha PardesiDocument3 pagesFaculty Biodata - NGP - SMT Neha PardesiLokesh DhakeNo ratings yet

- Pakistan Telecommunication Authority: Employment Application FormDocument3 pagesPakistan Telecommunication Authority: Employment Application FormAkcent AdrianNo ratings yet

- Applied Cryptography: Faculty Development Programme (FDP) ONDocument2 pagesApplied Cryptography: Faculty Development Programme (FDP) ONKanakala pradeep KumarNo ratings yet

- ME MTech MArch Application FormDocument1 pageME MTech MArch Application FormZero SevenNo ratings yet

- Wa0001Document2 pagesWa0001Shivam BhallaNo ratings yet

- Technician Hiring - 2022Document1 pageTechnician Hiring - 2022PPDC NAGAURNo ratings yet

- GEPCO-3002906 Hyderabad Junior Engineer (Electrical) Open MeritDocument4 pagesGEPCO-3002906 Hyderabad Junior Engineer (Electrical) Open MeritIzhar Ahmed NoohpotoNo ratings yet

- Electrical Working 6 Month To 3 Years Delhi and Near 15aug2017!1!852Document216 pagesElectrical Working 6 Month To 3 Years Delhi and Near 15aug2017!1!852prerna nandNo ratings yet

- Indian Institute of Science,: Research Programme 2020Document3 pagesIndian Institute of Science,: Research Programme 2020data scienceNo ratings yet

- M AppalnaiduDocument3 pagesM Appalnaidu210ee2229No ratings yet

- Kavya Latha ResumeDocument2 pagesKavya Latha ResumeKavya LathaNo ratings yet

- Share Vishwaja (Resume)Document3 pagesShare Vishwaja (Resume)Vishwaja satish virbhaktNo ratings yet

- Get JobDocument14 pagesGet JobTwisha GuptaNo ratings yet

- Dd/Mm/Yyyy:: Work Experience (If Applicable) - Please Do List All OrganisationsDocument4 pagesDd/Mm/Yyyy:: Work Experience (If Applicable) - Please Do List All OrganisationsGowtham krishnaNo ratings yet

- Indian Institute of Science,: Course Programme (M MGT) 2019Document2 pagesIndian Institute of Science,: Course Programme (M MGT) 2019Pratik JainNo ratings yet

- Hasan Mahmud ZilanyDocument4 pagesHasan Mahmud ZilanyhhelectronicsbdNo ratings yet

- Intern CV FormatDocument2 pagesIntern CV FormatManish BhartiNo ratings yet

- TCS 2020 Recruitment DetailsDocument2 pagesTCS 2020 Recruitment DetailsHiteshNo ratings yet

- Utkarsh Sharma: Work Experience Techincal SkillsDocument1 pageUtkarsh Sharma: Work Experience Techincal SkillschetanNo ratings yet

- A Report On Industrial Training Taken at NTPC Dadri: (From 20/05/2019 To 18/06/2019)Document10 pagesA Report On Industrial Training Taken at NTPC Dadri: (From 20/05/2019 To 18/06/2019)Bantisaini SainiNo ratings yet

- A Report On Industrial Training Taken at NTPC Dadri: (From 20/05/2019 To 18/06/2019)Document10 pagesA Report On Industrial Training Taken at NTPC Dadri: (From 20/05/2019 To 18/06/2019)Bantisaini SainiNo ratings yet

- A Seminar Report On: GSM V/S CdmaDocument6 pagesA Seminar Report On: GSM V/S CdmaGagan SehgalNo ratings yet

- Dr. C. V. Raman University: Diploma in Computer Application (DCA) 4800 3500Document10 pagesDr. C. V. Raman University: Diploma in Computer Application (DCA) 4800 3500Kunwar RawatNo ratings yet

- Application Form For Non-Teaching PostsDocument3 pagesApplication Form For Non-Teaching PostsMrs. Dhwani Hakani ADF-PHDNo ratings yet

- NPTEL Courses - 3rd - 5th Sem - ECE - EICDocument1 pageNPTEL Courses - 3rd - 5th Sem - ECE - EICsawasthi.1801No ratings yet

- Tushar ParmarDocument1 pageTushar ParmartusharparmarNo ratings yet

- J.K.K.Nattraja: Two Day National Level Workshop OnDocument2 pagesJ.K.K.Nattraja: Two Day National Level Workshop OnJ.Gowri ShankarNo ratings yet

- PT. Pupuk Kaltim: Lectrical NgineerDocument1 pagePT. Pupuk Kaltim: Lectrical NgineerリズキーNo ratings yet

- Mahesh Kumar (1902026)Document3 pagesMahesh Kumar (1902026)19FT026 Mahesh kumar.sNo ratings yet

- Mounadeep Poddar: Electrical and Electronic Engineering (B.Tech, 2 Year)Document2 pagesMounadeep Poddar: Electrical and Electronic Engineering (B.Tech, 2 Year)Sayan ChatterjeeNo ratings yet

- CV Ijazah Transkrip Dan Sertif PendukungDocument6 pagesCV Ijazah Transkrip Dan Sertif PendukungリズキーNo ratings yet

- Delhi Technological University: Result NotificationDocument5 pagesDelhi Technological University: Result Notificationlikhith krishnaNo ratings yet

- 2018 Cognizant Application FormDocument3 pages2018 Cognizant Application FormDeepanshu GuptaNo ratings yet

- Siru Sri Lalaka Gunathilaka: Electronics & Power Systems EngineeringDocument2 pagesSiru Sri Lalaka Gunathilaka: Electronics & Power Systems EngineeringRobbetMalcumNo ratings yet

- Peddaboina YamunaDocument1 pagePeddaboina YamunaResearch ArchitectNo ratings yet

- Gujarat Metro Rail Corporation (GMRC) Limited: Recruitment Notification of O&M Personnel (Non-Executives)Document11 pagesGujarat Metro Rail Corporation (GMRC) Limited: Recruitment Notification of O&M Personnel (Non-Executives)Vyas IshaNo ratings yet

- Iit Madras Resume Template 2 PageDocument3 pagesIit Madras Resume Template 2 PageMdMushahid MakandarNo ratings yet

- 14Document1 page14mehul03ecNo ratings yet

- 01 - VGST Format 2016-17 - FinalDocument23 pages01 - VGST Format 2016-17 - Finalaeu3csd bdvtNo ratings yet

- Special PhaseDocument2 pagesSpecial PhaseJhanavi KattelaNo ratings yet

- National Institute of Technology CalicutDocument2 pagesNational Institute of Technology CalicutTopRankersNo ratings yet

- Application Form For New EPE ApplicantsDocument11 pagesApplication Form For New EPE ApplicantsMuhammad ZulfiqarNo ratings yet

- About Gate - Eeenotes2uDocument6 pagesAbout Gate - Eeenotes2uvamsi prasannaNo ratings yet

- Detail Advertsiement 02 - 2019Document4 pagesDetail Advertsiement 02 - 2019dhavalgiriNo ratings yet

- Ayyaj Mulani - PP - 15-Nov-2022Document3 pagesAyyaj Mulani - PP - 15-Nov-2022yash shahakarNo ratings yet

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesFrom EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNo ratings yet

- 2N3055A (NPN), MJ15015 (NPN), MJ15016 (PNP) Complementary Silicon High Power TransistorsDocument6 pages2N3055A (NPN), MJ15015 (NPN), MJ15016 (PNP) Complementary Silicon High Power Transistorsklaus allowsNo ratings yet

- Qualitrol AP 900 910 RPRRDocument6 pagesQualitrol AP 900 910 RPRRJefe de PlantaNo ratings yet

- Three Phase Diode Rectifier With L, C and LC FilterDocument3 pagesThree Phase Diode Rectifier With L, C and LC FilterAnand SainiNo ratings yet

- Destroy Any Device With EMP Jammer - 3 Steps - InstructablesDocument9 pagesDestroy Any Device With EMP Jammer - 3 Steps - InstructablesCarlos Antonio De Bourbon-MontenegroNo ratings yet

- VNL5300S5-E: Omnifet Iii Fully Protected Low-Side DriverDocument21 pagesVNL5300S5-E: Omnifet Iii Fully Protected Low-Side DriverEugênio CésarNo ratings yet

- Gespsinaf: Active Harmonic Filter User ManualDocument86 pagesGespsinaf: Active Harmonic Filter User ManualAhmad Shawky El MadhalyNo ratings yet

- Problems For Chapter 3Document3 pagesProblems For Chapter 3qasimrazam89No ratings yet

- Codigos de FallasDocument233 pagesCodigos de Fallasjosecuellar69No ratings yet

- Sem3 EE EEEDocument12 pagesSem3 EE EEEGpc JaisalmerNo ratings yet

- User's Manual: EJX510A, EJX530A, EJX610A and EJX630A Absolute Pressure and Gauge Pressure TransmittersDocument51 pagesUser's Manual: EJX510A, EJX530A, EJX610A and EJX630A Absolute Pressure and Gauge Pressure TransmittersInstrumentation GCS GanaNo ratings yet

- IEC Contactors and Starters: Three-Pole Contactors, Frame C-UL/CSA RatingsDocument2 pagesIEC Contactors and Starters: Three-Pole Contactors, Frame C-UL/CSA RatingsJdd KasNo ratings yet

- MR 261-2017 Evaluation - 230118Document4 pagesMR 261-2017 Evaluation - 230118Ronish ChandraNo ratings yet

- Microelectromechanical Assignment Help: Problem 2.6: Dynamics With Matlab and SimulinkDocument24 pagesMicroelectromechanical Assignment Help: Problem 2.6: Dynamics With Matlab and SimulinkMechanical Engineering Assignment HelpNo ratings yet

- RFQ13355Document2 pagesRFQ13355Abdulgaffar HawaldarNo ratings yet

- Cordless Impact Wrench: Instruction ManualDocument12 pagesCordless Impact Wrench: Instruction ManualCésar PérezNo ratings yet

- Octopus 900 Instructions For UseDocument18 pagesOctopus 900 Instructions For UseAli FadhilNo ratings yet

- Subject Page No.: Premium SoundDocument2 pagesSubject Page No.: Premium Soundvette512No ratings yet

- 10000mah Mi Power Bank 3 Ultra Compact - Manual - enDocument6 pages10000mah Mi Power Bank 3 Ultra Compact - Manual - enJosé Manuel ReyesNo ratings yet

- OM Manual 3P579594-2-1Document1 pageOM Manual 3P579594-2-1Raj ThakurNo ratings yet

- Week 14. English IIIDocument3 pagesWeek 14. English IIIOil Field Industrial ServicesNo ratings yet

- Design and Implementation of Tracking System For Dual Axis Solar Tracker Using PIC 16F887Document4 pagesDesign and Implementation of Tracking System For Dual Axis Solar Tracker Using PIC 16F887ZclanPJ4UNo ratings yet

- Analysis of Load Output Characteristics of 3600kV Impulse Voltage GeneratorDocument5 pagesAnalysis of Load Output Characteristics of 3600kV Impulse Voltage GeneratorAlessandro SouzaNo ratings yet

- MCQ (Ec3352 DSD) - Unit 3Document2 pagesMCQ (Ec3352 DSD) - Unit 3PRABHAVATHY SNo ratings yet

- MATLAB Code For Amplitude ModulationDocument2 pagesMATLAB Code For Amplitude ModulationKazi Barakat50% (2)

- Fedhii Bittaa Meeshaa EMG Bara 2013Document11 pagesFedhii Bittaa Meeshaa EMG Bara 2013Jamal100% (1)

- H55M-ED55 Seres: MS-7635 (v1.x) ManboardDocument94 pagesH55M-ED55 Seres: MS-7635 (v1.x) Manboardjake zaynNo ratings yet

- Microeel: Features & BenefitsDocument2 pagesMicroeel: Features & BenefitsAntoNo ratings yet

- OPP-26897 (Arthurholm With Bosch)Document6 pagesOPP-26897 (Arthurholm With Bosch)ARIELNo ratings yet

- Omron Relay Catalogue PDFDocument58 pagesOmron Relay Catalogue PDFQuan PhanNo ratings yet

- Radar Level TransmitterDocument2 pagesRadar Level TransmitterpurizanNo ratings yet