Professional Documents

Culture Documents

Clock Buffers/Multiplexers: I O IB

Clock Buffers/Multiplexers: I O IB

Uploaded by

Thiện KhiêmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Clock Buffers/Multiplexers: I O IB

Clock Buffers/Multiplexers: I O IB

Uploaded by

Thiện KhiêmCopyright:

Available Formats

R

Clock Buffers/Multiplexers

I

O

IB

UG331_c4_04_080906

Inputs Outputs

I IB O

0 0 -

0 1 0

1 0 1

1 1 -

Notes:

1. The dash (-) means no change.

Figure 2-4: IBUFGDS Component and Truth Table

The default IBUFGDS I/O standard is LVDS_25.

Clock Buffers/Multiplexers

Clock buffers/multiplexers either drive clock input signals directly onto a clock line

(BUFG) or optionally provide a multiplexer to switch between two unrelated, possibly

asynchronous clock signals (BUFGMUX).

Each BUFGMUX element, shown in Figure 2-5, is a 2-to-1 multiplexer. The select line, S,

chooses which of the two inputs, I0 or I1, drives the BUFGMUX output signal, O, as

described in Table 2-5. As specified in each data sheet’s “DC and Switching

Characteristics” section, the S input has a setup time requirement. It also has

programmable polarity.

BUFGMUX

I0

O

I1

S

UG331_c4_05_080906

Figure 2-5: BUFGMUX Clock Multiplexer

Table 2-5: BUFGMUX Select Mechanism

S Input O Output

0 I0 Input

1 I1 Input

Spartan-3 Generation FPGA User Guide www.xilinx.com 53

UG331 (v1.8) June 13, 2011

You might also like

- IOM NetProDual Daikin Rev 4 PDFDocument15 pagesIOM NetProDual Daikin Rev 4 PDFVin Ken0% (1)

- BUFGMUX Connection DetailsDocument1 pageBUFGMUX Connection DetailsThiện KhiêmNo ratings yet

- BUFGMUX Multiplexing Details: Chapter 2: Using Global Clock ResourcesDocument1 pageBUFGMUX Multiplexing Details: Chapter 2: Using Global Clock ResourcesThiện KhiêmNo ratings yet

- Verification of Gates Experimaent: Digital Logic Design Lab ManualDocument5 pagesVerification of Gates Experimaent: Digital Logic Design Lab ManualRana jamshaid Rana jamshaidNo ratings yet

- GalatmelDocument26 pagesGalatmelNacho RomanelloNo ratings yet

- DT Ica Booklet Final 2024-25 Sem-I With BorderDocument67 pagesDT Ica Booklet Final 2024-25 Sem-I With BorderAvinash HaraleNo ratings yet

- Lab 01Document6 pagesLab 01MUSKAN AMEER UD DINNo ratings yet

- Format Laporan Praktikum PLCDocument4 pagesFormat Laporan Praktikum PLCDevis anugraNo ratings yet

- Islamic University Faculty of Engineering Department of Electrical EngineeringDocument10 pagesIslamic University Faculty of Engineering Department of Electrical Engineering676vyncfwxNo ratings yet

- Atf16v8cz 15puDocument26 pagesAtf16v8cz 15puatomo atomoNo ratings yet

- Bufgce and Bufgce - 1: XST Synthesis of Clock BuffersDocument1 pageBufgce and Bufgce - 1: XST Synthesis of Clock BuffersThiện KhiêmNo ratings yet

- Datasheet G16V8ADocument23 pagesDatasheet G16V8Aj.luis.cf3125No ratings yet

- Result PW3Document15 pagesResult PW3Mohd Shahrul EffendiNo ratings yet

- Using Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Document1 pageUsing Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Thiện KhiêmNo ratings yet

- Felices PLC Module ActivityDocument22 pagesFelices PLC Module ActivityRessie FelicesNo ratings yet

- David PLC Module ActivityDocument22 pagesDavid PLC Module ActivityRessie FelicesNo ratings yet

- High-Speed Complex Programmable Logic Device ATF750LVC: FeaturesDocument19 pagesHigh-Speed Complex Programmable Logic Device ATF750LVC: FeaturesEdwin RojasNo ratings yet

- High-Speed Complex Programmable Logic Device ATF750LVC: FeaturesDocument20 pagesHigh-Speed Complex Programmable Logic Device ATF750LVC: FeaturesYaju JotosNo ratings yet

- ATF2500C CPLD Family Datasheet ATF2500C: FeaturesDocument24 pagesATF2500C CPLD Family Datasheet ATF2500C: FeaturesAngel PardinesNo ratings yet

- Pasos para Implementar Un Proyecto en RSLOGIX 500Document8 pagesPasos para Implementar Un Proyecto en RSLOGIX 500Raul Rigoberto RoqueNo ratings yet

- 1SXU172024L0201 PlutoD20Document2 pages1SXU172024L0201 PlutoD20FaizFzNo ratings yet

- Horloge Geant Kit InstructionsDocument16 pagesHorloge Geant Kit Instructionsthierry.francois.1965No ratings yet

- ATF22V10C DatasheetDocument22 pagesATF22V10C DatasheetfreeeflyerNo ratings yet

- Digital I/O Programming Using PPIDocument5 pagesDigital I/O Programming Using PPIعسم ساماNo ratings yet

- 1-8 DemuxDocument8 pages1-8 DemuxNuke-Comm LeakageNo ratings yet

- Modified DLD Lab ManualsDocument40 pagesModified DLD Lab ManualsASHEESH TiwariNo ratings yet

- SACURAT CPP107 Laboratory1Document6 pagesSACURAT CPP107 Laboratory1Norjane Kyla SacuratNo ratings yet

- (Vega-ENG) ITF400 Serial Expansion Board V3 Rev.2Document4 pages(Vega-ENG) ITF400 Serial Expansion Board V3 Rev.2mahfoud ascenseurs100% (1)

- Abb Manual Change Over and Transfer Switches Ot CDocument40 pagesAbb Manual Change Over and Transfer Switches Ot CNicolaos MavrogenisNo ratings yet

- 8255 8254Document102 pages8255 8254Vamsi KrishnaNo ratings yet

- Guia de Instalação Das Expansões cfw11Document21 pagesGuia de Instalação Das Expansões cfw11Tiago ContagemNo ratings yet

- PLC 3Document22 pagesPLC 3api-3760396No ratings yet

- Final Notes Combined PDFDocument177 pagesFinal Notes Combined PDFDebanshu SamalNo ratings yet

- ACOE347 Exam Sp21Document5 pagesACOE347 Exam Sp21Mamas VartholomeouNo ratings yet

- Report 1Document32 pagesReport 1Narendra AchariNo ratings yet

- Digital Logic Circuits Unit 3 NotesDocument29 pagesDigital Logic Circuits Unit 3 NotesUnitedglobe newsNo ratings yet

- Fdocuments - in - PLC Programming A Ladder L N Switch Motor Ladder Diagram Power Supply L NDocument21 pagesFdocuments - in - PLC Programming A Ladder L N Switch Motor Ladder Diagram Power Supply L NHoang Nam NguyenNo ratings yet

- ATF16V8B, ATF16V8BQ, and ATF16V8BQL: FeaturesDocument27 pagesATF16V8B, ATF16V8BQ, and ATF16V8BQL: FeaturesSimilinga MnyongeNo ratings yet

- Instructions: V: +5V 7486 (Xorgate) 7408 (Andgate)Document1 pageInstructions: V: +5V 7486 (Xorgate) 7408 (Andgate)056S7HRITIK GUPTANo ratings yet

- Virtual Labs7Document1 pageVirtual Labs7056S7HRITIK GUPTANo ratings yet

- Atf1508 PDFDocument31 pagesAtf1508 PDFPhong DoNo ratings yet

- Programming A PLCDocument20 pagesProgramming A PLCamanda christineNo ratings yet

- Digital Microprocessor Lab Manual 5th SemDocument26 pagesDigital Microprocessor Lab Manual 5th SemRonit ChowdhuryNo ratings yet

- Memory DataSheetDocument10 pagesMemory DataSheetNguyễn Ngọc HuyNo ratings yet

- Test 3 Skee1223 20142015-2 SolutionsDocument4 pagesTest 3 Skee1223 20142015-2 SolutionsMr KNo ratings yet

- PLC Fault Contact Protection Diagram1Document1 pagePLC Fault Contact Protection Diagram1shivakalyan yadavNo ratings yet

- Example of A Combinatorial Circuit: A Multiplexer (MUX)Document5 pagesExample of A Combinatorial Circuit: A Multiplexer (MUX)Rishi BatraNo ratings yet

- Example of A Combinatorial Circuit: A Multiplexer (MUX)Document18 pagesExample of A Combinatorial Circuit: A Multiplexer (MUX)jangid_mohanNo ratings yet

- 520BID01 DS enDocument5 pages520BID01 DS enDJ ThangNo ratings yet

- 5.2 Multiplexers and DemultiplexerDocument17 pages5.2 Multiplexers and DemultiplexerVedantNo ratings yet

- Lab Report 2 Digital SystemDocument9 pagesLab Report 2 Digital Systemmuhammad adibuddinNo ratings yet

- Exp 1Document11 pagesExp 1Swapnil SahaNo ratings yet

- Input Output I F 0 1 Inputs Output A B F 0 0 1 0 0 1 1 1: Logic GatesDocument2 pagesInput Output I F 0 1 Inputs Output A B F 0 0 1 0 0 1 1 1: Logic GatesSam JordanNo ratings yet

- AOI FeatureDocument10 pagesAOI Featurekabraham.abinNo ratings yet

- ATF2500C CPLD Family Datasheet ATF2500C: FeaturesDocument9 pagesATF2500C CPLD Family Datasheet ATF2500C: FeaturesSolikin AjNo ratings yet

- Fanuc Series 0: Serial Line ParametersDocument3 pagesFanuc Series 0: Serial Line Parametersferjani ahmedNo ratings yet

- Ejemplo 2 RSLOGIX 500Document4 pagesEjemplo 2 RSLOGIX 500Raul Rigoberto RoqueNo ratings yet

- 1-Of-8 Decoder/demultiplexer: Integrated CircuitsDocument9 pages1-Of-8 Decoder/demultiplexer: Integrated CircuitsedissonNo ratings yet

- Power Generation: Application of AutomationDocument20 pagesPower Generation: Application of AutomationABVSAINo ratings yet

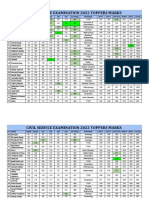

- Selected Candidates Marks CSE 2022Document6 pagesSelected Candidates Marks CSE 2022hara vardhan reddy naruNo ratings yet

- Nega Bizuye To New Cobble RoadDocument36 pagesNega Bizuye To New Cobble RoadAsmerom MosinehNo ratings yet

- 4.a Thing of BeautyDocument10 pages4.a Thing of Beautysrilakshmisuresh031No ratings yet

- 32 WindingDocument12 pages32 WindingVenkat PrasannaNo ratings yet

- VC-210 Service Manual - B PDFDocument12 pagesVC-210 Service Manual - B PDFdofaneiteNo ratings yet

- Illustrative List by Category of Household/Urban Hazardous SubstancesDocument2 pagesIllustrative List by Category of Household/Urban Hazardous SubstancesJima JamNo ratings yet

- Introduction To Tropical Meteorology Bing 1-Dikonversi PDFDocument62 pagesIntroduction To Tropical Meteorology Bing 1-Dikonversi PDFDaniel InversoNo ratings yet

- Taguchi Review LiteratureDocument6 pagesTaguchi Review LiteraturepsprajkotNo ratings yet

- Never On SundayDocument4 pagesNever On Sundaybrigitte jacquotNo ratings yet

- Batakundi SapphiresDocument34 pagesBatakundi SapphiresNaveed NaseerNo ratings yet

- IEC 61000-4-4 Burst Electrical Fast Transient / Burst Immunity TestDocument64 pagesIEC 61000-4-4 Burst Electrical Fast Transient / Burst Immunity TestopinzonNo ratings yet

- Pangasinan DicstionaryDocument9 pagesPangasinan DicstionaryAj Samera DiazNo ratings yet

- TestDocument9 pagesTestNga VũNo ratings yet

- Baaladhi Deepthanadhi Lajitadhi SayanadhiDocument4 pagesBaaladhi Deepthanadhi Lajitadhi SayanadhiPeter NovakNo ratings yet

- (Fatigue of Aircraft Structures) Fatigue Damage of Rivet Joints in The Condition of Stable Cyclic LoadDocument11 pages(Fatigue of Aircraft Structures) Fatigue Damage of Rivet Joints in The Condition of Stable Cyclic LoadJosue NietoNo ratings yet

- Epistemology 2Document43 pagesEpistemology 2Mohamad Nadi NorazemiNo ratings yet

- Advances in Robot KinematicsDocument1 pageAdvances in Robot KinematicsLarbi ElbakkaliNo ratings yet

- Livingston County Eclipse GuideDocument4 pagesLivingston County Eclipse GuideThe Livingston County NewsNo ratings yet

- Cobas C 311 Analyzer: Operator's Manual Software Version 01-04Document590 pagesCobas C 311 Analyzer: Operator's Manual Software Version 01-04khoangsachNo ratings yet

- N4のことばDocument18 pagesN4のことばFergianoNo ratings yet

- Winning Woodwinds!: Beginning Band Method Book Supplement For: FluteDocument49 pagesWinning Woodwinds!: Beginning Band Method Book Supplement For: Flutewe weNo ratings yet

- Binh Long OFFICIAL TEST FOR OLYMPIC 10-2018Document13 pagesBinh Long OFFICIAL TEST FOR OLYMPIC 10-2018Phuong Uyenn0% (1)

- The White Path: Buddhist Church of FowlerDocument8 pagesThe White Path: Buddhist Church of FowlerAnonymous C7r9WMRlNo ratings yet

- Tos DRRDocument2 pagesTos DRRRyan San Luis100% (2)

- CS 701 Research Paper (MS150200090)Document7 pagesCS 701 Research Paper (MS150200090)Mian Saeed RafiqueNo ratings yet

- Lecture Poultry Chicken NC IiDocument34 pagesLecture Poultry Chicken NC IiNichole Kyla Enriquez100% (1)

- HFX Manual ENDocument40 pagesHFX Manual ENmohammad AshrafNo ratings yet

- Jurnal Belimbing WuluhDocument6 pagesJurnal Belimbing WuluhPuspitasari NurulNo ratings yet

- Logic DiagramDocument1 pageLogic DiagramkapsarcNo ratings yet