Professional Documents

Culture Documents

Global Clock Resources: Clocking Infrastructure

Global Clock Resources: Clocking Infrastructure

Uploaded by

Thiện KhiêmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Global Clock Resources: Clocking Infrastructure

Global Clock Resources: Clocking Infrastructure

Uploaded by

Thiện KhiêmCopyright:

Available Formats

R

Chapter 2: Using Global Clock Resources

Global Clock Resources

The global clock resources consist of three connected components: GCLK Global Clock

input pads, BUFGMUX Global Clock Multiplexers, and Global Clock routing. See

Figure 2-1.

GCLK BUFGMUX

Pad Clocks

Global

DCM Routing

Double

Lines

UG331_c2_01_100209

Figure 2-1: Overall View of Clock Connections

The primary clock path is shown with bold lines, with a dedicated clock pad (GCLK)

driving a global clock buffer (BUFGMUX) that connects through global routing resources

to clock inputs on flip-flops and other clocked elements. The GCLK pads can be used as

general-purpose I/O, and include the LHCLK and RHCLK inputs described later. A DCM

can be inserted into the path between the clock pad and clock buffer to manipulate the

clock, or the DCM can acquire the clock signal from general-purpose resources. The

BUFGMUX can multiplex between two clock sources or be used as a simple BUFG clock

buffer. The clock buffer can only drive the clock routing resources, which in turn can only

drive clock inputs. However, clock inputs on flip-flops can also come from general-

purpose routing, although their use is not recommended due to higher skew.

Clocking Infrastructure

The detailed Spartan-3E and Extended Spartan-3A family clocking infrastructure is shown

in Figure 2-2.

46 www.xilinx.com Spartan-3 Generation FPGA User Guide

UG331 (v1.8) June 13, 2011

You might also like

- Am Jur 2d Bills and NotesDocument899 pagesAm Jur 2d Bills and NotesMichael Jones91% (11)

- Onboard and Ground Station Telemetry Architecture Design For A LEO NanosatelliteDocument18 pagesOnboard and Ground Station Telemetry Architecture Design For A LEO NanosatelliteEBEN EZERNo ratings yet

- SF7 Tracker Control System - GTD Rev6 PDFDocument16 pagesSF7 Tracker Control System - GTD Rev6 PDFvishalbhavar1100% (2)

- Bicycling WorldDocument15 pagesBicycling WorldKarl Angelo ArrietaNo ratings yet

- Clock GateDocument19 pagesClock Gateamma4manuNo ratings yet

- Bruker: AQR/P MainframeDocument69 pagesBruker: AQR/P MainframeFer GuNo ratings yet

- SKYLON User Manual Rev1Document52 pagesSKYLON User Manual Rev1Jarek JaworskiNo ratings yet

- BUFGMUX Outputs: Quadrant Clock RoutingDocument1 pageBUFGMUX Outputs: Quadrant Clock RoutingThiện KhiêmNo ratings yet

- Using Dedicated Clock Inputs in A Design: IbufgDocument1 pageUsing Dedicated Clock Inputs in A Design: IbufgThiện KhiêmNo ratings yet

- PS 5GRU UserGuide-S-Plane R3.0.0EDocument14 pagesPS 5GRU UserGuide-S-Plane R3.0.0EShailesh YadavNo ratings yet

- A New Placement and Integration Method of UPQC To Improve The Power Quality in DG NetworkDocument6 pagesA New Placement and Integration Method of UPQC To Improve The Power Quality in DG NetworkDr. Gollapalli NareshNo ratings yet

- Ug472 7series ClockingDocument114 pagesUg472 7series ClockingReinaldo AlejoNo ratings yet

- 32 Landing GearDocument190 pages32 Landing Gearhakoj29142No ratings yet

- BITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE IsDocument3 pagesBITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE Ismantenimientotalmaoma032No ratings yet

- Ug472 7series ClockingDocument112 pagesUg472 7series Clockingwert1a2No ratings yet

- Flexray 2Document20 pagesFlexray 2preetilathaNo ratings yet

- Using Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Document1 pageUsing Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Thiện KhiêmNo ratings yet

- Teleprotección 85Document20 pagesTeleprotección 85ANDREA LILIANA BAUTISTA ACEVEDONo ratings yet

- Programmable Logic Design Grzegorz Budzy Ń L Ecture 10: Fpga Clocking SchemesDocument70 pagesProgrammable Logic Design Grzegorz Budzy Ń L Ecture 10: Fpga Clocking SchemesTechy GuysNo ratings yet

- 351 Sect 09 BtrackDocument16 pages351 Sect 09 BtrackNathan BukoskiNo ratings yet

- 33 LightsDocument182 pages33 Lightshocine seghilaniNo ratings yet

- Recording Option: Operating Instructions Hkcu-Rec55Document34 pagesRecording Option: Operating Instructions Hkcu-Rec55simon.lctoddNo ratings yet

- GPS PPT 1 of 4Document11 pagesGPS PPT 1 of 4Sushil BhanNo ratings yet

- A 4-Ghz 130-Nm Address Generation Unit With 32-Bit Sparse-Tree Adder CoreDocument7 pagesA 4-Ghz 130-Nm Address Generation Unit With 32-Bit Sparse-Tree Adder CoreSubodh SinghalNo ratings yet

- 32 Landing GearDocument190 pages32 Landing GearLuiz Fernando Mibach100% (1)

- F650man IDocument553 pagesF650man Iaurel_c12-1No ratings yet

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Document16 pagesOsmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Tomás BurónNo ratings yet

- 2.5.3 Gating Signals: 2.6 Reset Design StrategyDocument11 pages2.5.3 Gating Signals: 2.6 Reset Design StrategyChaitanya NittaNo ratings yet

- Optimal DCM Clock and External Feedback InputsDocument1 pageOptimal DCM Clock and External Feedback InputsThiện KhiêmNo ratings yet

- 21-22 Satellites ExosDocument1 page21-22 Satellites ExosBalaji SohanNo ratings yet

- Design Considerations of Phase-Locked Loop Systems For Spread Spectrum Clock Generation CompatibilityDocument6 pagesDesign Considerations of Phase-Locked Loop Systems For Spread Spectrum Clock Generation CompatibilitygezahegnNo ratings yet

- Common Path Pessimism Removal An Industry PerspectiveDocument4 pagesCommon Path Pessimism Removal An Industry PerspectiveReddySaiNo ratings yet

- Clock Setup and Hold Timing: Chapter 2: Using Global Clock ResourcesDocument1 pageClock Setup and Hold Timing: Chapter 2: Using Global Clock ResourcesThiện KhiêmNo ratings yet

- Vdocuments - MX 2g Flexi BSC HardwareDocument31 pagesVdocuments - MX 2g Flexi BSC HardwareAndrea UsaiNo ratings yet

- RNC - Radio Network Controller: Presented byDocument12 pagesRNC - Radio Network Controller: Presented byMix RuksinNo ratings yet

- Design of Clock Distribution Networks-Case StudyDocument3 pagesDesign of Clock Distribution Networks-Case StudyPino Watson PisoloNo ratings yet

- Asynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-FlopsDocument6 pagesAsynchronous Data Sampling Within Clock-Gated Double Edge Triggered Flip-Flopsblessysara16No ratings yet

- 129639435Document23 pages129639435preetish.kamath89No ratings yet

- gp39 v3 01 and scx21 GuideDocument5 pagesgp39 v3 01 and scx21 GuidelukinugrohohadihadiNo ratings yet

- TSGS2#3 (99) 070Document3 pagesTSGS2#3 (99) 070Asif HossainNo ratings yet

- 10 IPS of Dawn SpaceDocument11 pages10 IPS of Dawn SpaceRocco IbhNo ratings yet

- Intro To Edge-GprsDocument56 pagesIntro To Edge-GprsGhulam RabbaniNo ratings yet

- Demonstrating The Flexibility Provided by GOOSE Messaging For Protection and Control Applications in An Industrial Power SystemDocument7 pagesDemonstrating The Flexibility Provided by GOOSE Messaging For Protection and Control Applications in An Industrial Power SystemmeeNo ratings yet

- Lab 2Document5 pagesLab 2Usama MalikNo ratings yet

- 1756HP-TIME User Manual v1.00.02Document33 pages1756HP-TIME User Manual v1.00.02Adnan Tahir DarNo ratings yet

- Perubahan Sistem Kontrol Dari PLC Ke Dcs Pada Grup Bag Filter 563-Bf1Document12 pagesPerubahan Sistem Kontrol Dari PLC Ke Dcs Pada Grup Bag Filter 563-Bf1Rizal SofyanNo ratings yet

- BSC/RNC Clock Feature Parameter DescriptionDocument21 pagesBSC/RNC Clock Feature Parameter DescriptionSam FicherNo ratings yet

- Application Note AN092: Measuring Bluetooth® Low Energy Power ConsumptionDocument24 pagesApplication Note AN092: Measuring Bluetooth® Low Energy Power ConsumptionAngelNo ratings yet

- GCS 222 MRL System Start Up GCS 222 MRL - 2012-07-03Document69 pagesGCS 222 MRL System Start Up GCS 222 MRL - 2012-07-03djidjelli nassir50% (2)

- Board Type O&M Board Omuc Board NameDocument20 pagesBoard Type O&M Board Omuc Board NameVikas GuptaNo ratings yet

- Physical Uplink Shared Channel PUSCH Closed-Loop PDocument33 pagesPhysical Uplink Shared Channel PUSCH Closed-Loop PAnonymous cbphWU0Y2No ratings yet

- Other Well Logs: Vizibg IK.Document26 pagesOther Well Logs: Vizibg IK.ZubairNo ratings yet

- Volume 2 of 3 (Substation Part) PDFDocument502 pagesVolume 2 of 3 (Substation Part) PDFMd. Mohiuddin Al-MahmudNo ratings yet

- Fast Return and Interfreq MLBDocument5 pagesFast Return and Interfreq MLBBagoes SidhartaNo ratings yet

- Electrical Load Analysis GFC 700 Afcs Diamond Da 40: P/N 005-00336-05 Rev. 1Document15 pagesElectrical Load Analysis GFC 700 Afcs Diamond Da 40: P/N 005-00336-05 Rev. 1cam cotNo ratings yet

- Eacop Uganda Rap Chapter 2 Project DescriptionDocument24 pagesEacop Uganda Rap Chapter 2 Project DescriptionМединаNo ratings yet

- Sh080373eam (050 100) PDFDocument51 pagesSh080373eam (050 100) PDFSergio Ernesto López OrellanaNo ratings yet

- How Does Clock Reconvergence Pessimism Removal (CRPR) Handle Dynamically Switched Related ClocksDocument4 pagesHow Does Clock Reconvergence Pessimism Removal (CRPR) Handle Dynamically Switched Related ClocksmanojkumarNo ratings yet

- Low Power Clock-Synchronizer For SOC With Delay Line Controller (DLC) in 45nm CMOS TechnologyDocument6 pagesLow Power Clock-Synchronizer For SOC With Delay Line Controller (DLC) in 45nm CMOS TechnologysrivathsavaNo ratings yet

- Central Expressway S2 Annual Report-2017Document8 pagesCentral Expressway S2 Annual Report-2017KumaraNo ratings yet

- Simulation-Based Performance Analysis of HSDPA For UMTS NetworksDocument5 pagesSimulation-Based Performance Analysis of HSDPA For UMTS NetworksfireincitadelNo ratings yet

- Study of Cable CrimpingDocument12 pagesStudy of Cable Crimpingpragya bagdeNo ratings yet

- New Text DocumentDocument2 pagesNew Text DocumentFitzgerald KeaneNo ratings yet

- Universal: Make NoDocument8 pagesUniversal: Make NoChinmaya BeheraNo ratings yet

- Neha Nylon 6,6Document16 pagesNeha Nylon 6,6sakshi ranadeNo ratings yet

- Service: FABIA 2000Document52 pagesService: FABIA 2000Mantenimientos IndustrialesNo ratings yet

- Space Frame StructureDocument40 pagesSpace Frame StructureB-05 ISHA PATELNo ratings yet

- HP HPE6-A70 March 2023-v1.2Document33 pagesHP HPE6-A70 March 2023-v1.2CCIEHOMERNo ratings yet

- 1MRK511313-BEN C en Product Guide Bay Control REC670 2.0Document107 pages1MRK511313-BEN C en Product Guide Bay Control REC670 2.0A1410 15No ratings yet

- Fa11 FinalDocument21 pagesFa11 FinalSri PatNo ratings yet

- Field Experience B: Principal Interview 1Document7 pagesField Experience B: Principal Interview 1Raymond BartonNo ratings yet

- Polycom CX5100 Unified Conference Station: Data SheetDocument3 pagesPolycom CX5100 Unified Conference Station: Data SheetvariNo ratings yet

- Assessment & Development Centre Workshop: Psyasia International'SDocument5 pagesAssessment & Development Centre Workshop: Psyasia International'SAditya BagaswaraNo ratings yet

- Aegis Emergency Data Sheet1Document2 pagesAegis Emergency Data Sheet1Armando RamirezNo ratings yet

- Experiment-1 Input and Output Characteristics of BJT in Ce ConfigurationDocument8 pagesExperiment-1 Input and Output Characteristics of BJT in Ce ConfigurationAditya GudlaNo ratings yet

- NOC23 EE49 Assignment Week03 v0.1Document4 pagesNOC23 EE49 Assignment Week03 v0.1Get Into StudyNo ratings yet

- Tax 1 DigestsDocument165 pagesTax 1 DigestsJm Palisoc100% (5)

- Overview of Central Excise Law and ProceduresDocument38 pagesOverview of Central Excise Law and ProceduresRavikumarrd RaviNo ratings yet

- Field & Stream - January 2018 USA PDFDocument100 pagesField & Stream - January 2018 USA PDFCata BscNo ratings yet

- Challenges of EntrepreneursDocument2 pagesChallenges of EntrepreneursElloïx JennerNo ratings yet

- Biodiversity ReportDocument12 pagesBiodiversity ReportjillianNo ratings yet

- Using Sage 50 Accounting 2016 1st Edition Purbhoo Solutions ManualDocument28 pagesUsing Sage 50 Accounting 2016 1st Edition Purbhoo Solutions Manualconsignedurylic75hi100% (28)

- Accenture Corporate Crisis ManagementDocument16 pagesAccenture Corporate Crisis Managementmukosino100% (1)

- FIrst Discoveries Workbook Unit 5Document6 pagesFIrst Discoveries Workbook Unit 5Felipe Herrera ZentenoNo ratings yet

- Technical Manual Gear Hub Systems: EnglishDocument84 pagesTechnical Manual Gear Hub Systems: EnglishЕвгений ЕвсеевNo ratings yet

- Hydrocarbon Potential of Jabo FieldDocument8 pagesHydrocarbon Potential of Jabo FieldFurqanButtNo ratings yet

- Bronson at Home Advanced Illness Management ProgramDocument15 pagesBronson at Home Advanced Illness Management Programapi-262307733No ratings yet

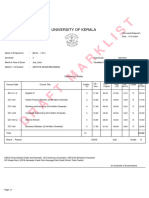

- Draft Marklist: University of KeralaDocument1 pageDraft Marklist: University of Keralamuraliadithya4No ratings yet

- Aeon7200 Service Manual-V00.01-A4Document37 pagesAeon7200 Service Manual-V00.01-A4annaya kitaNo ratings yet