Professional Documents

Culture Documents

BUFGMUX Outputs: Quadrant Clock Routing

BUFGMUX Outputs: Quadrant Clock Routing

Uploaded by

Thiện KhiêmCopyright:

Available Formats

You might also like

- Design of Arithmetic Calculator Using FpgaDocument58 pagesDesign of Arithmetic Calculator Using FpgavikramNo ratings yet

- CS2001 Group Project Report FinalDocument8 pagesCS2001 Group Project Report FinalHugh MatthewsNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- SCF File Creation For BBU Swap - V10a - Sreeram PDFDocument8 pagesSCF File Creation For BBU Swap - V10a - Sreeram PDFsreeram100% (1)

- ChartsDocument40 pagesChartsdenlopviperNo ratings yet

- Fiat Punto CVTDocument5 pagesFiat Punto CVTvalangelofNo ratings yet

- Global Clock Resources: Clocking InfrastructureDocument1 pageGlobal Clock Resources: Clocking InfrastructureThiện KhiêmNo ratings yet

- Using Dedicated Clock Inputs in A Design: IbufgDocument1 pageUsing Dedicated Clock Inputs in A Design: IbufgThiện KhiêmNo ratings yet

- Optimal DCM Clock and External Feedback InputsDocument1 pageOptimal DCM Clock and External Feedback InputsThiện KhiêmNo ratings yet

- Choosing Top/Bottom and Left-/Right-Half Global Buffers: Other InformationDocument1 pageChoosing Top/Bottom and Left-/Right-Half Global Buffers: Other InformationThiện KhiêmNo ratings yet

- Using Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Document1 pageUsing Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Thiện KhiêmNo ratings yet

- fpga writeupDocument2 pagesfpga writeupHarshini MNo ratings yet

- Xapp024.pdfxilinx XC 3000Document11 pagesXapp024.pdfxilinx XC 3000Rohith RajNo ratings yet

- reportDocument8 pagesreportHarshini MNo ratings yet

- UNITROL 5000 User's Manual Appendix,: Unitrol 5000 AVR Controls ON-LINE Maintenance InstructionsDocument18 pagesUNITROL 5000 User's Manual Appendix,: Unitrol 5000 AVR Controls ON-LINE Maintenance Instructionssaravan1891No ratings yet

- Basic Shift AccumulatorDocument4 pagesBasic Shift AccumulatorThahsin ThahirNo ratings yet

- Lab 2Document5 pagesLab 2Usama MalikNo ratings yet

- BLE 3 Click WebDocument5 pagesBLE 3 Click WebHenrique NunesNo ratings yet

- MKT3811 Week4 03.11.2021 RDocument62 pagesMKT3811 Week4 03.11.2021 REmirhan AlmaNo ratings yet

- B767 ATA 46 Student BookDocument17 pagesB767 ATA 46 Student BookElijah Paul Merto100% (2)

- FPGA TechnologyDocument26 pagesFPGA TechnologyvinaypantraNo ratings yet

- Hkpilot Mega 2.7: Flight Controller Usb/Gyro/Acc/Mag/BaroDocument14 pagesHkpilot Mega 2.7: Flight Controller Usb/Gyro/Acc/Mag/BaroFernando De BenitoNo ratings yet

- Piling The CFC ChartDocument3 pagesPiling The CFC ChartkumarNo ratings yet

- BITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE IsDocument3 pagesBITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE Ismantenimientotalmaoma032No ratings yet

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Document16 pagesOsmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Tomás BurónNo ratings yet

- 351 Sect 09 BtrackDocument16 pages351 Sect 09 BtrackNathan BukoskiNo ratings yet

- Clock Synchronization of BSC ExternallyDocument9 pagesClock Synchronization of BSC ExternallyNguyen Xuan NhamNo ratings yet

- Latticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Document28 pagesLatticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Krishnakumar SomanpillaiNo ratings yet

- Xc4000 Fpga Mod 4Document9 pagesXc4000 Fpga Mod 4ksm_commonNo ratings yet

- Elektro VoiceDocument35 pagesElektro VoicebarayafmNo ratings yet

- Unit Ii: CPLD & Fpga Architecture & ApplicationsDocument20 pagesUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- Ic 693 Cpu 313Document5 pagesIc 693 Cpu 313mubashersaeedNo ratings yet

- APN-C.006 CFC Online enDocument9 pagesAPN-C.006 CFC Online enAbhishek RajputNo ratings yet

- Clock Options On The HC9S08 Family: Application NoteDocument50 pagesClock Options On The HC9S08 Family: Application NoteJuan CarlosNo ratings yet

- ForgeFPGA Configuration Guide v2.1Document20 pagesForgeFPGA Configuration Guide v2.1HnnNo ratings yet

- Simatic S5 318-3UA11 Central Controller Interface Module: ManualDocument37 pagesSimatic S5 318-3UA11 Central Controller Interface Module: ManualAutomacao16No ratings yet

- BFSK PDFDocument5 pagesBFSK PDFRiad Al JuboriNo ratings yet

- Chapt7 1Document43 pagesChapt7 1Prasanna KumarNo ratings yet

- PM9903BPE: Evaluation Board For The SA9903B Energy Metering ICDocument22 pagesPM9903BPE: Evaluation Board For The SA9903B Energy Metering ICGiuseppe VerardoNo ratings yet

- MethodologyDocument18 pagesMethodologyDaukan Chavez AlbercaNo ratings yet

- MC81F4x32: User's ManualDocument198 pagesMC81F4x32: User's ManualRoger CarreroNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- I/A Series Software Foxblock Integrated Control Software: ContinuousDocument24 pagesI/A Series Software Foxblock Integrated Control Software: ContinuousFateh IderNo ratings yet

- AVR On-Line Maintenance InstructionsDocument13 pagesAVR On-Line Maintenance InstructionsAmit BiswasNo ratings yet

- 10 11648 J Jeee 20190702 16Document5 pages10 11648 J Jeee 20190702 16Shawyoo LeeNo ratings yet

- Programmable Controller: - SeriesDocument10 pagesProgrammable Controller: - SeriesBilal JuttNo ratings yet

- FPGA Based 32 Bit ALU For Automatic Antenna Control UnitDocument5 pagesFPGA Based 32 Bit ALU For Automatic Antenna Control UnitMinh DucNo ratings yet

- AN3560Document34 pagesAN3560Henry RodriguezNo ratings yet

- Gulfstream G Iv 300 FMSDocument14 pagesGulfstream G Iv 300 FMSAlvaroNo ratings yet

- DM 4 Land DM 4 Marine Generator Set Control 4189232117 UkDocument34 pagesDM 4 Land DM 4 Marine Generator Set Control 4189232117 UkaugustoronaldNo ratings yet

- Description of PLC Subroutine Library V01.06.00 For: Sinumerik 802DDocument49 pagesDescription of PLC Subroutine Library V01.06.00 For: Sinumerik 802DmagdyfdlNo ratings yet

- Part2 PDFDocument6 pagesPart2 PDFمحيي الدين الكميشىNo ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- Gs33j64e10-01en 009Document19 pagesGs33j64e10-01en 009MobileDickNo ratings yet

- Sinclair QL Service Manual - Sinclair ResearchDocument45 pagesSinclair QL Service Manual - Sinclair Researchabo alasrarNo ratings yet

- 33 LightsDocument182 pages33 Lightshocine seghilaniNo ratings yet

- Auto Reclose - 3 PH Trip - D60 & L90Document3 pagesAuto Reclose - 3 PH Trip - D60 & L90Sandeep sahuNo ratings yet

- Flancter App NoteDocument11 pagesFlancter App NotebigdogguruNo ratings yet

- Solid State Block Proving by Axle Counter (Digital) : Vinay Polepalli, M Anil KumarDocument10 pagesSolid State Block Proving by Axle Counter (Digital) : Vinay Polepalli, M Anil KumarShakeel RanaNo ratings yet

- Abstract:: Figure 1: Basic FPGA ConfigurationDocument4 pagesAbstract:: Figure 1: Basic FPGA ConfigurationEr Nayan PithadiyaNo ratings yet

- Cubesat Kit COTS FM430 Flight ModuleDocument14 pagesCubesat Kit COTS FM430 Flight ModulegunbrownNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- TsubakiDocument45 pagesTsubakiBastanta NainggolanNo ratings yet

- Lavallee & Ide - CatalogDocument36 pagesLavallee & Ide - CatalogCorey.DeGrandchamp6079No ratings yet

- Unified Operating SystemDocument2 pagesUnified Operating SystemMustafa Emre ÇınarNo ratings yet

- 3 4 W Control CablesDocument3 pages3 4 W Control CablesJaya SankaNo ratings yet

- Application Guide 2003 4Document32 pagesApplication Guide 2003 4Carlos PintoNo ratings yet

- Big Data in The Cybersecurity Operations Center: Thomas M. MitchellDocument3 pagesBig Data in The Cybersecurity Operations Center: Thomas M. MitchellBusiness Expert PressNo ratings yet

- ICM CH 6 Answers To Chapter ProblemsDocument2 pagesICM CH 6 Answers To Chapter ProblemsyawahabNo ratings yet

- Husqvarna/Viking Jade 20 Sewing Machine Service ManualDocument42 pagesHusqvarna/Viking Jade 20 Sewing Machine Service ManualiliiexpugnansNo ratings yet

- IMS-19-11 Service Request FormDocument2 pagesIMS-19-11 Service Request FormSubin RoshanNo ratings yet

- 01.+15603 Article+Text PR 1Document15 pages01.+15603 Article+Text PR 1KEYSIA MOREND MAMUKONo ratings yet

- AE510 - 03 NACA 0015 AirfoilDocument25 pagesAE510 - 03 NACA 0015 Airfoilasan09No ratings yet

- İş Makineleri Grubu Periyodik Bakımları (01-30) - 11 - 2021 Tarihli 1'nci Hafta RaporlamalarıDocument1 pageİş Makineleri Grubu Periyodik Bakımları (01-30) - 11 - 2021 Tarihli 1'nci Hafta RaporlamalarıKadir Koray BozyelNo ratings yet

- Part SD200N TenggarongDocument2 pagesPart SD200N TenggarongAndre STANo ratings yet

- Pakistan International School (English Section) : Subject: Physics Grade: 7 Answer Key Chapter 31: CircuitsDocument2 pagesPakistan International School (English Section) : Subject: Physics Grade: 7 Answer Key Chapter 31: CircuitsAHK GAMERNo ratings yet

- Manual 1 Torres AmcotDocument3 pagesManual 1 Torres AmcotRobert HernandezNo ratings yet

- AUSA M50Dx4 Parts ManualDocument216 pagesAUSA M50Dx4 Parts ManualGyl BNo ratings yet

- Install Wooden Door JambDocument14 pagesInstall Wooden Door JambJeanelle SamsonNo ratings yet

- Chapter 3 - Electrons in AtomsDocument16 pagesChapter 3 - Electrons in AtomsNabindra RuwaliNo ratings yet

- Tracer PlusDocument9 pagesTracer PlusAdi ApriadiNo ratings yet

- Calhoun-Whitcomb Design of 2010Document14 pagesCalhoun-Whitcomb Design of 2010Awan AJa100% (1)

- XC968E轮式装载机技术规格书Document5 pagesXC968E轮式装载机技术规格书Yavor KolevskiNo ratings yet

- CE Teaching Load 1st Sem 2022 2023Document15 pagesCE Teaching Load 1st Sem 2022 2023roylandNo ratings yet

- Alcatel 7300 ASAM PDFDocument12 pagesAlcatel 7300 ASAM PDFGuilherme Vilas BoasNo ratings yet

- CIV3703 Transport Engineering (USQ)Document34 pagesCIV3703 Transport Engineering (USQ)hao baiNo ratings yet

- Phenomena of Double RefractionDocument5 pagesPhenomena of Double RefractionMahendra PandaNo ratings yet

- Bomba Denison Serie PremierDocument50 pagesBomba Denison Serie Premiergineslopezruiz100% (1)

- GitHub TrainingDocument21 pagesGitHub Trainingcyberfox786No ratings yet

BUFGMUX Outputs: Quadrant Clock Routing

BUFGMUX Outputs: Quadrant Clock Routing

Uploaded by

Thiện KhiêmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

BUFGMUX Outputs: Quadrant Clock Routing

BUFGMUX Outputs: Quadrant Clock Routing

Uploaded by

Thiện KhiêmCopyright:

Available Formats

R

Quadrant Clock Routing

The four BUFGMUX elements on the top edge are paired together and share inputs from

the eight global clock inputs along the top edge. Each BUFGMUX pair connects to four of

the eight global clock inputs, as shown in Figure 2-2, page 47. This optionally allows

differential inputs to the global clock inputs without wasting a BUFGMUX element.

The connections for the bottom-edge BUFGMUX elements are similar to the top-edge

connections (see Figure 2-11). On the left and right edges, only two clock inputs feed each

pair of BUFGMUX elements.

BUFGMUX Outputs

The BUFGMUX drives the global clock routing, which in turn connects to clock inputs on

device resources. The BUFGMUX can also connect to a DCM, typically used for internal

feedback to the DCM CLKFB input, as shown in Figure 2-12.

Global Digital Clock Global

Buffer Input Manager Clock Buffer

IBUFG BUFG

I O I O Low-Skew

GCLK CLKIN Output Global Clock

Network

DCM

CLKFB

UG331_c4_11_080906

Figure 2-12: Using a DCM to Eliminate Clock Skew

For more details on using the DCMs, see Chapter 3, “Using Digital Clock Managers

(DCMs).”

Spartan-3 Global Clock Buffers

The Spartan-3 family has only eight global clock buffers. Four BUFGMUX elements are

placed at the center of the die’s bottom edge, just above the GCLK0 - GCLK3 inputs. The

remaining four BUFGMUX elements are placed at the center of the die’s top edge, just

below the GCLK4 - GCLK7 inputs. Each pair of BUFGMUX elements shares two sources;

each source feeds the I0 input of one BUFGMUX and the I1 input of the adjacent

BUFGMUX. Thus two completely independent pairs of clock inputs to be multiplexed

could be on the same side of the die but not on the adjacent BUFGMUX elements. For more

details, see the Spartan-3 FPGA data sheet.

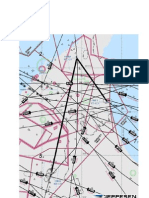

Quadrant Clock Routing

The clock routing within the Spartan-3E and Extended Spartan-3A family is quadrant-

based, as shown in Figure 2-2, page 47. Each clock quadrant supports eight total clock

signals, labeled A through H in Table 2-7 and Figure 2-13. The clock source for an

individual clock line originates either from a global BUFGMUX element along the top and

bottom edges or from a BUFGMUX element along the associated left/right edge, as shown

in Figure 2-13. The clock lines feed the synchronous resource elements (CLBs, IOBs, block

RAM, multipliers, and DCMs) within the quadrant. Those resources have programmable

polarity on the clock input.

Spartan-3 Generation FPGA User Guide www.xilinx.com 59

UG331 (v1.8) June 13, 2011

You might also like

- Design of Arithmetic Calculator Using FpgaDocument58 pagesDesign of Arithmetic Calculator Using FpgavikramNo ratings yet

- CS2001 Group Project Report FinalDocument8 pagesCS2001 Group Project Report FinalHugh MatthewsNo ratings yet

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- SCF File Creation For BBU Swap - V10a - Sreeram PDFDocument8 pagesSCF File Creation For BBU Swap - V10a - Sreeram PDFsreeram100% (1)

- ChartsDocument40 pagesChartsdenlopviperNo ratings yet

- Fiat Punto CVTDocument5 pagesFiat Punto CVTvalangelofNo ratings yet

- Global Clock Resources: Clocking InfrastructureDocument1 pageGlobal Clock Resources: Clocking InfrastructureThiện KhiêmNo ratings yet

- Using Dedicated Clock Inputs in A Design: IbufgDocument1 pageUsing Dedicated Clock Inputs in A Design: IbufgThiện KhiêmNo ratings yet

- Optimal DCM Clock and External Feedback InputsDocument1 pageOptimal DCM Clock and External Feedback InputsThiện KhiêmNo ratings yet

- Choosing Top/Bottom and Left-/Right-Half Global Buffers: Other InformationDocument1 pageChoosing Top/Bottom and Left-/Right-Half Global Buffers: Other InformationThiện KhiêmNo ratings yet

- Using Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Document1 pageUsing Clock Buffers/Multiplexers in A Design: Bufgmux and Bufgmux - 1Thiện KhiêmNo ratings yet

- fpga writeupDocument2 pagesfpga writeupHarshini MNo ratings yet

- Xapp024.pdfxilinx XC 3000Document11 pagesXapp024.pdfxilinx XC 3000Rohith RajNo ratings yet

- reportDocument8 pagesreportHarshini MNo ratings yet

- UNITROL 5000 User's Manual Appendix,: Unitrol 5000 AVR Controls ON-LINE Maintenance InstructionsDocument18 pagesUNITROL 5000 User's Manual Appendix,: Unitrol 5000 AVR Controls ON-LINE Maintenance Instructionssaravan1891No ratings yet

- Basic Shift AccumulatorDocument4 pagesBasic Shift AccumulatorThahsin ThahirNo ratings yet

- Lab 2Document5 pagesLab 2Usama MalikNo ratings yet

- BLE 3 Click WebDocument5 pagesBLE 3 Click WebHenrique NunesNo ratings yet

- MKT3811 Week4 03.11.2021 RDocument62 pagesMKT3811 Week4 03.11.2021 REmirhan AlmaNo ratings yet

- B767 ATA 46 Student BookDocument17 pagesB767 ATA 46 Student BookElijah Paul Merto100% (2)

- FPGA TechnologyDocument26 pagesFPGA TechnologyvinaypantraNo ratings yet

- Hkpilot Mega 2.7: Flight Controller Usb/Gyro/Acc/Mag/BaroDocument14 pagesHkpilot Mega 2.7: Flight Controller Usb/Gyro/Acc/Mag/BaroFernando De BenitoNo ratings yet

- Piling The CFC ChartDocument3 pagesPiling The CFC ChartkumarNo ratings yet

- BITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE IsDocument3 pagesBITE Check of Landing Gear Control Interface Unit (LGCIU) With Use of MCDU To Ensure That Continuous BITE Ismantenimientotalmaoma032No ratings yet

- Osmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Document16 pagesOsmeoisis 2022-09-06 15-33-19PIC - Mid - C - 5Tomás BurónNo ratings yet

- 351 Sect 09 BtrackDocument16 pages351 Sect 09 BtrackNathan BukoskiNo ratings yet

- Clock Synchronization of BSC ExternallyDocument9 pagesClock Synchronization of BSC ExternallyNguyen Xuan NhamNo ratings yet

- Latticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Document28 pagesLatticexp2 Sysclock PLL Design and Usage Guide: March 2012 Technical Note Tn1126Krishnakumar SomanpillaiNo ratings yet

- Xc4000 Fpga Mod 4Document9 pagesXc4000 Fpga Mod 4ksm_commonNo ratings yet

- Elektro VoiceDocument35 pagesElektro VoicebarayafmNo ratings yet

- Unit Ii: CPLD & Fpga Architecture & ApplicationsDocument20 pagesUnit Ii: CPLD & Fpga Architecture & ApplicationsNarasimha Murthy Yayavaram100% (1)

- Ic 693 Cpu 313Document5 pagesIc 693 Cpu 313mubashersaeedNo ratings yet

- APN-C.006 CFC Online enDocument9 pagesAPN-C.006 CFC Online enAbhishek RajputNo ratings yet

- Clock Options On The HC9S08 Family: Application NoteDocument50 pagesClock Options On The HC9S08 Family: Application NoteJuan CarlosNo ratings yet

- ForgeFPGA Configuration Guide v2.1Document20 pagesForgeFPGA Configuration Guide v2.1HnnNo ratings yet

- Simatic S5 318-3UA11 Central Controller Interface Module: ManualDocument37 pagesSimatic S5 318-3UA11 Central Controller Interface Module: ManualAutomacao16No ratings yet

- BFSK PDFDocument5 pagesBFSK PDFRiad Al JuboriNo ratings yet

- Chapt7 1Document43 pagesChapt7 1Prasanna KumarNo ratings yet

- PM9903BPE: Evaluation Board For The SA9903B Energy Metering ICDocument22 pagesPM9903BPE: Evaluation Board For The SA9903B Energy Metering ICGiuseppe VerardoNo ratings yet

- MethodologyDocument18 pagesMethodologyDaukan Chavez AlbercaNo ratings yet

- MC81F4x32: User's ManualDocument198 pagesMC81F4x32: User's ManualRoger CarreroNo ratings yet

- FpgaDocument6 pagesFpgaÁryâñ SinghNo ratings yet

- I/A Series Software Foxblock Integrated Control Software: ContinuousDocument24 pagesI/A Series Software Foxblock Integrated Control Software: ContinuousFateh IderNo ratings yet

- AVR On-Line Maintenance InstructionsDocument13 pagesAVR On-Line Maintenance InstructionsAmit BiswasNo ratings yet

- 10 11648 J Jeee 20190702 16Document5 pages10 11648 J Jeee 20190702 16Shawyoo LeeNo ratings yet

- Programmable Controller: - SeriesDocument10 pagesProgrammable Controller: - SeriesBilal JuttNo ratings yet

- FPGA Based 32 Bit ALU For Automatic Antenna Control UnitDocument5 pagesFPGA Based 32 Bit ALU For Automatic Antenna Control UnitMinh DucNo ratings yet

- AN3560Document34 pagesAN3560Henry RodriguezNo ratings yet

- Gulfstream G Iv 300 FMSDocument14 pagesGulfstream G Iv 300 FMSAlvaroNo ratings yet

- DM 4 Land DM 4 Marine Generator Set Control 4189232117 UkDocument34 pagesDM 4 Land DM 4 Marine Generator Set Control 4189232117 UkaugustoronaldNo ratings yet

- Description of PLC Subroutine Library V01.06.00 For: Sinumerik 802DDocument49 pagesDescription of PLC Subroutine Library V01.06.00 For: Sinumerik 802DmagdyfdlNo ratings yet

- Part2 PDFDocument6 pagesPart2 PDFمحيي الدين الكميشىNo ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- Gs33j64e10-01en 009Document19 pagesGs33j64e10-01en 009MobileDickNo ratings yet

- Sinclair QL Service Manual - Sinclair ResearchDocument45 pagesSinclair QL Service Manual - Sinclair Researchabo alasrarNo ratings yet

- 33 LightsDocument182 pages33 Lightshocine seghilaniNo ratings yet

- Auto Reclose - 3 PH Trip - D60 & L90Document3 pagesAuto Reclose - 3 PH Trip - D60 & L90Sandeep sahuNo ratings yet

- Flancter App NoteDocument11 pagesFlancter App NotebigdogguruNo ratings yet

- Solid State Block Proving by Axle Counter (Digital) : Vinay Polepalli, M Anil KumarDocument10 pagesSolid State Block Proving by Axle Counter (Digital) : Vinay Polepalli, M Anil KumarShakeel RanaNo ratings yet

- Abstract:: Figure 1: Basic FPGA ConfigurationDocument4 pagesAbstract:: Figure 1: Basic FPGA ConfigurationEr Nayan PithadiyaNo ratings yet

- Cubesat Kit COTS FM430 Flight ModuleDocument14 pagesCubesat Kit COTS FM430 Flight ModulegunbrownNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- TsubakiDocument45 pagesTsubakiBastanta NainggolanNo ratings yet

- Lavallee & Ide - CatalogDocument36 pagesLavallee & Ide - CatalogCorey.DeGrandchamp6079No ratings yet

- Unified Operating SystemDocument2 pagesUnified Operating SystemMustafa Emre ÇınarNo ratings yet

- 3 4 W Control CablesDocument3 pages3 4 W Control CablesJaya SankaNo ratings yet

- Application Guide 2003 4Document32 pagesApplication Guide 2003 4Carlos PintoNo ratings yet

- Big Data in The Cybersecurity Operations Center: Thomas M. MitchellDocument3 pagesBig Data in The Cybersecurity Operations Center: Thomas M. MitchellBusiness Expert PressNo ratings yet

- ICM CH 6 Answers To Chapter ProblemsDocument2 pagesICM CH 6 Answers To Chapter ProblemsyawahabNo ratings yet

- Husqvarna/Viking Jade 20 Sewing Machine Service ManualDocument42 pagesHusqvarna/Viking Jade 20 Sewing Machine Service ManualiliiexpugnansNo ratings yet

- IMS-19-11 Service Request FormDocument2 pagesIMS-19-11 Service Request FormSubin RoshanNo ratings yet

- 01.+15603 Article+Text PR 1Document15 pages01.+15603 Article+Text PR 1KEYSIA MOREND MAMUKONo ratings yet

- AE510 - 03 NACA 0015 AirfoilDocument25 pagesAE510 - 03 NACA 0015 Airfoilasan09No ratings yet

- İş Makineleri Grubu Periyodik Bakımları (01-30) - 11 - 2021 Tarihli 1'nci Hafta RaporlamalarıDocument1 pageİş Makineleri Grubu Periyodik Bakımları (01-30) - 11 - 2021 Tarihli 1'nci Hafta RaporlamalarıKadir Koray BozyelNo ratings yet

- Part SD200N TenggarongDocument2 pagesPart SD200N TenggarongAndre STANo ratings yet

- Pakistan International School (English Section) : Subject: Physics Grade: 7 Answer Key Chapter 31: CircuitsDocument2 pagesPakistan International School (English Section) : Subject: Physics Grade: 7 Answer Key Chapter 31: CircuitsAHK GAMERNo ratings yet

- Manual 1 Torres AmcotDocument3 pagesManual 1 Torres AmcotRobert HernandezNo ratings yet

- AUSA M50Dx4 Parts ManualDocument216 pagesAUSA M50Dx4 Parts ManualGyl BNo ratings yet

- Install Wooden Door JambDocument14 pagesInstall Wooden Door JambJeanelle SamsonNo ratings yet

- Chapter 3 - Electrons in AtomsDocument16 pagesChapter 3 - Electrons in AtomsNabindra RuwaliNo ratings yet

- Tracer PlusDocument9 pagesTracer PlusAdi ApriadiNo ratings yet

- Calhoun-Whitcomb Design of 2010Document14 pagesCalhoun-Whitcomb Design of 2010Awan AJa100% (1)

- XC968E轮式装载机技术规格书Document5 pagesXC968E轮式装载机技术规格书Yavor KolevskiNo ratings yet

- CE Teaching Load 1st Sem 2022 2023Document15 pagesCE Teaching Load 1st Sem 2022 2023roylandNo ratings yet

- Alcatel 7300 ASAM PDFDocument12 pagesAlcatel 7300 ASAM PDFGuilherme Vilas BoasNo ratings yet

- CIV3703 Transport Engineering (USQ)Document34 pagesCIV3703 Transport Engineering (USQ)hao baiNo ratings yet

- Phenomena of Double RefractionDocument5 pagesPhenomena of Double RefractionMahendra PandaNo ratings yet

- Bomba Denison Serie PremierDocument50 pagesBomba Denison Serie Premiergineslopezruiz100% (1)

- GitHub TrainingDocument21 pagesGitHub Trainingcyberfox786No ratings yet