Professional Documents

Culture Documents

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Uploaded by

Thiện KhiêmCopyright:

Available Formats

You might also like

- 787 Circuit Breakers ListDocument144 pages787 Circuit Breakers Listlalo7772100% (3)

- 1NZFE PinoutDocument1 page1NZFE PinoutSet Paing100% (1)

- Annexure A Price Schedule STSDocument188 pagesAnnexure A Price Schedule STSRuslan Ibragimov100% (1)

- Preservation Proceedure (SAMPLE)Document29 pagesPreservation Proceedure (SAMPLE)Hasann Maawia100% (1)

- CSS NC II Institutional AssessmentDocument3 pagesCSS NC II Institutional Assessmentdylan tikoyNo ratings yet

- SparkPlug CrossReference Updated 123015 7Document3 pagesSparkPlug CrossReference Updated 123015 7Alex VdbusscheNo ratings yet

- JBW1 - Rev2 PDFDocument1 pageJBW1 - Rev2 PDFSreekanthMylavarapuNo ratings yet

- 089Document1 page089Thiện KhiêmNo ratings yet

- Table 2-2:: Clock InputsDocument1 pageTable 2-2:: Clock InputsThiện KhiêmNo ratings yet

- Spartan-3E FPGA Clock InputsDocument1 pageSpartan-3E FPGA Clock InputsThiện KhiêmNo ratings yet

- Skematik DSNDocument1 pageSkematik DSNAsrul YanuarNo ratings yet

- Raspberry Pi Switchboard SCH - 20171218Document2 pagesRaspberry Pi Switchboard SCH - 20171218julioclavijoNo ratings yet

- PRACTICAL TESTDocument4 pagesPRACTICAL TESTFaris IzzatNo ratings yet

- Jadwal 45 Meni Genap-22.23Document4 pagesJadwal 45 Meni Genap-22.23ANishiNo ratings yet

- Table 3-14:: DCM Clock RequirementsDocument1 pageTable 3-14:: DCM Clock RequirementsThiện KhiêmNo ratings yet

- Input OutputDocument6 pagesInput OutputTanjina K.No ratings yet

- Reset: 20MHZ X1 15pF C1 15pF C2Document1 pageReset: 20MHZ X1 15pF C1 15pF C2Chiton AguirreNo ratings yet

- Extended Spartan-3A Family: Direct Input Connections and Optional External DCM FeedbackDocument1 pageExtended Spartan-3A Family: Direct Input Connections and Optional External DCM FeedbackThiện KhiêmNo ratings yet

- Rack Sampler SystemDocument1 pageRack Sampler Systemnery castroNo ratings yet

- Mfaa-241418-S EsquemaDocument4 pagesMfaa-241418-S EsquemaSergio SilvaNo ratings yet

- Faculty of Electrical and Electronic Engineering 2020 - 2021Document37 pagesFaculty of Electrical and Electronic Engineering 2020 - 2021Thinh LêNo ratings yet

- Gsm-Based Well Water Level MonitorDocument15 pagesGsm-Based Well Water Level Monitorduttachiranjit550No ratings yet

- S10 SW-SPST S11 SW-SPST 12 SW-SPST S13 SW-SPST S14 SW-SPST S15 SW-SPST S16 SW-SPST S17 SW-SPSTDocument1 pageS10 SW-SPST S11 SW-SPST 12 SW-SPST S13 SW-SPST S14 SW-SPST S15 SW-SPST S16 SW-SPST S17 SW-SPSTHieu LeNo ratings yet

- 2011 Japan Student Services OrganizationDocument2 pages2011 Japan Student Services OrganizationJoseNo ratings yet

- Eta 6953 Redmi 9a240330130031Document2 pagesEta 6953 Redmi 9a240330130031kashi kashiNo ratings yet

- Spartan-3 FPGA Clock Inputs: Table 2-3Document1 pageSpartan-3 FPGA Clock Inputs: Table 2-3Thiện KhiêmNo ratings yet

- Pinout Esp32 Devkit v1Document1 pagePinout Esp32 Devkit v1Daniel RibeiroNo ratings yet

- 4 3 3 M H Z Transmitter: R1Out R2Out T1In T2In R1In R2In T1Out T2OutDocument3 pages4 3 3 M H Z Transmitter: R1Out R2Out T1In T2In R1In R2In T1Out T2OutpdhanekulaNo ratings yet

- Mini STM32 STM32F103 TFT LCD Board V3Document1 pageMini STM32 STM32F103 TFT LCD Board V3AndreyNo ratings yet

- PDNDocument7 pagesPDNThomas JosephNo ratings yet

- Turbina ms5001Document64 pagesTurbina ms5001Orlando Jose Serrano0% (1)

- Planing PM Centrale GPEG 2020Document4 pagesPlaning PM Centrale GPEG 2020Salim82 LKNo ratings yet

- LEC2 - 7segment - LED MatrixDocument37 pagesLEC2 - 7segment - LED MatrixYousefNo ratings yet

- Eeg ReviewDocument28 pagesEeg ReviewThanh Bình HoàngNo ratings yet

- Hard BootDocument1 pageHard BootJairo Andrés Quiñones Buitrago100% (2)

- Proteus LEDDocument3 pagesProteus LEDMuhammad Zikri AbdillahNo ratings yet

- Planing PM Centrale GPEG 2021Document4 pagesPlaning PM Centrale GPEG 2021Salim82 LKNo ratings yet

- LCDCharacterDocument1 pageLCDCharacterJIGNESH100% (1)

- Atmega8 LCD TimerDocument1 pageAtmega8 LCD TimerВадим МкртчянNo ratings yet

- lpc1114 SynthDocument1 pagelpc1114 SynthMirel-Cătălin ChirilăNo ratings yet

- Lachoo Memorial College of Science & Technology (Autonomous)Document1 pageLachoo Memorial College of Science & Technology (Autonomous)HghhjNo ratings yet

- Ford Figo b517 2010 25 Ewd10Document1 pageFord Figo b517 2010 25 Ewd10sandeepNo ratings yet

- Adc0808 Pic16f84aDocument1 pageAdc0808 Pic16f84aPhap NguyenNo ratings yet

- Minimum System Atmega8 H-Bridge Motor Driver: Putar Kanan Putar KiriDocument1 pageMinimum System Atmega8 H-Bridge Motor Driver: Putar Kanan Putar KiriJeAmmy BelajarSabarrNo ratings yet

- Pwmprest Rev05 - PWM30070V - ListaDocument1 pagePwmprest Rev05 - PWM30070V - ListaJezus BorgesNo ratings yet

- 3 KW DC-DC Converter Electrical SchematicsDocument5 pages3 KW DC-DC Converter Electrical SchematicsKenneth LazoNo ratings yet

- TC-L47E50L: 47 Inch Class 1080p LCD HDTVDocument5 pagesTC-L47E50L: 47 Inch Class 1080p LCD HDTVсчавит счавитNo ratings yet

- Pelatihan ATMEGA8535 CVAVRDocument121 pagesPelatihan ATMEGA8535 CVAVRnbbudionoNo ratings yet

- MicroCR IDocument102 pagesMicroCR IRoxana ButaNo ratings yet

- Manual Simple Trainer 8051Document6 pagesManual Simple Trainer 8051Sumarwan WawanNo ratings yet

- Ruang Pembagian RaporDocument1 pageRuang Pembagian RaporMirna AsmallahNo ratings yet

- Parts List: TMFX - CDocument64 pagesParts List: TMFX - CNilton RovedaNo ratings yet

- M3329C1/M3329 C1: SpecificationsDocument1 pageM3329C1/M3329 C1: SpecificationsmohamedNo ratings yet

- Assignment 3 SOLUTION1Document5 pagesAssignment 3 SOLUTION1BORU MEDA TUBENo ratings yet

- Jadwal PBM Sem Genap T.P 2022-2023 - Rev - 1Document1 pageJadwal PBM Sem Genap T.P 2022-2023 - Rev - 1Fahri Ahmad SNo ratings yet

- Gambarlah Dengan Menggunakan Proteus Skema Di Bawah Ini:: Pengendali Motor DCDocument4 pagesGambarlah Dengan Menggunakan Proteus Skema Di Bawah Ini:: Pengendali Motor DCLukman AriyantoNo ratings yet

- 747 Dimmer LocationsDocument8 pages747 Dimmer Locations이봉연No ratings yet

- Speeduino 0.4.3D Part ListDocument1 pageSpeeduino 0.4.3D Part ListRicardo LealNo ratings yet

- CHAMPION - TORCH Cross Reference ChartDocument6 pagesCHAMPION - TORCH Cross Reference ChartLawas UnikNo ratings yet

- Skema Asus K45DR Kono KaeDocument5 pagesSkema Asus K45DR Kono KaeAphe TaiasuNo ratings yet

- Dien Tro 330 OmDocument4 pagesDien Tro 330 OmQuang LuậnNo ratings yet

- Schematic - Matrix PCBDocument1 pageSchematic - Matrix PCBvinNo ratings yet

- Implicit and Explicit InformationDocument3 pagesImplicit and Explicit InformationAbbas GholamiNo ratings yet

- Political Culture in Post Communist Countries Albanian CaseDocument10 pagesPolitical Culture in Post Communist Countries Albanian CaseArditÇekaNo ratings yet

- Comparative Study of Isolation Procedures For Essential Oils Hydro Distillation Versus Solvent ExtractionDocument2 pagesComparative Study of Isolation Procedures For Essential Oils Hydro Distillation Versus Solvent ExtractionmyrtaromNo ratings yet

- What I Need To Know? What I Need To Know?: Quarter 1Document16 pagesWhat I Need To Know? What I Need To Know?: Quarter 1Aileen gay PayunanNo ratings yet

- Energy Recovery From Landing AircraftDocument8 pagesEnergy Recovery From Landing AircraftRaniero FalzonNo ratings yet

- Heredity and EvolutionDocument5 pagesHeredity and EvolutionRahul Ecka100% (3)

- AICTE Model - Digital Electronics and Systems - Abhishek Bhatt - 17-01-2024Document539 pagesAICTE Model - Digital Electronics and Systems - Abhishek Bhatt - 17-01-2024matey.tushar5646No ratings yet

- C3Document1 pageC3Maxwell_RhodeszNo ratings yet

- Curriculum Vitae: Pramod - Junior CAM EngineerDocument4 pagesCurriculum Vitae: Pramod - Junior CAM EngineerpramodNo ratings yet

- P PotassiumDocument12 pagesP PotassiumHeleneSmithNo ratings yet

- Starkville Dispatch Eedition 11-4-18Document32 pagesStarkville Dispatch Eedition 11-4-18The DispatchNo ratings yet

- Current Affairs Capsule For SBI/IBPS/RRB PO Mains Exam 2021 - Part 2Document253 pagesCurrent Affairs Capsule For SBI/IBPS/RRB PO Mains Exam 2021 - Part 2King SammyNo ratings yet

- Financial Markets ReviewerDocument8 pagesFinancial Markets ReviewerHalf BloodNo ratings yet

- CHWW What Makes Up A CommunityDocument2 pagesCHWW What Makes Up A CommunityJev DumasisNo ratings yet

- Ageing Aura and Vanitas in Art Greek LauDocument31 pagesAgeing Aura and Vanitas in Art Greek LautaraselbulbaNo ratings yet

- Fluency ReflectionDocument7 pagesFluency Reflectionapi-316375440No ratings yet

- Important People - Exercises 2 PDFDocument2 pagesImportant People - Exercises 2 PDFDiana BerariNo ratings yet

- NFSUDocument14 pagesNFSUROMESHA CHATTERJEENo ratings yet

- G. Vrbová (Auth.), Professor Dr. W. A. Nix, Professor Dr. G. Vrbová (Eds.) - Electrical Stimulation and Neuromuscular Disorders-Springer-Verlag Berlin Heidelberg (1986)Document148 pagesG. Vrbová (Auth.), Professor Dr. W. A. Nix, Professor Dr. G. Vrbová (Eds.) - Electrical Stimulation and Neuromuscular Disorders-Springer-Verlag Berlin Heidelberg (1986)Harshavardhan SNo ratings yet

- E1695-01 CT System Performance MeasurementDocument4 pagesE1695-01 CT System Performance MeasurementsanthakumarNo ratings yet

- Exam Day Flyer 2024Document18 pagesExam Day Flyer 2024chrysostomos tsabounarisNo ratings yet

- Introduction To Supply Chain Analytics: Rohit KapoorDocument13 pagesIntroduction To Supply Chain Analytics: Rohit KapoorSARANSH MOHANTY PGP 2021-23 BatchNo ratings yet

- (Medbook4u Com) IllBaby1Document693 pages(Medbook4u Com) IllBaby1Certificate SurrenderNo ratings yet

- Islam A Challenge To Religion by G. A. ParwezDocument359 pagesIslam A Challenge To Religion by G. A. ParwezJamshed IqbalNo ratings yet

- Design and Fabrication of Unmanned Arial Vehicle For Multi-Mission TasksDocument10 pagesDesign and Fabrication of Unmanned Arial Vehicle For Multi-Mission TasksTJPRC PublicationsNo ratings yet

- PRE - Delivery Inspection OF EX200 Super: /TTC-KGP/SOP/2)Document10 pagesPRE - Delivery Inspection OF EX200 Super: /TTC-KGP/SOP/2)Habibur RahamanNo ratings yet

- L4Tnm-Psa: Product ClassificationDocument4 pagesL4Tnm-Psa: Product Classificationhassan329No ratings yet

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Uploaded by

Thiện KhiêmOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Spartan-3E Fpga: Direct Input and Optional External Feedback To Left-Edge Dcms (Xc3S1200E and Xc3S1600E)

Uploaded by

Thiện KhiêmCopyright:

Available Formats

R

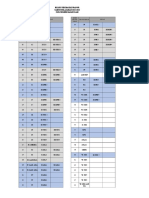

Chapter 3: Using Digital Clock Managers (DCMs)

Table 3-15: Spartan-3E FPGA: Direct Input and Optional External Feedback to Left-Edge DCMs

(XC3S1200E and XC3S1600E)

Diff. Single-Ended Pin Number by Package Type Left Edge

Clock VQ100 CP132 TQ144 PQ208 FT256 FG320 FG400 FG484 LHCLK DCM/BUFGMUX

BUFGMUX_X0Y5 D

BUFGMUX_X0Y4 C

P P9 F3 P14 P22 H5 J5 K3 M5 LHCLK0

Clock Lines

Pair

N P10 F2 P15 P23 H6 J4 K2 L5 LHCLK1

DCM_X0Y2

P P11 F1 P16 P24 H3 J1 K7 L8 LHCLK2

Pair

N P12 G1 P17 P25 H4 J2 L7 M8 LHCLK3

I/O Bank 3

BUFGMUX_X0Y3 B

BUFGMUX_X0Y2 A

BUFGMUX_X0Y9 H

BUFGMUX_X0Y8 G

P P15 G3 P20 P28 J2 K3 M1 M1 LHCLK4

Clock Lines

Pair

N P16 H1 P21 P29 J3 K4 L1 N1 LHCLK5

DCM_X0Y1

P P17 H2 P22 P30 J5 K6 M3 M3 LHCLK6

Pair

N P18 H3 P23 P31 J4 K5 L3 M4 LHCLK7

BUFGMUX_X0Y7 F

BUFGMUX_X0Y6 E

Table 3-16: Spartan-3E FPGA: Direct Input and Optional External Feedback to Right-Edge DCMs

(XC3S1200E and XC3S1600E)

Right Edge Single-Ended Pin Number by Package Type Diff.

DCM/BUFGMUX RHCLK VQ100 CP132 TQ144 PQ208 FT256 FG320 FG400 FG484 Clock

D BUFGMUX_X3Y5

C BUFGMUX_X3Y4

RHCLK7 P68 G13 P94 P135 H11 J14 J20 L19 N

Clock Lines

Pair

RHCLK6 P67 G14 P93 P134 H12 J15 K20 L18 P

DCM_X3Y2

RHCLK5 P66 H12 P92 P133 H14 J16 K14 L21 N

Pair

RHCLK4 P65 H13 P91 P132 H15 J17 K13 L20 P

I/O Bank 1

B BUFGMUX_X3Y3

A BUFGMUX_X3Y2

H BUFGMUX_X3Y9

G BUFGMUX_X3Y8

RHCLK3 P63 J14 P88 P129 J13 K14 L14 M16 N

Clock Lines

Pair

RHCLK2 P62 J13 P87 P128 J14 K15 L15 M15 P

DCM_X3Y1

RHCLK1 P61 J12 P86 P127 J16 K12 L16 M22 N

Pair

RHCLK0 P60 K14 P85 P126 K16 K13 M16 N22 P

F BUFGMUX_X3Y7

E BUFGMUX_X3Y6

86 www.xilinx.com Spartan-3 Generation FPGA User Guide

UG331 (v1.8) June 13, 2011

You might also like

- 787 Circuit Breakers ListDocument144 pages787 Circuit Breakers Listlalo7772100% (3)

- 1NZFE PinoutDocument1 page1NZFE PinoutSet Paing100% (1)

- Annexure A Price Schedule STSDocument188 pagesAnnexure A Price Schedule STSRuslan Ibragimov100% (1)

- Preservation Proceedure (SAMPLE)Document29 pagesPreservation Proceedure (SAMPLE)Hasann Maawia100% (1)

- CSS NC II Institutional AssessmentDocument3 pagesCSS NC II Institutional Assessmentdylan tikoyNo ratings yet

- SparkPlug CrossReference Updated 123015 7Document3 pagesSparkPlug CrossReference Updated 123015 7Alex VdbusscheNo ratings yet

- JBW1 - Rev2 PDFDocument1 pageJBW1 - Rev2 PDFSreekanthMylavarapuNo ratings yet

- 089Document1 page089Thiện KhiêmNo ratings yet

- Table 2-2:: Clock InputsDocument1 pageTable 2-2:: Clock InputsThiện KhiêmNo ratings yet

- Spartan-3E FPGA Clock InputsDocument1 pageSpartan-3E FPGA Clock InputsThiện KhiêmNo ratings yet

- Skematik DSNDocument1 pageSkematik DSNAsrul YanuarNo ratings yet

- Raspberry Pi Switchboard SCH - 20171218Document2 pagesRaspberry Pi Switchboard SCH - 20171218julioclavijoNo ratings yet

- PRACTICAL TESTDocument4 pagesPRACTICAL TESTFaris IzzatNo ratings yet

- Jadwal 45 Meni Genap-22.23Document4 pagesJadwal 45 Meni Genap-22.23ANishiNo ratings yet

- Table 3-14:: DCM Clock RequirementsDocument1 pageTable 3-14:: DCM Clock RequirementsThiện KhiêmNo ratings yet

- Input OutputDocument6 pagesInput OutputTanjina K.No ratings yet

- Reset: 20MHZ X1 15pF C1 15pF C2Document1 pageReset: 20MHZ X1 15pF C1 15pF C2Chiton AguirreNo ratings yet

- Extended Spartan-3A Family: Direct Input Connections and Optional External DCM FeedbackDocument1 pageExtended Spartan-3A Family: Direct Input Connections and Optional External DCM FeedbackThiện KhiêmNo ratings yet

- Rack Sampler SystemDocument1 pageRack Sampler Systemnery castroNo ratings yet

- Mfaa-241418-S EsquemaDocument4 pagesMfaa-241418-S EsquemaSergio SilvaNo ratings yet

- Faculty of Electrical and Electronic Engineering 2020 - 2021Document37 pagesFaculty of Electrical and Electronic Engineering 2020 - 2021Thinh LêNo ratings yet

- Gsm-Based Well Water Level MonitorDocument15 pagesGsm-Based Well Water Level Monitorduttachiranjit550No ratings yet

- S10 SW-SPST S11 SW-SPST 12 SW-SPST S13 SW-SPST S14 SW-SPST S15 SW-SPST S16 SW-SPST S17 SW-SPSTDocument1 pageS10 SW-SPST S11 SW-SPST 12 SW-SPST S13 SW-SPST S14 SW-SPST S15 SW-SPST S16 SW-SPST S17 SW-SPSTHieu LeNo ratings yet

- 2011 Japan Student Services OrganizationDocument2 pages2011 Japan Student Services OrganizationJoseNo ratings yet

- Eta 6953 Redmi 9a240330130031Document2 pagesEta 6953 Redmi 9a240330130031kashi kashiNo ratings yet

- Spartan-3 FPGA Clock Inputs: Table 2-3Document1 pageSpartan-3 FPGA Clock Inputs: Table 2-3Thiện KhiêmNo ratings yet

- Pinout Esp32 Devkit v1Document1 pagePinout Esp32 Devkit v1Daniel RibeiroNo ratings yet

- 4 3 3 M H Z Transmitter: R1Out R2Out T1In T2In R1In R2In T1Out T2OutDocument3 pages4 3 3 M H Z Transmitter: R1Out R2Out T1In T2In R1In R2In T1Out T2OutpdhanekulaNo ratings yet

- Mini STM32 STM32F103 TFT LCD Board V3Document1 pageMini STM32 STM32F103 TFT LCD Board V3AndreyNo ratings yet

- PDNDocument7 pagesPDNThomas JosephNo ratings yet

- Turbina ms5001Document64 pagesTurbina ms5001Orlando Jose Serrano0% (1)

- Planing PM Centrale GPEG 2020Document4 pagesPlaning PM Centrale GPEG 2020Salim82 LKNo ratings yet

- LEC2 - 7segment - LED MatrixDocument37 pagesLEC2 - 7segment - LED MatrixYousefNo ratings yet

- Eeg ReviewDocument28 pagesEeg ReviewThanh Bình HoàngNo ratings yet

- Hard BootDocument1 pageHard BootJairo Andrés Quiñones Buitrago100% (2)

- Proteus LEDDocument3 pagesProteus LEDMuhammad Zikri AbdillahNo ratings yet

- Planing PM Centrale GPEG 2021Document4 pagesPlaning PM Centrale GPEG 2021Salim82 LKNo ratings yet

- LCDCharacterDocument1 pageLCDCharacterJIGNESH100% (1)

- Atmega8 LCD TimerDocument1 pageAtmega8 LCD TimerВадим МкртчянNo ratings yet

- lpc1114 SynthDocument1 pagelpc1114 SynthMirel-Cătălin ChirilăNo ratings yet

- Lachoo Memorial College of Science & Technology (Autonomous)Document1 pageLachoo Memorial College of Science & Technology (Autonomous)HghhjNo ratings yet

- Ford Figo b517 2010 25 Ewd10Document1 pageFord Figo b517 2010 25 Ewd10sandeepNo ratings yet

- Adc0808 Pic16f84aDocument1 pageAdc0808 Pic16f84aPhap NguyenNo ratings yet

- Minimum System Atmega8 H-Bridge Motor Driver: Putar Kanan Putar KiriDocument1 pageMinimum System Atmega8 H-Bridge Motor Driver: Putar Kanan Putar KiriJeAmmy BelajarSabarrNo ratings yet

- Pwmprest Rev05 - PWM30070V - ListaDocument1 pagePwmprest Rev05 - PWM30070V - ListaJezus BorgesNo ratings yet

- 3 KW DC-DC Converter Electrical SchematicsDocument5 pages3 KW DC-DC Converter Electrical SchematicsKenneth LazoNo ratings yet

- TC-L47E50L: 47 Inch Class 1080p LCD HDTVDocument5 pagesTC-L47E50L: 47 Inch Class 1080p LCD HDTVсчавит счавитNo ratings yet

- Pelatihan ATMEGA8535 CVAVRDocument121 pagesPelatihan ATMEGA8535 CVAVRnbbudionoNo ratings yet

- MicroCR IDocument102 pagesMicroCR IRoxana ButaNo ratings yet

- Manual Simple Trainer 8051Document6 pagesManual Simple Trainer 8051Sumarwan WawanNo ratings yet

- Ruang Pembagian RaporDocument1 pageRuang Pembagian RaporMirna AsmallahNo ratings yet

- Parts List: TMFX - CDocument64 pagesParts List: TMFX - CNilton RovedaNo ratings yet

- M3329C1/M3329 C1: SpecificationsDocument1 pageM3329C1/M3329 C1: SpecificationsmohamedNo ratings yet

- Assignment 3 SOLUTION1Document5 pagesAssignment 3 SOLUTION1BORU MEDA TUBENo ratings yet

- Jadwal PBM Sem Genap T.P 2022-2023 - Rev - 1Document1 pageJadwal PBM Sem Genap T.P 2022-2023 - Rev - 1Fahri Ahmad SNo ratings yet

- Gambarlah Dengan Menggunakan Proteus Skema Di Bawah Ini:: Pengendali Motor DCDocument4 pagesGambarlah Dengan Menggunakan Proteus Skema Di Bawah Ini:: Pengendali Motor DCLukman AriyantoNo ratings yet

- 747 Dimmer LocationsDocument8 pages747 Dimmer Locations이봉연No ratings yet

- Speeduino 0.4.3D Part ListDocument1 pageSpeeduino 0.4.3D Part ListRicardo LealNo ratings yet

- CHAMPION - TORCH Cross Reference ChartDocument6 pagesCHAMPION - TORCH Cross Reference ChartLawas UnikNo ratings yet

- Skema Asus K45DR Kono KaeDocument5 pagesSkema Asus K45DR Kono KaeAphe TaiasuNo ratings yet

- Dien Tro 330 OmDocument4 pagesDien Tro 330 OmQuang LuậnNo ratings yet

- Schematic - Matrix PCBDocument1 pageSchematic - Matrix PCBvinNo ratings yet

- Implicit and Explicit InformationDocument3 pagesImplicit and Explicit InformationAbbas GholamiNo ratings yet

- Political Culture in Post Communist Countries Albanian CaseDocument10 pagesPolitical Culture in Post Communist Countries Albanian CaseArditÇekaNo ratings yet

- Comparative Study of Isolation Procedures For Essential Oils Hydro Distillation Versus Solvent ExtractionDocument2 pagesComparative Study of Isolation Procedures For Essential Oils Hydro Distillation Versus Solvent ExtractionmyrtaromNo ratings yet

- What I Need To Know? What I Need To Know?: Quarter 1Document16 pagesWhat I Need To Know? What I Need To Know?: Quarter 1Aileen gay PayunanNo ratings yet

- Energy Recovery From Landing AircraftDocument8 pagesEnergy Recovery From Landing AircraftRaniero FalzonNo ratings yet

- Heredity and EvolutionDocument5 pagesHeredity and EvolutionRahul Ecka100% (3)

- AICTE Model - Digital Electronics and Systems - Abhishek Bhatt - 17-01-2024Document539 pagesAICTE Model - Digital Electronics and Systems - Abhishek Bhatt - 17-01-2024matey.tushar5646No ratings yet

- C3Document1 pageC3Maxwell_RhodeszNo ratings yet

- Curriculum Vitae: Pramod - Junior CAM EngineerDocument4 pagesCurriculum Vitae: Pramod - Junior CAM EngineerpramodNo ratings yet

- P PotassiumDocument12 pagesP PotassiumHeleneSmithNo ratings yet

- Starkville Dispatch Eedition 11-4-18Document32 pagesStarkville Dispatch Eedition 11-4-18The DispatchNo ratings yet

- Current Affairs Capsule For SBI/IBPS/RRB PO Mains Exam 2021 - Part 2Document253 pagesCurrent Affairs Capsule For SBI/IBPS/RRB PO Mains Exam 2021 - Part 2King SammyNo ratings yet

- Financial Markets ReviewerDocument8 pagesFinancial Markets ReviewerHalf BloodNo ratings yet

- CHWW What Makes Up A CommunityDocument2 pagesCHWW What Makes Up A CommunityJev DumasisNo ratings yet

- Ageing Aura and Vanitas in Art Greek LauDocument31 pagesAgeing Aura and Vanitas in Art Greek LautaraselbulbaNo ratings yet

- Fluency ReflectionDocument7 pagesFluency Reflectionapi-316375440No ratings yet

- Important People - Exercises 2 PDFDocument2 pagesImportant People - Exercises 2 PDFDiana BerariNo ratings yet

- NFSUDocument14 pagesNFSUROMESHA CHATTERJEENo ratings yet

- G. Vrbová (Auth.), Professor Dr. W. A. Nix, Professor Dr. G. Vrbová (Eds.) - Electrical Stimulation and Neuromuscular Disorders-Springer-Verlag Berlin Heidelberg (1986)Document148 pagesG. Vrbová (Auth.), Professor Dr. W. A. Nix, Professor Dr. G. Vrbová (Eds.) - Electrical Stimulation and Neuromuscular Disorders-Springer-Verlag Berlin Heidelberg (1986)Harshavardhan SNo ratings yet

- E1695-01 CT System Performance MeasurementDocument4 pagesE1695-01 CT System Performance MeasurementsanthakumarNo ratings yet

- Exam Day Flyer 2024Document18 pagesExam Day Flyer 2024chrysostomos tsabounarisNo ratings yet

- Introduction To Supply Chain Analytics: Rohit KapoorDocument13 pagesIntroduction To Supply Chain Analytics: Rohit KapoorSARANSH MOHANTY PGP 2021-23 BatchNo ratings yet

- (Medbook4u Com) IllBaby1Document693 pages(Medbook4u Com) IllBaby1Certificate SurrenderNo ratings yet

- Islam A Challenge To Religion by G. A. ParwezDocument359 pagesIslam A Challenge To Religion by G. A. ParwezJamshed IqbalNo ratings yet

- Design and Fabrication of Unmanned Arial Vehicle For Multi-Mission TasksDocument10 pagesDesign and Fabrication of Unmanned Arial Vehicle For Multi-Mission TasksTJPRC PublicationsNo ratings yet

- PRE - Delivery Inspection OF EX200 Super: /TTC-KGP/SOP/2)Document10 pagesPRE - Delivery Inspection OF EX200 Super: /TTC-KGP/SOP/2)Habibur RahamanNo ratings yet

- L4Tnm-Psa: Product ClassificationDocument4 pagesL4Tnm-Psa: Product Classificationhassan329No ratings yet