Professional Documents

Culture Documents

Az5a75 01F

Az5a75 01F

Uploaded by

ttOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Az5a75 01F

Az5a75 01F

Uploaded by

ttCopyright:

Available Formats

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

Features AZ5A75-01F is a unique design which includes

proprietary clamping cell in a single package.

ESD protection for one line with bi-directional During transient conditions, the proprietary

Provide transient protection for one line to clamping cell prevents over-voltage on the power

IEC 61000-4-2 (ESD) ±17kV (air), ±15kV (contact) line or control/data lines, protecting any

IEC 61000-4-4 (EFT) 40A (5/50ns) downstream components.

Cable Discharge Event (CDE)

0201 small DFN package saves board space AZ5A75-01F may be used to meet the ESD

Protect one I/O line or one power line immunity requirements of IEC 61000-4-2, Level 4

Fast turn-on and low clamping voltage (±15kV air, ±8kV contact discharge)

For low operating voltage applications: 5V

maximum

Solid-state silicon-avalanche and active circuit

triggering technology Circuit Diagram /

Green part Pin Configuration

Applications

Mobile phones

Handheld portable applications 1

Computer interfaces protection

Microprocessors protection

Serial and parallel ports protection

Control signal lines protection

Power lines on PCB protection

Latch-up protection 2

Description

DFN0603P2Y (Bottom View)

AZ5A75-01F is a design which includes one (0.6mm x 0.3mm x 0.3mm)

bi-directional ESD rated clamping cell to protect

one power line, or one control line, or one

low-speed data line in an electronic system. The

AZ5A75-01F has been specifically designed to

protect sensitive components which are

connected to power and control lines from

over-voltage damage and latch-up caused by

Electrostatic Discharging (ESD), Electrical Fast

Transients (EFT), and Cable Discharge Event

(CDE).

Revision 2018/03/19 ©2018 Amazing Micro. 1 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

SPECIFICATIONS

ABSOLUTE MAXIMUM RATINGS (TA= 25oC, unless otherwise specified)

PARAMETER SYMBOL RATING UNIT

Operating Supply Voltage VDC ±5.5 V

ESD per IEC 61000-4-2 (Air) VESD-1 ±17

kV

ESD per IEC 61000-4-2 (Contact) VESD-2 ±15

o

Lead Soldering Temperature TSOL 260 (10 sec.) C

o

Operating Temperature TOP -55 to +85 C

o

Storage Temperature TSTO -55 to +150 C

ELECTRICAL CHARACTERISTICS

PARAMETER SYMBOL CONDITION MIN TYP MAX UNIT

Reverse Stand-Off

VRWM T=25 oC. -5 5 V

Voltage

Reverse Leakage

ILeak VRWM = ±5V, T=25 oC. 100 nA

Current

Reverse Breakdown

VBV IBV = 1mA, T=25 oC. 5.6 9 V

Voltage

ESD Clamping IEC 61000-4-2 +8kV (ITLP = 16A),

VCL-ESD 12 V

Voltage (Note 1) Contact mode, T=25 oC.

ESD Dynamic IEC 61000-4-2, 0~+8kV, T=25 oC,

Rdynamic 0.25 Ω

Turn-on Resistance Contact mode.

Channel Input

CIN VR = 0V, f = 1MHz, T=25 oC. 5.5 7 pF

Capacitance

Note 1: ESD Clamping Voltage was measured by Transmission Line Pulsing (TLP) System.

TLP conditions: Z0= 50Ω, tp= 100ns, tr= 1ns.

Revision 2018/03/19 ©2018 Amazing Micro. 2 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

Typical Characteristics

Typical Variation of CIN vs. VIN

8

7 Pin 1 to Pin 2

2

f = 1MHz, T = 25℃

Input Capacitance (pF)

0

-5 -4 -3 -2 -1 0 1 2 3 4 5

Input Voltage (V)

Transmission Line Pulsing (TLP) Measurement

18

V_pulse

16

14 Pulse from a

transmission line TLP_I

12 100ns +

10

TLP_V DUT

8

6 _

4

2

0

-2

-4

-6

-8

-10

-12

-14 Pin1 to Pin2

-16

-18

-14 -12 -10 -8 -6 -4 -2 0 2 4 6 8 10 12

Transmission Line Pulsing (T

Transmission Line Pulsing (TLP) Voltage (V)

Revision 2018/03/19 ©2018 Amazing Micro. 3 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

Application Information

The AZ5A75-01F is designed to protect one line In order to obtain enough suppression of ESD

against system ESD/EFT/Cable Discharge induced transient, a good circuit board is critical.

pulses by clamping it to an acceptable reference. Thus, the following guidelines are recommended:

It provides bi-directional protection. Minimize the path length between the

protected lines and the AZ5A75-01F.

The usage of the AZ5A75-01F is shown in Fig. 1. Place the AZ5A75-01F near the input

Protected line, such as data line, control line, or terminals or connectors to restrict transient

power line, is connected at pin 1. The pin 2 is coupling.

connected to a ground plane on the board. In The ESD current return path to ground

order to minimize parasitic inductance in the should be kept as short as possible.

board traces, all path lengths connected to the Use ground planes whenever possible.

pins of AZ5A75-01F should be kept as short as NEVER route critical signals near board

possible. edges and near the lines which the ESD

transient easily injects to.

AZ5A75-01F

AZ5A75-01F

Fig. 1

Revision 2018/03/19 ©2018 Amazing Micro. 4 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

Fig. 2 shows another simplified example of using low-speed data line, and power line from ESD

AZ5A75-01F to protect the control line, transient stress.

AZ5A75-01F

AZ5A75-01F

AZ5A75-01F

Fig. 2

Revision 2018/03/19 ©2018 Amazing Micro. 5 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

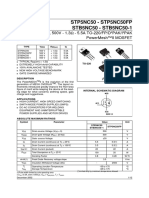

Mechanical Details LAND LAYOUT

0.15

DFN0603P2Y 0.25 0.25

PACKAGE DIAGRAMS

D

0.30

E

0.65

(Unit: mm)

TOP VIEW

Notes:

This LAND LAYOUT is for reference

purposes only. Please consult your

A

manufacturing partners to ensure your

A1 company’s PCB design guidelines are met.

SIDE VIEW

D1 D2

45o MARKING CODE

0.05

0.05

E1 E2

F

BOTTOM VIEW

K = Device Code

Millimeters

SYMBOL

MIN. NOM. MAX.

Part Number Marking Code

D 0.55 0.60 0.65

E 0.25 0.30 0.35

AZ5A75-01F.R7G

A 0.28 0.30 0.32 K

(Green Part)

A1 0.00 0.02 0.05

D1 0.13 0.18 0.23 Note. Green means Pb-free, RoHS, and

D2 0.14 0.19 0.24 Halogen free compliant.

E1/E2 0.20 0.25 0.30

F 0.35

Revision 2018/03/19 ©2018 Amazing Micro. 6 www.amazingIC.com

AZ5A75-01F

Transient Voltage Suppressing Device

Tiny Package for ESD/Transient Protection

Ordering Information

PN# Material Type Reel size MOQ MOQ/internal box MOQ/carton

AZ5A75-01F.R7G Green T/R 7 inch 12,000/reel 4 reels= 48,000/box 6 boxes =288,000/carton

Revision History

Revision Modification Description

Revision 2017/03/24 Preliminary Release.

Revision 2018/03/19 Formal Release.

Revision 2018/03/19 ©2018 Amazing Micro. 7 www.amazingIC.com

You might also like

- Iec 60364-4-41Document7 pagesIec 60364-4-41harish50% (2)

- IEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 15kV (Contact) IEC 61000-4-4 (EFT) 50A (5/50ns) Cable Discharge Event (CDE)Ion PetruscaNo ratings yet

- IEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)Document6 pagesIEC 61000-4-2 (ESD) 20kV (Air), 12kV (Contact) IEC 61000-4-4 (EFT) 40A (5/50ns) IEC 61000-4-5 (Lightning) 7A (8/20 S) Cable Discharge Event (CDE)cafosokNo ratings yet

- Az5b75 01BDocument6 pagesAz5b75 01BttNo ratings yet

- AZ5413-01F.R7GR DatasheetDocument7 pagesAZ5413-01F.R7GR DatasheetttNo ratings yet

- AZ3105-01F DatasheetDocument5 pagesAZ3105-01F DatasheetttNo ratings yet

- 1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge ProtectionDocument7 pages1.6mm X 1.0mm DFN Package Saves Board: Transient Voltage Suppressing Device For ESD and Surge ProtectionxXMythicalRoseXNo ratings yet

- 0402 Small DFN Package Saves Board SpaceDocument7 pages0402 Small DFN Package Saves Board Spacecarlos rumboNo ratings yet

- AZ3133-04F DatasheetDocument7 pagesAZ3133-04F DatasheetttNo ratings yet

- AZ2115-05C.R7G (Datasheet)Document7 pagesAZ2115-05C.R7G (Datasheet)ttNo ratings yet

- ESD Protection AZC099-04S PDFDocument12 pagesESD Protection AZC099-04S PDFChrist TianNo ratings yet

- Ultra Low Capacitance: 0.4pF Typical: Suitable For, 17V and Below, Operating Voltage ApplicationsDocument7 pagesUltra Low Capacitance: 0.4pF Typical: Suitable For, 17V and Below, Operating Voltage ApplicationsttNo ratings yet

- Az5b0s 01FDocument6 pagesAz5b0s 01FJC CNo ratings yet

- Azc199 02SDocument8 pagesAzc199 02SHamzaNo ratings yet

- SYT06S03DVCDocument9 pagesSYT06S03DVCttNo ratings yet

- For Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalDocument10 pagesFor Operating Voltage of 5V and Below Ultra Low Capacitance: 0.5pF TypicalTri Nguyen Real EstateNo ratings yet

- For Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalDocument9 pagesFor Operating Voltage of 3.3V and Below Ultra Low Capacitance: 0.45pF TypicalChithiran C SspNo ratings yet

- SLP1210N6Document7 pagesSLP1210N6NalsonNo ratings yet

- TVL ST23 04 Ad0Document9 pagesTVL ST23 04 Ad0coulsonpfilNo ratings yet

- Low Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesDocument8 pagesLow Capacitance TVS For LVDS Interfaces: Protection Products - Railclamp Description FeaturesAnibal Tantalean SarmientoNo ratings yet

- RCLAMP0503NDocument7 pagesRCLAMP0503NAisya NurcahyaNo ratings yet

- Low Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesDocument6 pagesLow Voltage Clamp For ESD and CDE Protection: Protection Products Protection Products - Microclamp Description FeaturesAmirNo ratings yet

- INPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Document8 pagesINPAQ Transient Voltage Suppressor TVLST2304BD0 Specification A0Isaac CostaNo ratings yet

- SR05 N2195 Rev.aDocument5 pagesSR05 N2195 Rev.aMauricio T CostaNo ratings yet

- CDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsDocument6 pagesCDDFN10-2574N - Surface Mount TVS Diode Array: Features ApplicationsAlexNo ratings yet

- Datasheet 0524P Dioda TVS ArrayDocument4 pagesDatasheet 0524P Dioda TVS ArraynoorsyaifulNo ratings yet

- Slvu2 8Document10 pagesSlvu2 8hadiNo ratings yet

- ESDSRVLC05-4: DescriptionDocument5 pagesESDSRVLC05-4: DescriptionelminerocapmaNo ratings yet

- ESD5302N WillSEMIDocument7 pagesESD5302N WillSEMIRenato Luiz TécnicoNo ratings yet

- SMCJ 778393Document7 pagesSMCJ 778393aprioris84No ratings yet

- Data SheetDocument10 pagesData SheetRaphael Silveira de SouzaNo ratings yet

- WILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFDocument5 pagesWILLSEMI Will Semicon ESD5311N 2 TR - C153721 PDFPippoNo ratings yet

- GT I9300 Galaxy S3 U713 PDFDocument10 pagesGT I9300 Galaxy S3 U713 PDFhernanNo ratings yet

- Railclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesDocument8 pagesRailclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesHemantkumarNo ratings yet

- LM341/LM78MXX Series 3-Terminal Positive Voltage Regulators: Features DescriptionDocument18 pagesLM341/LM78MXX Series 3-Terminal Positive Voltage Regulators: Features Descriptiondasch7788No ratings yet

- Esda 25 B 1Document5 pagesEsda 25 B 1aleregsilva7321No ratings yet

- Railclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesDocument10 pagesRailclamp Low Capacitance Tvs Array: Protection Products - Railclamp Description FeaturesEinson SepulvedaNo ratings yet

- TLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power SupplyDocument10 pagesTLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power Supplycarlosjuniors888No ratings yet

- PTVS5V5D1BLDocument12 pagesPTVS5V5D1BLttNo ratings yet

- BSP75N Transistor Inhibodor ArranqueDocument8 pagesBSP75N Transistor Inhibodor ArranqueCerrajería SecurityNo ratings yet

- Railclamp Low Capacitance Tvs Diode Array: Protection Products Description FeaturesDocument13 pagesRailclamp Low Capacitance Tvs Diode Array: Protection Products Description Featuresrishi sagarNo ratings yet

- Aoz8s502bds 05Document5 pagesAoz8s502bds 05ttNo ratings yet

- Ka78Mxx: 3-Terminal 0.5A Positive Voltage RegulatorDocument14 pagesKa78Mxx: 3-Terminal 0.5A Positive Voltage RegulatorTinwin HtutNo ratings yet

- Esd9B, Szesd9B Transient Voltage Suppressors: Micro Packaged Diodes For ESD ProtectionDocument4 pagesEsd9B, Szesd9B Transient Voltage Suppressors: Micro Packaged Diodes For ESD ProtectionВиктор АгарковNo ratings yet

- TLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power SupplyDocument9 pagesTLP731, TLP732: Office Machine Household Use Equipment Solid State Relay Switching Power SupplysNo ratings yet

- Tesdc24V: Taiwan SemiconductorDocument6 pagesTesdc24V: Taiwan Semiconductorn tanevarNo ratings yet

- RClamp1011ZCTNT TFTDocument11 pagesRClamp1011ZCTNT TFTttNo ratings yet

- Chipguard MLC Series - Esd Protectors: Features ApplicationsDocument4 pagesChipguard MLC Series - Esd Protectors: Features ApplicationsPhan Ngọc DuyNo ratings yet

- Datasheet TN6Q04 PDFDocument4 pagesDatasheet TN6Q04 PDFDaniel AvecillaNo ratings yet

- Esdalc6v1 1u2Document11 pagesEsdalc6v1 1u2Aditya SrivatsavNo ratings yet

- uClamp2411ZA AGDocument6 pagesuClamp2411ZA AGttNo ratings yet

- ESDA25DB3: Transil Array For Esd ProtectionDocument5 pagesESDA25DB3: Transil Array For Esd ProtectionZoltán ÁgostonNo ratings yet

- MC78M12Document14 pagesMC78M12Radio AtelierNo ratings yet

- WILLSEMI Will Semicon ESD5451N 2 TR - C239604Document7 pagesWILLSEMI Will Semicon ESD5451N 2 TR - C239604PippoNo ratings yet

- Stps 5 L 25Document8 pagesStps 5 L 25Gabriel LatiuNo ratings yet

- Stp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetDocument12 pagesStp5Nc50 - Stp5Nc50Fp Stb5Nc50 - Stb5Nc50-1: N-Channel 500V - 1.3 - 5.5A To-220/Fp/D Pak/I Pak Powermesh Ii MosfetJavier55No ratings yet

- DatasheetDocument12 pagesDatasheetErwin Rolando EscobarNo ratings yet

- ESDA25B1: Transil Array For Esd ProtectionDocument5 pagesESDA25B1: Transil Array For Esd Protectiondrain rainNo ratings yet

- Stps 5 H 100Document10 pagesStps 5 H 100chudungk57No ratings yet

- TLP531, TLP532Document9 pagesTLP531, TLP532leon silvaNo ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- SMD Type High Current Molding Power ChokeDocument90 pagesSMD Type High Current Molding Power ChokettNo ratings yet

- IPC Simple Standards Tree 2024Document1 pageIPC Simple Standards Tree 2024ttNo ratings yet

- IPC-4554-2005 浸没镀锡印刷电路板规范Document18 pagesIPC-4554-2005 浸没镀锡印刷电路板规范ttNo ratings yet

- SCT12A2Document23 pagesSCT12A2ttNo ratings yet

- HLCA0420SD-Series 20220704Document6 pagesHLCA0420SD-Series 20220704ttNo ratings yet

- AZ5413-01F.R7GR DatasheetDocument7 pagesAZ5413-01F.R7GR DatasheetttNo ratings yet

- HLCA0530SD Series - A03 2020.11.12Document6 pagesHLCA0530SD Series - A03 2020.11.12ttNo ratings yet

- Rca N5045a Series 28Q200 29Document9 pagesRca N5045a Series 28Q200 29ttNo ratings yet

- En Iso 15197 2015Document60 pagesEn Iso 15197 2015ttNo ratings yet

- Technician Mechatronics - CTS2.0 - NSQF-4Document73 pagesTechnician Mechatronics - CTS2.0 - NSQF-4projectsNo ratings yet

- Sefelec Reference Pent0438: Operating Manual XS SERIES - EnglishDocument156 pagesSefelec Reference Pent0438: Operating Manual XS SERIES - EnglishFidaa JaafrahNo ratings yet

- KSKDocument197 pagesKSKAnonymous qIGu372No ratings yet

- A31315 DatasheetDocument70 pagesA31315 DatasheetblejekmcNo ratings yet

- Advance Harmonic FilterDocument4 pagesAdvance Harmonic FilterMichael SetiawanNo ratings yet

- Dr. Assad Abu-Jasser, ECE-iugaza: Electrical Machines (EELE 4350)Document37 pagesDr. Assad Abu-Jasser, ECE-iugaza: Electrical Machines (EELE 4350)muaz_aminu1422No ratings yet

- Panasonic Nv-gs10, Nv-gs30, Nv-gs40, Nv-gs50 SchematicsDocument90 pagesPanasonic Nv-gs10, Nv-gs30, Nv-gs40, Nv-gs50 SchematicsEpureanu VasileNo ratings yet

- Physics 2102 Gabriela GonzálezDocument10 pagesPhysics 2102 Gabriela Gonzálezjeez janiNo ratings yet

- 9 271Document11 pages9 271Алексей ЯмаNo ratings yet

- SSDG Grid Code - Rev Sept 2019Document33 pagesSSDG Grid Code - Rev Sept 2019Ashfaaq OchatoyaNo ratings yet

- Safick Ahammed. M Mobile: +971-552685851 Career Objective: Fountain View (Emaar) - Downtown - DubaiDocument5 pagesSafick Ahammed. M Mobile: +971-552685851 Career Objective: Fountain View (Emaar) - Downtown - Dubaimohamed shariefNo ratings yet

- ICT Grade 6 UAEDocument29 pagesICT Grade 6 UAEfalasteen.qandeelNo ratings yet

- Convergence of Emerging Technologies To Address The Challenges of The 21 CenturyDocument26 pagesConvergence of Emerging Technologies To Address The Challenges of The 21 CenturyMara DulogNo ratings yet

- Viewsonic Va1912w Service ManualDocument66 pagesViewsonic Va1912w Service Manualradioman_350% (1)

- Mems Microphone ThesisDocument8 pagesMems Microphone Thesisdnr8hw9w100% (1)

- @high Frequency Properties of Electro-Textiles For Wearable Antenna ApplicationsDocument9 pages@high Frequency Properties of Electro-Textiles For Wearable Antenna ApplicationsMomtaz Islam SobujNo ratings yet

- GK3000 Single Phase VFD Manual PDFDocument52 pagesGK3000 Single Phase VFD Manual PDFKaren CruzNo ratings yet

- BOD Incubator-User ManualDocument4 pagesBOD Incubator-User ManualTech LabNo ratings yet

- V11100 16V O - V S: VER Oltage EnsorDocument4 pagesV11100 16V O - V S: VER Oltage EnsorBelinda Koyaiye100% (1)

- Performance Analysis of Different Bit Carry Look Ahead Adder Using VHDL EnvironmentDocument9 pagesPerformance Analysis of Different Bit Carry Look Ahead Adder Using VHDL Environmentssabinayaa12No ratings yet

- Masoneilan SVI II AP Digital Valve Positioner - Brochure - English PDFDocument16 pagesMasoneilan SVI II AP Digital Valve Positioner - Brochure - English PDFHenry ZhangNo ratings yet

- CH340DS1Document15 pagesCH340DS1Biswajit GhoshNo ratings yet

- Design and Simulation of Grid Connected PV System With Hybrid Inverter Using MATLAB/SimulinkDocument7 pagesDesign and Simulation of Grid Connected PV System With Hybrid Inverter Using MATLAB/SimulinkFawkes SangNo ratings yet

- Bera-: Sr. No Name of Equipment Specification Justific AtionDocument5 pagesBera-: Sr. No Name of Equipment Specification Justific AtionNandini GuptaNo ratings yet

- Design An Electrical Power Grid Substation 66Document5 pagesDesign An Electrical Power Grid Substation 66Mostafa El SheikhNo ratings yet

- Method Statement For Instrument Calibration PDFDocument14 pagesMethod Statement For Instrument Calibration PDFMohamed AdelNo ratings yet

- Leroy Somer Main AlternatorsDocument20 pagesLeroy Somer Main AlternatorsShahzad HussainNo ratings yet

- Design Domain and Levels of AbstractionDocument68 pagesDesign Domain and Levels of Abstractionsirisha1983No ratings yet

- DIN Rail Mounted Programmable Digital Timer Switch Instruction ManualDocument3 pagesDIN Rail Mounted Programmable Digital Timer Switch Instruction ManualRoberto VillegasNo ratings yet