Professional Documents

Culture Documents

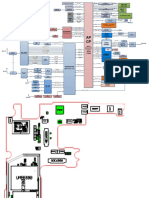

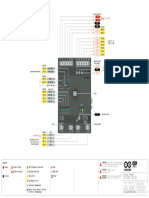

T3 7page V1.0

T3 7page V1.0

Uploaded by

Wolf JohnOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

T3 7page V1.0

T3 7page V1.0

Uploaded by

Wolf JohnCopyright:

Available Formats

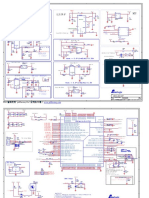

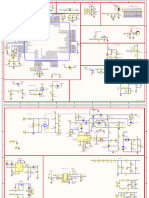

SYS of HI3519AV100 1V8_SOC

1V8_SOC NOTES:(very important!!!)

1L3 1P6

If the customer does not use the UPDATE_MODE_N function, the customer can use

AVDD_BAT_RTC 1P4 DVDD18_PMC

AVDD_BAT_RTC

AVDD18_EMMC

only the GPIO output function or SPI function of the pin. The hardware design must

AC2

C433 33PF RTC_XIN 1P5 AVSS_RTC1

AVSS_RTC2 NF_DQ0/EMMC_DATA7/PWM_OUT5

AT8 ensure that the pin has an external pull-up resistor and the recommended

C0402

RTC_XIN AD2

U3D GPIO5_7

NF_DQ1/EMMC_DATA2/PWM_OUT4

AT7 impedance is 4.7k

RTC_XOUT RTC_XIN GPIO5_2

X2 AD1 AU7

RTC_XOUT NF_DQ2/EMMC_DATA1/PWM_OUT3

TP33 1

1 VDD_TEST_RTC 1N4

VDD_TEST_RTC <DEVICE> GPIO5_1 AT6

If the customer does not use any function of this pin,

41

2 3 NF_DQ3/EMMC_DATA0/PWM_OUT2

TP-C40

32.768KHZ

1K1

Y1 PWR_STARTUP

GPIO5_0

NF_DQ4/EMMC_DATA4/SFC_MISO_IO1

AT5 SFC_MISO_IO1 the hardware hardware design must ensure that the pin

1K2 PWR_SEQ0 GPIO5_4 AU5 SFC_MOSI_IO0

XTAL4-6_7X1_4-H1_4

PWR_SEQ1 NF_DQ5/EMMC_DATA3/SFC_MOSI_IO0

1L2

AB2 PWR_SEQ2 GPIO5_5 AT4 SFC_HOLD_IO3

has an external pull-up resistor.

AA2 PWR_WAKEUP0 NF_DQ6/EMMC_DATA5/SFC_HOLD_IO3

C432 33PF RTC_XOUT Y2 PWR_WAKEUP1

PWR_BUTTON0

GPIO5_3

NF_DQ7/EMMC_DATA6/SFC_WP_IO2

AT3 SFC_WP_IO2 The recommended resistance is 4.7k

PWR功能NC时,PWR_RSTN必须接4.7UF的电容 AB1

SYS Interface 4 of 7

1L1 PWR_EN0 GPIO5_6 AT2

C0402

PWR_RSTN 1M1 PWR_EN1 NF_RDY/EMMC_DS AU3 SFC_CLK/NF_REN

R505 10

PWR_RSTN NF_REN/EMMC_CLK/SFC_CLK 1V2

XIN 1V8_SOC NF_CLE/SFC_CSN1/GPIO6_3 1V3 SFC_CSN0/NF_WEN

C355 18PF R92 R0402 0

NF_WEN/EMMC_RST_N/SFC_CSN0

GPIO6_1 1W1

C0402 R0402

NF_ALE/EMMC_POWER_EN/PWM_OUT7

R84

X5 1L4

AVDD18_LSADC GPIO6_2

1

1K4 1W2

AVSS_LSADC NF_CSN/EMMC_CMD/PWM_OUT6

1

GPIO6_0

2 4 1W3

R177 200

GND1 GND2 VCC_12V_ADC 1N1 EMMC_ZCOMP

1M

LSADC_CH0/GPIO1_0 1V8_SOC

3

1P1 R0402

R0402 1M2 LSADC_CH1/GPIO1_1

3

1N2 LSADC_CH2/GPIO1_2

24MHZ LSADC_CH3/GPIO1_3

1V8_SOC

R113

XTAL4-3_2X2_5-P1_2X1_4-H0_9

C356 18PF R32 100 XOUT

Note:EMMC_ZCOMP resistor(R177/200ohm) must be retained

C0402 R0402 1M4

DVDD18_OSC

10K

1P3 RESET_USB

JTAG_EN 1P2 PWR_EN_12V_DVR

XIN AF1 JTAG_TRSTN/I2S0_MCLK/I2S1_MCLK R0402

XOUT AF2 XIN UART7_RXD/GPIO2_0 AH1

XOUT JTAG_TCK/I2S1_BCLK/UART7_TXD PWR_RSTN

GPIO2_1

AH2 PWR_OFF_DONE _CPU

JTAG_TMS/I2S1_WS/UART7_RTSN

C23

GPIO2_2 1R3

PWM_OUT0_1V2 AN2 JTAG_TDO/I2S1_SD_RX0

PWM_OUT1_1V8 AR2 PWM_OUT0/GPIO1_6 UART7_CTSN/GPIO2_3 1R2 3V3_PER

SVB_PWM0_DVDD 1T3 PWM_OUT1/GPIO1_7 JTAG_TDI/I2S0_BCLK/I2S1_SD_RX1

SVB_PWM0/SPI4_SCLK/I2C9_SCL UART8_RXD/GPIO2_4

4.7UF

AM2

GPIO4_0 GPIO2_5/I2S0_WS/UART8_TXD

1T2

SVB_PWM1/SPI4_SDO/I2C9_SDA I2S1_SD_RX2

R193

R192

AM1

SVB_PWM2_CPU_MEDIA GPIO4_1 GPIO2_6/I2S0_SD_TX/UART8_RTSN C0402

1U2 TEST_MODE FUNCTION

UPDATE_MODE_N 1V1 SVB_PWM2/SPI4_SDI/GPIO4_2 I2S1_SD_RX3 1U1

GPIO4_3/SPI4_CSN/UPDATE_MODE_N GPIO2_7/IR_IN/I2S0_SD_RX 0 normal mode NOTES:The reset time of PWR_RSTN must be more than 40us.

NOTES:(very important!!!)

when use RTC function and Coin battery,pay attention to the circuit. UART8_CTSN/I2S0_MCLK Reset time is about 1ms

you must use two same Schottky diode. 1 test mode

4.7K

1K

1K

the forward voltage of Schottky diode VF<0.3V. POR_SEL 1T1 1R1 TEST_MODE

R163

POR_SEL TEST_MODE

3V3_SOC R0402

R0402

SYS_RSTN_1V8 AK1 R0402

AVDD_BAT_RTC RST_N AP1 I2C0_SDA

SD3 AL2 I2C0_SDA AP2 I2C0_SCL

SYS_RSTN_OUT/WDG_RSTN I2C0_SCL I2C0_SCL

1K R71 A C B_RTC

HBGA567-16-3737

R0402 SOD523 Note:I2C0 only for 3.3V level.

BAT1

Battery

EC-D6_8-P1_5-H2

NOTES:(very important!!!)

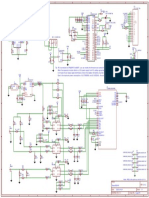

The HDMI differential trace impedance is 100ohm. If DVDD3318_RGMIILCD is connected to 3.3V

VO of HI3519AV100 the schematic diagram of hardware design of DVDD3318_RGMIILCD

is refered to Hi3519AV100 hardware design user guide

HDMI_TX0P V37 1A19 INTB_FPD

HDMI_TX0N V36 HDMI_TX0P

HDMI_TX0N

LCD_CLK/VOU1120_CLK/VOU656_CLK

GPIO14_2

Make sure that the voltage difference between DVDD3318_RGMIILCD and DVDD18_RGMIILCD

HDMI_TX1P U36 1C15 FPD_LOCK

HDMI_TX1N U37 HDMI_TX1P LCD_DATA0/VOU1120_DATA7 is within ± 1.98 V during power-on and power-off.

HDMI_TX2P R37 HDMI_TX1N VOU656_DATA0/UART3_RXD/GPIO0_0 1A15 FPD_PASS

0V8_LDO HDMI_TX2N R36 HDMI_TX2P LCD_DATA1/VOU1120_DATA6

HDMI_TXCP Y36 HDMI_TX2N VOU656_DATA1/UART3_TXD/GPIO0_1 1B15 PDB_FPD If DVDD3318_RGMIILCD is connected to 3.3V

HDMI_TXCN Y37 HDMI_TXCP LCD_DATA2/VOU1120_DATA5

LB42 120R@100Mhz_0.12R_1A_0402 HDMI_TXCN VOU656_DATA2/UART3_RTSN

HDMI_SCL 1K18 UART6_RXD/GPIO0_2 1A16

Set the output voltage of these pins to 3.3 V by referring to

1 2 AVDD08_HDMITX HDMI_SDA 1K19 HDMI_SCL LCD_DATA3/VOU1120_DATA4

HDMI_CEC 1H19 HDMI_SDA

U3E

VOU656_DATA3/UART3_CTSN Hi3519AV100 3.3 V/1.8 V I/O Application Note.

HDMI_HOTPLUG 1L19 HDMI_CEC UART6_TXD/GPIO0_3 1B16 LED_CTRL2

HDMI_HOTPLUG LCD_DATA4/VOU1120_DATA3 If the voltage is set to 1.8 V, these I/O pins may be damaged.

C52

R0402 VOU656_DATA4/UART5_RXD/GPIO0_4

1A17

AVDD08_HDMITX 1H15 LCD_DATA5/VOU1120_DATA2

AVDD08_HDMITX VOU656_DATA5/UART5_TXD/GPIO0_5 1B17 LED_CTRL1

LCD_DATA6/VOU1120_DATA1

4.7UF

<DEVICE> VOU656_DATA6/UART6_RXD/GPIO0_6

LCD_DATA7/VOU1120_DATA0

1C17 3V3_RGMIILCD 3V3_PER

Q17

C0402 AVDDPLL_HDMITX 1H16 VOU656_DATA7/UART6_TXD/GPIO0_7

B36

AVDD18PLL_HDMITX RGMII_TXD3/VOU1120_DATA15 D S

LCD_DATA12/I2C8_SCL/UART6_RXD

LCD_DATA10/SPI3_SDI/GPIO12_7

C36 R1272

VO Interface 5 of 7

RGMII_TXD2/VOU1120_DATA14 C857

1V8_SOC CJ3401

AVDDDRV_HDMITX1H18 LCD_DATA14/I2C8_SDA/UART6_TXD

10uF

100K

G

AVDD33DRV_HDMITX LCD_DATA11/SPI3_CSN/GPIO6_7 D36 R46 RMII_TXD0 R1273 C859

1000R@100Mhz_1.25R_0.25A_0402 33 sot23-gds

LB51 RGMII_TXD0/LCD_HSYNC/SPI3_SDI

I2C8_SCL/GPIO9_4/TEST_OUT4/RMII_TXD0 C0805 R0402

D37 R47 R0402 33 RMII_TXD1 2K 1uF

1 2 AVDDPLL_HDMITX RGMII_TXD1/LCD_DE/SPI3_SDO

I2C7_SDA/GPIO6_6/TEST_OUT3/RMII_TXD1 C0402

R242 12K 1J19 E36 R48 R0402 33 RMII_TXEN R0402

HDMI_REXT RGMII_TXEN/SPI3_SDO/SPI3_SCLK R1271

I2C7_SDA/I2C7_SCL/TEST_OUT2/RMII_TXEN

C40

R0402 R0402 GPIO12_6 R0402

1B18 R49 33 RMII_REF_CLK 100K

RGMII_TXCKOUT/RMII_CLK

C

T36 LCD_DATA8/SPI3_CSN/I2C8_SDA

R0402 R1269 R0402

AVSS_HDMITX1 TEST_OUT5/GPIO9_5

470NF

W36 1C19 B Q18

AA36 AVSS_HDMITX2 RGMII_RXD3/VOU1120_DATA13 1V8_SOC

AVSS_HDMITX3 LCD_DATA8/I2C7_SCL/UART5_RXD 2K

1G15 NPN/NC

E

1G16 AVSS_HDMITX4 SPI3_SCLK/VSYNC_TE_MIPITX R0402

C0402 AVSS_HDMITX5 GPIO12_1 R1270 sot23-bec

1H17 1D19

1J18 AVSS_HDMITX6 RGMII_RXD2/VOU1120_DATA12

3V3_SOC AVSS_HDMITX7 LCD_DATA10/LCD_DATA9/I2C7_SDA

UART5_TXD/SPI3_SDO/GPIO12_2 10K

1C18 RMII_RXD1

RGMII_RXD1/LCD_VSYNC/UART3_RXD R0402

GPIO12_3/RMII_RXD1 1E19 RMII_RXD0

AVDDDRV_HDMITX RGMII_RXD0/SPI3_SCLK/I2C7_SCL

R61 10K

UART3_TXD/GPIO12_4/RMII_RXD0 1D18 RMII_CRSDV

3V3_RGMIILCD RGMII_RXDV/LCD_DATA11

C58

R0402

UART3_RTSN/UART6_RXD

GPIO12_0/TEST_OUT0/RMII_CRS_DV 1F18

RGMII_RXCK/LCD_DATA15

UART3_CTSN

4.7UF

1C16 <Variant Name>

DVDD3318_RGMIILCD1 UART6_TXD/TEST_OUT1/GPIO12_5 EPHY_RSTN

1B19

1D16 EPHY_RSTN/LCD_DATA9

C0402 1V8_SOC DVDD3318_RGMIILCD2 VOU1120_DATA11/LCD_DE

TEST_OUT7/GPIO11_7

深圳为有视讯有限公司

1E18 R53 33 EPHY_CLK

EPHY_CLK/LCD_DATA13

VOU1120_DATA10/TEST_OUT6

1D14 R0402

DVDD18_RGMIILCD1 GPIO11_6

1F19 MDIO

1D15 MDIO/SPI3_CSN/VOU1120_DATA8

DVDD18_RGMIILCD2 I2C8_SDA/TEST_OUT9/GPIO14_1 1G18 MDCK

R54 33 Progecet

MDCK/SPI3_SDI/VOU1120_DATA9

I2C8_SCL/TEST_OUT8/GPIO14_0 Name T3-MAINPCB-V1.0.0

R0402

HBGA567-16-3737 Document

Number HI3519AV100_SYSTEM Desigend Rev 1.0

Date: Friday, November 23, 2018 Sheet 7 of 15 Size A2

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Samsung g532gDocument44 pagesSamsung g532gEKO ARISANDI89% (9)

- s805 Box SchematicDocument10 pagess805 Box Schematicq hw2012No ratings yet

- 2BU001 V2.01 DL S56 DualDocument20 pages2BU001 V2.01 DL S56 DualRiza VirsadaNo ratings yet

- Kim Uno Rev1 SchematicDocument1 pageKim Uno Rev1 SchematicweaponNo ratings yet

- Esquema Reducido ZeroW PDFDocument1 pageEsquema Reducido ZeroW PDFRoberto VicenteNo ratings yet

- Level 3 Repair: 8-1. Components LayoutDocument40 pagesLevel 3 Repair: 8-1. Components LayoutJerry Isaac Guerra HilarioNo ratings yet

- 2BT061 - V1 03 - DL (150121)Document22 pages2BT061 - V1 03 - DL (150121)Riza VirsadaNo ratings yet

- RIFFBOX2 Interface ConnectorsDocument1 pageRIFFBOX2 Interface ConnectorsApolo ApoloNo ratings yet

- Schematic MAINDocument1 pageSchematic MAINTNUT CK3No ratings yet

- NEJE KZ Board SchematicDocument1 pageNEJE KZ Board Schematicvictor Sanmiguel0% (1)

- IT8720F CxsDocument1 pageIT8720F CxslioNo ratings yet

- w706 v3.1 lpddr2 Mipilcm 2015030Document14 pagesw706 v3.1 lpddr2 Mipilcm 2015030Jhon Fredy Diaz CorreaNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument42 pagesLevel 3 Repair: 8-1. Block Diagramمحمد مشلوشNo ratings yet

- Iprog Mainboard SCHDocument1 pageIprog Mainboard SCHnelson lince100% (1)

- 610c rm-836 SchematicDocument42 pages610c rm-836 SchematicVladimir GutarraNo ratings yet

- OPPO F5 SchematicDocument22 pagesOPPO F5 SchematicYasir Shabeer100% (1)

- Piu202 Piu302 Piu202 Piu302: Pic1101 Pic1101Document1 pagePiu202 Piu302 Piu202 Piu302: Pic1101 Pic1101Bautista100% (1)

- Uart LDO 3.3VDocument2 pagesUart LDO 3.3VMas SamNo ratings yet

- Block DiagramDocument3 pagesBlock DiagramttatontokevinNo ratings yet

- EduShield SchematicDocument1 pageEduShield SchematicPlaymr 365No ratings yet

- Mueller Experiments Kromrey Brandt Tesla BediniDocument15 pagesMueller Experiments Kromrey Brandt Tesla BediniVlad AdrianNo ratings yet

- Schematic - POCO X3 Pro - 2023 09 27Document4 pagesSchematic - POCO X3 Pro - 2023 09 27kashi kashiNo ratings yet

- SM-A260F Common Tshoo 7 PDFDocument24 pagesSM-A260F Common Tshoo 7 PDFRamíro ChocotecóNo ratings yet

- Duinomite Mini Rev CDocument1 pageDuinomite Mini Rev Cnathantshama1No ratings yet

- Nanovna-H: Title: Rev: Date: Sheet: Easyeda V5.4.12 Drawn byDocument1 pageNanovna-H: Title: Rev: Date: Sheet: Easyeda V5.4.12 Drawn byMarcelo Roberto Gadotti100% (3)

- (NB Solutions) Ducati MB v4p0 r1.0Document12 pages(NB Solutions) Ducati MB v4p0 r1.0trutlept100% (1)

- SM-J330F_Tshoo_7Document47 pagesSM-J330F_Tshoo_7toma1No ratings yet

- SM-J330F Tshoo 7Document47 pagesSM-J330F Tshoo 7Muhamad TediNo ratings yet

- R1B S41M98HC1 (X600)Document8 pagesR1B S41M98HC1 (X600)Riza VirsadaNo ratings yet

- RTS5176EDocument1 pageRTS5176EevilplayerindoNo ratings yet

- LA-9104P VAW00 Inspiron 3521-8Document1 pageLA-9104P VAW00 Inspiron 3521-8samarxdasNo ratings yet

- 2019 T Con Amp Screen Panel Repair Guide Kent Liewpdf 5 PDF Free - Part9Document35 pages2019 T Con Amp Screen Panel Repair Guide Kent Liewpdf 5 PDF Free - Part9EveraldoNo ratings yet

- MICROCONROLLERDocument1 pageMICROCONROLLERFırat KağıtçıNo ratings yet

- 13 LSPs912 G1 1703 Schem 3462937Document10 pages13 LSPs912 G1 1703 Schem 3462937Глеб ЖигловNo ratings yet

- S802 MBX Ref Basic V03 131212 ReDocument16 pagesS802 MBX Ref Basic V03 131212 ReyhyzhjNo ratings yet

- Wa0017Document44 pagesWa0017nacer gheNo ratings yet

- Troubleshooting PDFDocument44 pagesTroubleshooting PDFibrahim (baim)No ratings yet

- QCC3031-BTM331 SCHDocument1 pageQCC3031-BTM331 SCHliemnv.ic1984No ratings yet

- Wistron Egret - Vga Agp - Rev SBDocument7 pagesWistron Egret - Vga Agp - Rev SBRM EletronicaNo ratings yet

- 610 RM-835 Schem@ PlacementDocument41 pages610 RM-835 Schem@ PlacementRiza VirsadaNo ratings yet

- Samsung M105GDocument61 pagesSamsung M105GMerku MichoNo ratings yet

- Schematic - WIFI Wall Switch 2 WayDocument1 pageSchematic - WIFI Wall Switch 2 WayMarius MihaiNo ratings yet

- Captivate Development Kit: Processor PCB To Panel PCB Connector Haptic Drive CircuitDocument2 pagesCaptivate Development Kit: Processor PCB To Panel PCB Connector Haptic Drive CircuitPankaj Rupani100% (3)

- HP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aDocument67 pagesHP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aNeven PiscutiNo ratings yet

- MB Manual Z790-Aero-G 1001 e 230406Document41 pagesMB Manual Z790-Aero-G 1001 e 230406gasvargas77No ratings yet

- Vestel 17mb70-5-Sema SCHDocument16 pagesVestel 17mb70-5-Sema SCHАлексей ТатарскихNo ratings yet

- AFX00002 Full PinoutDocument1 pageAFX00002 Full Pinoutclem37codNo ratings yet

- Wistron Jv50-Pu - Finger Print BoardDocument1 pageWistron Jv50-Pu - Finger Print BoardAlfonso BDNo ratings yet

- Acer Aspire - 5338 - 5736G - 5738 - 5738G - 5738DG - 5738 1 08245-1 - JV50-MV - 01 - Finger - Print - BoardDocument1 pageAcer Aspire - 5338 - 5736G - 5738 - 5738G - 5738DG - 5738 1 08245-1 - JV50-MV - 01 - Finger - Print - BoardffffNo ratings yet

- Wistron Jv50-Pu - Finger Print Board (Diagramas - Com.br)Document1 pageWistron Jv50-Pu - Finger Print Board (Diagramas - Com.br)rapazdosnotesNo ratings yet

- 1110C ConDocument1 page1110C Consong_trangNo ratings yet

- DVA T4 Power Supply (Scheme p.1 of 3)Document1 pageDVA T4 Power Supply (Scheme p.1 of 3)Ümit GÜNGÖRNo ratings yet

- 6508 00e PDFDocument56 pages6508 00e PDFJulio Luis Sánchez MompiéNo ratings yet

- Tu Put A Madre 564168Document28 pagesTu Put A Madre 564168joladawehiNo ratings yet

- A9 接口板 40 023T1Document1 pageA9 接口板 40 023T1易行胜No ratings yet

- GT-S5300 Service ManualDocument47 pagesGT-S5300 Service ManualNo-OneNo ratings yet

- 1p - Smart Meter - Rev-03Document4 pages1p - Smart Meter - Rev-03infoNo ratings yet

- Rpi SCH 2b 1p2 ReducedDocument1 pageRpi SCH 2b 1p2 Reducedvijaykumarn100% (1)

- SCHEMATICS sr28c51351 - B - NA - VZ - PROD - 0302Document97 pagesSCHEMATICS sr28c51351 - B - NA - VZ - PROD - 0302wallison AndradeNo ratings yet

- Appendix B-AcceessoriesDocument17 pagesAppendix B-AcceessoriesaryojunyantoNo ratings yet

- = 510 μA. Determine β, α, and iDocument6 pages= 510 μA. Determine β, α, and ib1041049 110-niu-studentNo ratings yet

- AMPHENOL Series 3Document36 pagesAMPHENOL Series 3PTCNo ratings yet

- Introduction To Electrical InstallationDocument30 pagesIntroduction To Electrical InstallationMohamad Taib Miskon100% (1)

- Part-2 Electric DrivesDocument37 pagesPart-2 Electric Drivesankushff7872No ratings yet

- Adm CS EvccDocument3 pagesAdm CS EvccAnvesh AnanthulaNo ratings yet

- Digital Temperature Controllers: Model Number StructureDocument5 pagesDigital Temperature Controllers: Model Number StructureYandi HidayatNo ratings yet

- Me218b - Team 13 Bom - Parts ListDocument2 pagesMe218b - Team 13 Bom - Parts Listapi-340751025No ratings yet

- Panasonic Sa-Tm54 Mini ComboDocument146 pagesPanasonic Sa-Tm54 Mini ComboPerez PepoNo ratings yet

- ASSESSMENT G8 TLE q2Document2 pagesASSESSMENT G8 TLE q2Maria Chelo AgosNo ratings yet

- Fona XDG: Service and Installation ManualDocument32 pagesFona XDG: Service and Installation ManualKhaled MokhtariNo ratings yet

- MantDocument2 pagesMantAstudillo Garcia DanielNo ratings yet

- Application of Power Diode in Power ElectronicsDocument18 pagesApplication of Power Diode in Power ElectronicsSahale Shera Lutse 18BEE0376No ratings yet

- Powervalue 31/11 T 10/20 Kva: User ManualDocument37 pagesPowervalue 31/11 T 10/20 Kva: User ManualRabia akramNo ratings yet

- Lecture 1-Transformer Voltages and The General Transformer EquationDocument3 pagesLecture 1-Transformer Voltages and The General Transformer EquationJohn Abernard TubioNo ratings yet

- Finder-70 11 8 230 2022-Datasheet PDFDocument10 pagesFinder-70 11 8 230 2022-Datasheet PDFovidiuNo ratings yet

- R12 T07B24 Ifmi XX XX SDW El 00064Document1 pageR12 T07B24 Ifmi XX XX SDW El 00064Abrar DigitalNo ratings yet

- Irf 630Document7 pagesIrf 630ban4444No ratings yet

- Transistor TesterDocument4 pagesTransistor TesteraurodenNo ratings yet

- BPE (Lab Manual)Document15 pagesBPE (Lab Manual)Ahmad Awais ChoudhryNo ratings yet

- Capaciter Working PrincipalDocument2 pagesCapaciter Working PrincipalSanjivee SachinNo ratings yet

- TEAL PDU Module in HFD Cabinet Manual (5113474) - SM - DOC1744019 - 2Document52 pagesTEAL PDU Module in HFD Cabinet Manual (5113474) - SM - DOC1744019 - 2gua gua100% (1)

- Guide On Supercapacitor Leakage Current Behavior in EH ApplicationsDocument4 pagesGuide On Supercapacitor Leakage Current Behavior in EH ApplicationsCazimir BostanNo ratings yet

- Abb Acs800 Drive ManualDocument124 pagesAbb Acs800 Drive Manualvũ trầnNo ratings yet

- TB6575FNG: PreliminaryDocument13 pagesTB6575FNG: PreliminaryjicoelhoNo ratings yet

- Relay Iso9002: (Unit:mm) (Unit:mm)Document2 pagesRelay Iso9002: (Unit:mm) (Unit:mm)Gabun KirillNo ratings yet

- L293D Motor Driver PDFDocument6 pagesL293D Motor Driver PDFPedro Cu Aguirre100% (1)

- CAT4-2 Complete ENDocument264 pagesCAT4-2 Complete ENalltheloveintheworldNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument5 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product Specificationangel bastidasNo ratings yet

- ACS 1000W PMWorkInstDocument22 pagesACS 1000W PMWorkInstJinNo ratings yet