Professional Documents

Culture Documents

Pmodi2s RM

Pmodi2s RM

Uploaded by

pskumarvlsipdCopyright:

Available Formats

You might also like

- DS001 Rev.04 - Datasheet HT32SX V2.2 - 19022021Document18 pagesDS001 Rev.04 - Datasheet HT32SX V2.2 - 19022021RaimundoNo ratings yet

- Asahi Kasei Microdevices AK4462VN - C1870772Document104 pagesAsahi Kasei Microdevices AK4462VN - C1870772Artur SchmidtNo ratings yet

- AK4493 - E-00 Dec 13th 2017Document104 pagesAK4493 - E-00 Dec 13th 2017bentNo ratings yet

- Imcp Ht32Sx - Sip SigfoxDocument16 pagesImcp Ht32Sx - Sip SigfoxMarcelBortolotiNo ratings yet

- AK4452VNDocument87 pagesAK4452VNJudon ArroyoNo ratings yet

- Bluetooth Low Energy 4.2 Soc With Audio Codec General DescriptionDocument264 pagesBluetooth Low Energy 4.2 Soc With Audio Codec General DescriptionspotNo ratings yet

- P1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical DataDocument106 pagesP1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical Datareza_azadNo ratings yet

- Ds Maestro 2Document48 pagesDs Maestro 2GregNo ratings yet

- ES1988Document60 pagesES1988GregNo ratings yet

- 192 KHZ Digital Audio Interface Receiver: FeaturesDocument60 pages192 KHZ Digital Audio Interface Receiver: FeaturesmercyjohnNo ratings yet

- stm32f091cc 956209 PDFDocument129 pagesstm32f091cc 956209 PDFHảoNgôNo ratings yet

- Da14583 Fs 3v0 PDFDocument230 pagesDa14583 Fs 3v0 PDFspot100% (1)

- Brooklyn AdcDocument20 pagesBrooklyn AdcdavidartefactNo ratings yet

- AK4499 Feb2019Document117 pagesAK4499 Feb2019PeterNo ratings yet

- 192 KHZ Digital Audio Interface Receiver: Features General DescriptionDocument59 pages192 KHZ Digital Audio Interface Receiver: Features General DescriptionpiroNo ratings yet

- MPC 5565 PDFDocument54 pagesMPC 5565 PDFvarimasrNo ratings yet

- Wavefront AL1402G OptoRec Data SheetDocument9 pagesWavefront AL1402G OptoRec Data SheetmylitalindaNo ratings yet

- Bluetooth Low Energy 4.2 Soc General Description: FinalDocument234 pagesBluetooth Low Energy 4.2 Soc General Description: FinalspotNo ratings yet

- RPM Measurement (Tachometer)Document10 pagesRPM Measurement (Tachometer)19E45A0229 SDESEEENo ratings yet

- Ak4458 DatasheetDocument90 pagesAk4458 Datasheettawit2001No ratings yet

- Document Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualDocument32 pagesDocument Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualSilver ProNo ratings yet

- Mcf52259 Coldfire Microcontroller: Data Sheet: Technical DataDocument46 pagesMcf52259 Coldfire Microcontroller: Data Sheet: Technical DataCHAITANYA531No ratings yet

- Cypress Product Roadmap Public 001-89435 - 0LDocument255 pagesCypress Product Roadmap Public 001-89435 - 0LKumar BabuNo ratings yet

- Low Cost, Low Power CMOS General-Purpose Dual Analog Front End AD73322LDocument48 pagesLow Cost, Low Power CMOS General-Purpose Dual Analog Front End AD73322LAnirban MitraNo ratings yet

- Asahi Kasei Microdevices AK4637EN - C2649367Document96 pagesAsahi Kasei Microdevices AK4637EN - C2649367Artur SchmidtNo ratings yet

- DS At32f403a V2.01 enDocument88 pagesDS At32f403a V2.01 enDinusha AmerasingheNo ratings yet

- ARM7 LPC2129 Processor RegistersDocument34 pagesARM7 LPC2129 Processor RegistersAnchal ChaturvedyNo ratings yet

- Bluetooth Based Home Appliances ControllerDocument77 pagesBluetooth Based Home Appliances ControllerCrispNo ratings yet

- stm32f100cb PDFDocument96 pagesstm32f100cb PDFCiprian FrigioiNo ratings yet

- SAM4S Datasheet PDFDocument1,163 pagesSAM4S Datasheet PDFDaniel TelloNo ratings yet

- BP1064L2 Datasheet Preliminary V0.5Document18 pagesBP1064L2 Datasheet Preliminary V0.5Huỳnh Quốc ViệtNo ratings yet

- Microchip ATSAMD21G18A AUT DatasheetDocument972 pagesMicrochip ATSAMD21G18A AUT DatasheetmicNo ratings yet

- DMOS Driver For 3-Phase Brushless DC Motor: DescriptionDocument34 pagesDMOS Driver For 3-Phase Brushless DC Motor: Descriptionluis lopezNo ratings yet

- R8C24 25 Flyer (24-003A)Document2 pagesR8C24 25 Flyer (24-003A)nagforuNo ratings yet

- RTL 8186Document50 pagesRTL 8186Maria Alejandra DalcolmoNo ratings yet

- MC56F8006/MC56F8002 Digital Signal ControllerDocument106 pagesMC56F8006/MC56F8002 Digital Signal Controllerchatty85No ratings yet

- Ak4332ecb en DatasheetDocument81 pagesAk4332ecb en DatasheetBenjaminNo ratings yet

- BK1086-88 Datasheet v1.0Document30 pagesBK1086-88 Datasheet v1.0BradMorseNo ratings yet

- NDS3332 IP QAM Modulator User Manual 201610Document24 pagesNDS3332 IP QAM Modulator User Manual 201610PT. GARUDA SUPER LINKNo ratings yet

- STM 32 F 107 VCDocument108 pagesSTM 32 F 107 VCShin YenNo ratings yet

- ST72324Jx ST72324Kx: 5V Range 8-Bit Mcu With 8 To 32K Flash, 10-Bit Adc, 4 Timers, Spi, Sci InterfaceDocument164 pagesST72324Jx ST72324Kx: 5V Range 8-Bit Mcu With 8 To 32K Flash, 10-Bit Adc, 4 Timers, Spi, Sci Interfacemario_turbinadoNo ratings yet

- STM32F072Document128 pagesSTM32F072MaycoNo ratings yet

- tlc6984 DisplayDocument76 pagestlc6984 DisplaySandeep BNo ratings yet

- ST 10Document24 pagesST 10Carlos Henrique SabinoNo ratings yet

- Iot Based Irrigation SystemDocument77 pagesIot Based Irrigation System19E45A0286 SDESEEENo ratings yet

- STM32F103 DatasheetDocument122 pagesSTM32F103 DatasheetKwun Hok ChongNo ratings yet

- STM32 F103 XXDocument123 pagesSTM32 F103 XXporoi7No ratings yet

- ESP8266-12F DocDocument20 pagesESP8266-12F DocplwrlvzxaocrejwruoNo ratings yet

- 10 Mbps ARCNET (ANSI 878.1) Controller With 2Kx8 On-Board RAMDocument89 pages10 Mbps ARCNET (ANSI 878.1) Controller With 2Kx8 On-Board RAMGoh Seng TakNo ratings yet

- DSP Blocks InterfacingDocument30 pagesDSP Blocks Interfacingdolly aryaNo ratings yet

- 6500Document1,118 pages6500apeksha_837No ratings yet

- En DM00090510 PDFDocument128 pagesEn DM00090510 PDFYoussef EssaouariNo ratings yet

- 78M6612 Single-Phase, Dual-Outlet Power and Energy Measurement ICDocument46 pages78M6612 Single-Phase, Dual-Outlet Power and Energy Measurement ICAn Huynh VanNo ratings yet

- Chapter 3 Electronics: November 2012 XP Series S/MDocument30 pagesChapter 3 Electronics: November 2012 XP Series S/MspirisNo ratings yet

- STM32F107XX de Escaner Fvdi J2534 Ford MazdaDocument103 pagesSTM32F107XX de Escaner Fvdi J2534 Ford MazdaJose Otilio Chavez CantuNo ratings yet

- 10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionDocument24 pages10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionpskumarvlsipdNo ratings yet

- HW 7Document2 pagesHW 7pskumarvlsipdNo ratings yet

- HW 8Document6 pagesHW 8pskumarvlsipdNo ratings yet

- HW 10Document4 pagesHW 10pskumarvlsipdNo ratings yet

- HW 9Document3 pagesHW 9pskumarvlsipdNo ratings yet

- A Survey On Cryptography Comparative Study Between RSA Vs ECC Algorithms and RSA Vs El-Gamal AlgorithmsDocument4 pagesA Survey On Cryptography Comparative Study Between RSA Vs ECC Algorithms and RSA Vs El-Gamal AlgorithmspskumarvlsipdNo ratings yet

- A Multiplication Formula and Its Application: Yongwen Zhu Yantai City 264005, P.R. ChinaDocument15 pagesA Multiplication Formula and Its Application: Yongwen Zhu Yantai City 264005, P.R. ChinapskumarvlsipdNo ratings yet

- Dell Inspiron N4010 QUANTA UM8 UMA REV 1ADocument46 pagesDell Inspiron N4010 QUANTA UM8 UMA REV 1ASaumen RoyNo ratings yet

- Visual Programming SFT 5030Document33 pagesVisual Programming SFT 5030Raja GopalNo ratings yet

- Python Programming: Reema TharejaDocument27 pagesPython Programming: Reema TharejaKevinNo ratings yet

- Emerging Systems: Part 1: Quantum ComputingDocument19 pagesEmerging Systems: Part 1: Quantum ComputingSanta GeorgeNo ratings yet

- Operating System Module Only For Exit Exam Preparation DawitDocument29 pagesOperating System Module Only For Exit Exam Preparation DawitFuad EdrisNo ratings yet

- A Guide To Mastering html5 css3 and JavascriptDocument68 pagesA Guide To Mastering html5 css3 and JavascriptchiprutNo ratings yet

- P R O T E U S: Introduction and InstallationDocument17 pagesP R O T E U S: Introduction and InstallationPaolo GarbinNo ratings yet

- Unit-3 - 4 Buffered AcquisitionDocument13 pagesUnit-3 - 4 Buffered AcquisitionDaksh SharmaNo ratings yet

- Turbo Codes For PCS Applications: AbstractDocument6 pagesTurbo Codes For PCS Applications: AbstractMudita ChandraNo ratings yet

- Computer Security-Lab-2Document19 pagesComputer Security-Lab-2Mesay NebelbalNo ratings yet

- View Source Print ?: Predict The Output of The Below ProgramDocument132 pagesView Source Print ?: Predict The Output of The Below ProgrammaneshkandukuriNo ratings yet

- VoLTE FGI GroupDocument6 pagesVoLTE FGI Groupcharan ThakurNo ratings yet

- CV MarufDocument3 pagesCV MarufMaruf MohammedNo ratings yet

- Microprocessor and Peripherals Interfacing Notes: Course Code: ECC501 Class: TE-EXTC Mumbai UniversityDocument10 pagesMicroprocessor and Peripherals Interfacing Notes: Course Code: ECC501 Class: TE-EXTC Mumbai UniversityAnikhet MulkyNo ratings yet

- Concurrent Process Creation and Execution: Multi-ProcessingDocument16 pagesConcurrent Process Creation and Execution: Multi-ProcessingLujainNo ratings yet

- Project 2 Presentation On: Digitized and Decentralized Blockchain Technology For Banking Sector (REVIEW-2)Document22 pagesProject 2 Presentation On: Digitized and Decentralized Blockchain Technology For Banking Sector (REVIEW-2)Sujee ReddyNo ratings yet

- Ijirt144246 PaperDocument6 pagesIjirt144246 PaperAdebanji JoshuaNo ratings yet

- Recalculate Actual Units & CostsDocument4 pagesRecalculate Actual Units & CostsJule LobresNo ratings yet

- Temenos Cloud Close of Business OPERATIONS MANUALDocument8 pagesTemenos Cloud Close of Business OPERATIONS MANUALSuraj JPNo ratings yet

- BITS-battery-tracking Userguide v3.2 Whats New-1Document38 pagesBITS-battery-tracking Userguide v3.2 Whats New-1LijinEMNo ratings yet

- Panasonic MINAS A4 PDFDocument6 pagesPanasonic MINAS A4 PDFedersonsotoNo ratings yet

- Symantec Premium 250-561 70q-DEMODocument18 pagesSymantec Premium 250-561 70q-DEMOAlmir KarastanovićNo ratings yet

- FL17 ParametersDocument1,286 pagesFL17 ParametersChristian JoundaNo ratings yet

- Flow ControlsDocument8 pagesFlow ControlsSadanand Kalya SadashivaiahNo ratings yet

- KY 013 Joy ITDocument6 pagesKY 013 Joy ITTesoro HonNo ratings yet

- 2017 Licensing For Infrastructure Products Using RepriseDocument18 pages2017 Licensing For Infrastructure Products Using RepriseViktor RégerNo ratings yet

- Untitled17 - Jupyter NotebookDocument2 pagesUntitled17 - Jupyter NotebookjackmekaNo ratings yet

- Ss CD Theory Lab Result Sheet C SectionDocument2 pagesSs CD Theory Lab Result Sheet C SectionMadhu CkNo ratings yet

- iThingsPaper PDFDocument7 pagesiThingsPaper PDFAbhijeet Dhanraj SalveNo ratings yet

- Lab 1Document10 pagesLab 1mey chuNo ratings yet

Pmodi2s RM

Pmodi2s RM

Uploaded by

pskumarvlsipdOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pmodi2s RM

Pmodi2s RM

Uploaded by

pskumarvlsipdCopyright:

Available Formats

1300 Henley Court

Pullman, WA 99163

509.334.6306

www.digilentinc.com

PmodI2S™ Reference Manual

Revised April 12, 2016

This manual applies to the PmodI2S rev. A

Overview

The Digilent PmodI2S is a stereo audio module that accepts all major audio data interface formats and sample

rates.

Features include:

Stereo 24-bit D/A converter

Output converted audio signals through standard

headphone jack

Supports all major audio data interface formats

Accepts 16-24 bits of audio data

Small PCB size for flexible designs 1.0 in × 0.8 in (2.5

cm × 2.0 cm)

6-pin Pmod port with GPIO interface

The PmodI2S.

1 Functional Description

The PmodI2S utilizes a Cirrus Logic CS4344 Stereo D/A converter to take digital audio data and output the

corresponding analog signal through a standard stereo headphone jack. It is designed to work at standard audio

rates, although the master clock can run anywhere from 512 kHz to 50 MHz.

2 Interfacing with the Pmod

The PmodI2S communicates with the host board via the GPIO protocol. As this module uses the Integrated

Interchip Sound (I²S) protocol, several different clock lines are required.

The fastest clock signal will be the Master Clock (MCLK); as the name implies, this signal will keep everything nicely

synchronized. The sample rate (Fs) clock, also known as the Left-Right Clock (LRCK) or the Word Select (WS) clock,

indicates when a particular set of data is to be placed on the left or right audio channel for stereo sound.

The final clock is the bit clock, labeled as the Serial Clock (SCK) on the Pmod. This clock can either be provided as a

signal from the host board, or can be internally derived by the Pmod itself by providing at least two consecutive

Copyright Digilent, Inc. All rights reserved.

DOC#: 502-191 Other product and company names mentioned may be trademarks of their respective owners. Page 1 of 3

PmodI2S™ Reference Manual

frames of the LRCK without providing any SCK signals. The on-board chip will then measure the Master Clock rate

and the LRCK rate and determine an appropriate bit clock rate. However, the MCLK/LRCK ratio must meet a set

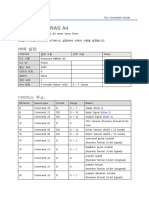

ratio in order to generate an internal SCK, as outlined in the table below from the CS4344 datasheet.

Internal SCK Mode External SCK Mode

16-bit data and SCK = 32*Fs if MCLK/LRCK = 1024, 512, 256,

128, or 64

Up to 24-bit data with data valid on the rising

Up to 24-bit data and SCK = 48*Fs if MCLK/LRCK = 768, 384,

edge of SCK

192, or 96

Up to 24-bit data and SCK = 72*Fs if MCLK/LRCK = 1152

Table 1. MCLK/LRCK ratio.

The ratio between the MCLK and the LRCK rates must be an integer ratio so that the internal clock dividers can

determine an appropriate bit rate. A table of commonly used sample rates and their corresponding MCLK rates

from the CS4344 datasheet is provided below:

LRCK MCLK (MHz)

(kHz) 64x 96x 128x 192x 256x 384x 512x 768x 1024x 1152x

32 - - - - 8.1920 12.2880 - - 32.7680 36.8640

44.1 - - - - 11.2896 16.9344 22.5792 33.8680 45.1580 -

48 - - - - 12.2880 18.4320 24.5760 36.8640 49.1520 -

64 - - 8.9120 12.2880 - - 32.7680 49.1520 - -

88.2 - - 11.2896 16.9344 22.5792 33.8680 - - - -

96 - - 12.2880 18.4320 24.5760 36.8640 - - - -

128 8.1920 12.2880 - - 32.7680 49.1520 - - - -

176.4 11.2896 16.9344 22.5792 33.8680 - - - - - -

192 12.2880 18.4320 24.5760 36.8640 - - - - - -

Mode QSM DSM SSM

Table 2. Sample rates and corresponding MCLK rates.

The I²S protocol requires that data is clocked in on the falling edge of the bit clock. The first bit of data (MSB) is not

clocked in on the falling edge until a first complete bit clock cycle has passed after the LRCK has changed state. The

rising edge of the bit clock clock informs the on board chip that the next bit of data can be read.

The delay of one bit clock cycle before transferring data at each LRCK change also implies that the least significant

bit (LSB) of data will be transferred after the LRCK change has occurred. No particular phase relationship must be

followed with this on-board chip, although the phase relationship must stay consistent throughout audio session.

An example timing diagram of I²S from Texas Instruments is shown below:

Figure 1. PmodI2S timing diagram.

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners. Page 2 of 3

PmodI2S™ Reference Manual

Pin Signal Description

1 MCLK Master Clock

2 LRCK Left-right Clock

3 SCK Serial Clock

4 SDIN Serial Data input

5 GND Power Supply Ground

6 VCC Positive Power Supply

Table 3. Pinout description table.

Any external power applied to the PmodI2S must be within 3V and 5.25V; however, it is recommended that Pmod

is operated at 3.3V.

3 Physical Dimensions

The pins on the pin header are spaced 100 mil apart. The PCB is 1 inch long on the sides parallel to the pins on the

pin header and 0.8 inches long on the sides perpendicular to the pin header.

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners. Page 3 of 3

You might also like

- DS001 Rev.04 - Datasheet HT32SX V2.2 - 19022021Document18 pagesDS001 Rev.04 - Datasheet HT32SX V2.2 - 19022021RaimundoNo ratings yet

- Asahi Kasei Microdevices AK4462VN - C1870772Document104 pagesAsahi Kasei Microdevices AK4462VN - C1870772Artur SchmidtNo ratings yet

- AK4493 - E-00 Dec 13th 2017Document104 pagesAK4493 - E-00 Dec 13th 2017bentNo ratings yet

- Imcp Ht32Sx - Sip SigfoxDocument16 pagesImcp Ht32Sx - Sip SigfoxMarcelBortolotiNo ratings yet

- AK4452VNDocument87 pagesAK4452VNJudon ArroyoNo ratings yet

- Bluetooth Low Energy 4.2 Soc With Audio Codec General DescriptionDocument264 pagesBluetooth Low Energy 4.2 Soc With Audio Codec General DescriptionspotNo ratings yet

- P1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical DataDocument106 pagesP1016 Qoriq Integrated Processor Hardware Specifications: Data Sheet: Technical Datareza_azadNo ratings yet

- Ds Maestro 2Document48 pagesDs Maestro 2GregNo ratings yet

- ES1988Document60 pagesES1988GregNo ratings yet

- 192 KHZ Digital Audio Interface Receiver: FeaturesDocument60 pages192 KHZ Digital Audio Interface Receiver: FeaturesmercyjohnNo ratings yet

- stm32f091cc 956209 PDFDocument129 pagesstm32f091cc 956209 PDFHảoNgôNo ratings yet

- Da14583 Fs 3v0 PDFDocument230 pagesDa14583 Fs 3v0 PDFspot100% (1)

- Brooklyn AdcDocument20 pagesBrooklyn AdcdavidartefactNo ratings yet

- AK4499 Feb2019Document117 pagesAK4499 Feb2019PeterNo ratings yet

- 192 KHZ Digital Audio Interface Receiver: Features General DescriptionDocument59 pages192 KHZ Digital Audio Interface Receiver: Features General DescriptionpiroNo ratings yet

- MPC 5565 PDFDocument54 pagesMPC 5565 PDFvarimasrNo ratings yet

- Wavefront AL1402G OptoRec Data SheetDocument9 pagesWavefront AL1402G OptoRec Data SheetmylitalindaNo ratings yet

- Bluetooth Low Energy 4.2 Soc General Description: FinalDocument234 pagesBluetooth Low Energy 4.2 Soc General Description: FinalspotNo ratings yet

- RPM Measurement (Tachometer)Document10 pagesRPM Measurement (Tachometer)19E45A0229 SDESEEENo ratings yet

- Ak4458 DatasheetDocument90 pagesAk4458 Datasheettawit2001No ratings yet

- Document Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualDocument32 pagesDocument Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualSilver ProNo ratings yet

- Mcf52259 Coldfire Microcontroller: Data Sheet: Technical DataDocument46 pagesMcf52259 Coldfire Microcontroller: Data Sheet: Technical DataCHAITANYA531No ratings yet

- Cypress Product Roadmap Public 001-89435 - 0LDocument255 pagesCypress Product Roadmap Public 001-89435 - 0LKumar BabuNo ratings yet

- Low Cost, Low Power CMOS General-Purpose Dual Analog Front End AD73322LDocument48 pagesLow Cost, Low Power CMOS General-Purpose Dual Analog Front End AD73322LAnirban MitraNo ratings yet

- Asahi Kasei Microdevices AK4637EN - C2649367Document96 pagesAsahi Kasei Microdevices AK4637EN - C2649367Artur SchmidtNo ratings yet

- DS At32f403a V2.01 enDocument88 pagesDS At32f403a V2.01 enDinusha AmerasingheNo ratings yet

- ARM7 LPC2129 Processor RegistersDocument34 pagesARM7 LPC2129 Processor RegistersAnchal ChaturvedyNo ratings yet

- Bluetooth Based Home Appliances ControllerDocument77 pagesBluetooth Based Home Appliances ControllerCrispNo ratings yet

- stm32f100cb PDFDocument96 pagesstm32f100cb PDFCiprian FrigioiNo ratings yet

- SAM4S Datasheet PDFDocument1,163 pagesSAM4S Datasheet PDFDaniel TelloNo ratings yet

- BP1064L2 Datasheet Preliminary V0.5Document18 pagesBP1064L2 Datasheet Preliminary V0.5Huỳnh Quốc ViệtNo ratings yet

- Microchip ATSAMD21G18A AUT DatasheetDocument972 pagesMicrochip ATSAMD21G18A AUT DatasheetmicNo ratings yet

- DMOS Driver For 3-Phase Brushless DC Motor: DescriptionDocument34 pagesDMOS Driver For 3-Phase Brushless DC Motor: Descriptionluis lopezNo ratings yet

- R8C24 25 Flyer (24-003A)Document2 pagesR8C24 25 Flyer (24-003A)nagforuNo ratings yet

- RTL 8186Document50 pagesRTL 8186Maria Alejandra DalcolmoNo ratings yet

- MC56F8006/MC56F8002 Digital Signal ControllerDocument106 pagesMC56F8006/MC56F8002 Digital Signal Controllerchatty85No ratings yet

- Ak4332ecb en DatasheetDocument81 pagesAk4332ecb en DatasheetBenjaminNo ratings yet

- BK1086-88 Datasheet v1.0Document30 pagesBK1086-88 Datasheet v1.0BradMorseNo ratings yet

- NDS3332 IP QAM Modulator User Manual 201610Document24 pagesNDS3332 IP QAM Modulator User Manual 201610PT. GARUDA SUPER LINKNo ratings yet

- STM 32 F 107 VCDocument108 pagesSTM 32 F 107 VCShin YenNo ratings yet

- ST72324Jx ST72324Kx: 5V Range 8-Bit Mcu With 8 To 32K Flash, 10-Bit Adc, 4 Timers, Spi, Sci InterfaceDocument164 pagesST72324Jx ST72324Kx: 5V Range 8-Bit Mcu With 8 To 32K Flash, 10-Bit Adc, 4 Timers, Spi, Sci Interfacemario_turbinadoNo ratings yet

- STM32F072Document128 pagesSTM32F072MaycoNo ratings yet

- tlc6984 DisplayDocument76 pagestlc6984 DisplaySandeep BNo ratings yet

- ST 10Document24 pagesST 10Carlos Henrique SabinoNo ratings yet

- Iot Based Irrigation SystemDocument77 pagesIot Based Irrigation System19E45A0286 SDESEEENo ratings yet

- STM32F103 DatasheetDocument122 pagesSTM32F103 DatasheetKwun Hok ChongNo ratings yet

- STM32 F103 XXDocument123 pagesSTM32 F103 XXporoi7No ratings yet

- ESP8266-12F DocDocument20 pagesESP8266-12F DocplwrlvzxaocrejwruoNo ratings yet

- 10 Mbps ARCNET (ANSI 878.1) Controller With 2Kx8 On-Board RAMDocument89 pages10 Mbps ARCNET (ANSI 878.1) Controller With 2Kx8 On-Board RAMGoh Seng TakNo ratings yet

- DSP Blocks InterfacingDocument30 pagesDSP Blocks Interfacingdolly aryaNo ratings yet

- 6500Document1,118 pages6500apeksha_837No ratings yet

- En DM00090510 PDFDocument128 pagesEn DM00090510 PDFYoussef EssaouariNo ratings yet

- 78M6612 Single-Phase, Dual-Outlet Power and Energy Measurement ICDocument46 pages78M6612 Single-Phase, Dual-Outlet Power and Energy Measurement ICAn Huynh VanNo ratings yet

- Chapter 3 Electronics: November 2012 XP Series S/MDocument30 pagesChapter 3 Electronics: November 2012 XP Series S/MspirisNo ratings yet

- STM32F107XX de Escaner Fvdi J2534 Ford MazdaDocument103 pagesSTM32F107XX de Escaner Fvdi J2534 Ford MazdaJose Otilio Chavez CantuNo ratings yet

- 10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionDocument24 pages10-Pin, 24-Bit, 192 KHZ Stereo D/A Converter: Features DescriptionpskumarvlsipdNo ratings yet

- HW 7Document2 pagesHW 7pskumarvlsipdNo ratings yet

- HW 8Document6 pagesHW 8pskumarvlsipdNo ratings yet

- HW 10Document4 pagesHW 10pskumarvlsipdNo ratings yet

- HW 9Document3 pagesHW 9pskumarvlsipdNo ratings yet

- A Survey On Cryptography Comparative Study Between RSA Vs ECC Algorithms and RSA Vs El-Gamal AlgorithmsDocument4 pagesA Survey On Cryptography Comparative Study Between RSA Vs ECC Algorithms and RSA Vs El-Gamal AlgorithmspskumarvlsipdNo ratings yet

- A Multiplication Formula and Its Application: Yongwen Zhu Yantai City 264005, P.R. ChinaDocument15 pagesA Multiplication Formula and Its Application: Yongwen Zhu Yantai City 264005, P.R. ChinapskumarvlsipdNo ratings yet

- Dell Inspiron N4010 QUANTA UM8 UMA REV 1ADocument46 pagesDell Inspiron N4010 QUANTA UM8 UMA REV 1ASaumen RoyNo ratings yet

- Visual Programming SFT 5030Document33 pagesVisual Programming SFT 5030Raja GopalNo ratings yet

- Python Programming: Reema TharejaDocument27 pagesPython Programming: Reema TharejaKevinNo ratings yet

- Emerging Systems: Part 1: Quantum ComputingDocument19 pagesEmerging Systems: Part 1: Quantum ComputingSanta GeorgeNo ratings yet

- Operating System Module Only For Exit Exam Preparation DawitDocument29 pagesOperating System Module Only For Exit Exam Preparation DawitFuad EdrisNo ratings yet

- A Guide To Mastering html5 css3 and JavascriptDocument68 pagesA Guide To Mastering html5 css3 and JavascriptchiprutNo ratings yet

- P R O T E U S: Introduction and InstallationDocument17 pagesP R O T E U S: Introduction and InstallationPaolo GarbinNo ratings yet

- Unit-3 - 4 Buffered AcquisitionDocument13 pagesUnit-3 - 4 Buffered AcquisitionDaksh SharmaNo ratings yet

- Turbo Codes For PCS Applications: AbstractDocument6 pagesTurbo Codes For PCS Applications: AbstractMudita ChandraNo ratings yet

- Computer Security-Lab-2Document19 pagesComputer Security-Lab-2Mesay NebelbalNo ratings yet

- View Source Print ?: Predict The Output of The Below ProgramDocument132 pagesView Source Print ?: Predict The Output of The Below ProgrammaneshkandukuriNo ratings yet

- VoLTE FGI GroupDocument6 pagesVoLTE FGI Groupcharan ThakurNo ratings yet

- CV MarufDocument3 pagesCV MarufMaruf MohammedNo ratings yet

- Microprocessor and Peripherals Interfacing Notes: Course Code: ECC501 Class: TE-EXTC Mumbai UniversityDocument10 pagesMicroprocessor and Peripherals Interfacing Notes: Course Code: ECC501 Class: TE-EXTC Mumbai UniversityAnikhet MulkyNo ratings yet

- Concurrent Process Creation and Execution: Multi-ProcessingDocument16 pagesConcurrent Process Creation and Execution: Multi-ProcessingLujainNo ratings yet

- Project 2 Presentation On: Digitized and Decentralized Blockchain Technology For Banking Sector (REVIEW-2)Document22 pagesProject 2 Presentation On: Digitized and Decentralized Blockchain Technology For Banking Sector (REVIEW-2)Sujee ReddyNo ratings yet

- Ijirt144246 PaperDocument6 pagesIjirt144246 PaperAdebanji JoshuaNo ratings yet

- Recalculate Actual Units & CostsDocument4 pagesRecalculate Actual Units & CostsJule LobresNo ratings yet

- Temenos Cloud Close of Business OPERATIONS MANUALDocument8 pagesTemenos Cloud Close of Business OPERATIONS MANUALSuraj JPNo ratings yet

- BITS-battery-tracking Userguide v3.2 Whats New-1Document38 pagesBITS-battery-tracking Userguide v3.2 Whats New-1LijinEMNo ratings yet

- Panasonic MINAS A4 PDFDocument6 pagesPanasonic MINAS A4 PDFedersonsotoNo ratings yet

- Symantec Premium 250-561 70q-DEMODocument18 pagesSymantec Premium 250-561 70q-DEMOAlmir KarastanovićNo ratings yet

- FL17 ParametersDocument1,286 pagesFL17 ParametersChristian JoundaNo ratings yet

- Flow ControlsDocument8 pagesFlow ControlsSadanand Kalya SadashivaiahNo ratings yet

- KY 013 Joy ITDocument6 pagesKY 013 Joy ITTesoro HonNo ratings yet

- 2017 Licensing For Infrastructure Products Using RepriseDocument18 pages2017 Licensing For Infrastructure Products Using RepriseViktor RégerNo ratings yet

- Untitled17 - Jupyter NotebookDocument2 pagesUntitled17 - Jupyter NotebookjackmekaNo ratings yet

- Ss CD Theory Lab Result Sheet C SectionDocument2 pagesSs CD Theory Lab Result Sheet C SectionMadhu CkNo ratings yet

- iThingsPaper PDFDocument7 pagesiThingsPaper PDFAbhijeet Dhanraj SalveNo ratings yet

- Lab 1Document10 pagesLab 1mey chuNo ratings yet