Professional Documents

Culture Documents

Week 4 Research

Week 4 Research

Uploaded by

sany6354Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Week 4 Research

Week 4 Research

Uploaded by

sany6354Copyright:

Available Formats

KIARASH GHASEMZADEH

2/28/23

PMOS VTH PROBLEM AND SILICON ON INSULATOR

pMOS Vth problem:

• The threshold voltage (Vth) problem refers to the fact that in the early days of MOSFET

technology, the threshold voltage of the pMOS transistor was much higher than that of the

nMOS transistor. This made it difficult to design circuits that required both nMOS and pMOS

transistors because it was hard to ensure that they would operate at the same voltage level.

The higher threshold voltage of the pMOS transistor was due to the fact that the gate oxide of

pMOS devices was made from a different material than the nMOS devices. The different

material led to a different fixed charge density in the gate oxide, which in turn affected the

threshold voltage.

Researchers overcame the Vth problem by developing new gate oxide materials and fabrication

processes that reduced the difference in threshold voltage between nMOS and pMOS devices.

This made it possible to design and fabricate CMOS circuits that could operate at lower voltage

levels and consume less power.

• researchers have used various techniques to solve the Vth problem in pMOS MOSFETs. One of

the most common methods is the so-called "work function engineering" technique, which

involves modifying the gate electrode material to adjust the effective work function of the gate.

This can be achieved by adding a thin layer of metal with a different work function on top of the

gate electrode, or by doping the gate electrode with a suitable impurity.

Another technique involves using a "punch-through stopper" (PTS) layer in the gate oxide, which

prevents the depletion region from spreading into the channel region and increases the

effective channel length. This helps to reduce the Vth of the pMOS device.

More recently, other techniques such as strained silicon, high-k dielectrics, and metal gate

electrodes have been developed to further improve the performance of pMOS MOSFETs and

address the Vth problem.

Silicon on Insulator (SOI):

• Silicon on Insulator (SOI) is a technology that involves fabricating a thin layer of silicon on top of

a layer of insulating material such as silicon dioxide (SiO2). The insulating layer serves as a

barrier to prevent the flow of electrical charges, and as a result, the electrical behavior of the

thin silicon layer can be different from bulk silicon.

• SOI has several advantages over bulk silicon, including reduced parasitic capacitance, improved

device isolation, and better radiation hardness. The reduced parasitic capacitance leads to faster

switching speeds and lower power consumption, making SOI devices ideal for high-performance

applications such as microprocessors and memory chips.

• SOI technology can be classified into two main categories: partially depleted SOI (PD-SOI) and

fully depleted SOI (FD-SOI). In PD-SOI, the silicon layer is partially depleted of charge carriers,

while in FD-SOI, the silicon layer is completely depleted. FD-SOI provides better control over the

flow of charge carriers, and hence, is better suited for low-power and high-performance

applications.

• SOI technology has evolved over the years, and it is now possible to fabricate SOI wafers with

high uniformity and quality. As a result, SOI technology has become an important platform for

the development of advanced integrated circuits, particularly in the fields of microprocessors,

memory, and high-speed communication.

You might also like

- Lilyum / Lilyum Bym: Lilyum Operator'S ManualDocument96 pagesLilyum / Lilyum Bym: Lilyum Operator'S ManualNassima BELIL100% (2)

- Lab Report VLSIDocument24 pagesLab Report VLSIK Eerti Vyas0% (2)

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsDocument31 pages15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- IPC-7351A & PCBL Land Pattern Naming ConventionDocument6 pagesIPC-7351A & PCBL Land Pattern Naming ConventionSri ramNo ratings yet

- Microwave Antenna AndrewDocument196 pagesMicrowave Antenna AndrewSetiawan Lukmanto100% (4)

- MosfetDocument20 pagesMosfetMohammad Rameez100% (2)

- Imp For IntDocument3 pagesImp For IntsaticitechNo ratings yet

- A Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerDocument10 pagesA Review Paper On Cmos, Soi and Finfet Technology: Einfochips Pvt. Ltd. Ahmedabad, Asic Physical Design EngineerRohit JangidNo ratings yet

- VLSI Unit 2 Technology - SDocument52 pagesVLSI Unit 2 Technology - SIndrajeet GautamNo ratings yet

- Title:-: Nanoscale Devices For Low Power VLSI DesignDocument2 pagesTitle:-: Nanoscale Devices For Low Power VLSI DesignEr Paramjit SinghNo ratings yet

- Fermi FET Technology Seminar ReportDocument21 pagesFermi FET Technology Seminar Reportimcoolsha999No ratings yet

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDocument3 pagesComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedMeiling MizukiNo ratings yet

- Mosfet: Metal Oxide Semiconductor Field Effect TransistorsDocument47 pagesMosfet: Metal Oxide Semiconductor Field Effect Transistorschandanayadav8490No ratings yet

- SOI Implementation Whitepaper Infotech v2Document12 pagesSOI Implementation Whitepaper Infotech v2Võ Đức HiếuNo ratings yet

- Engineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarDocument7 pagesEngineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarjeshkakkadNo ratings yet

- A Review Paper On Cmos, Soi and Finfet TechnologyDocument18 pagesA Review Paper On Cmos, Soi and Finfet TechnologyRamakrishnaRao SoogooriNo ratings yet

- Dynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIDocument9 pagesDynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIBüşra AkyıldızNo ratings yet

- Investigation of FDSOI and PDSOI MOSFETDocument10 pagesInvestigation of FDSOI and PDSOI MOSFETsamactrangNo ratings yet

- A Study On Multi Material Gate All Around SOI MOSFETDocument5 pagesA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelNo ratings yet

- Electronic Devices in MTL Annual Report 1998Document20 pagesElectronic Devices in MTL Annual Report 1998tbsuirNo ratings yet

- Question & AnswerDocument10 pagesQuestion & AnswerArighna BasakNo ratings yet

- FinfetsDocument27 pagesFinfetsAjay JoshyNo ratings yet

- An Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityDocument11 pagesAn Evolutionary Transition of Conventional N MOS VLSI To CMOS Considering Scaling, Low Power and Higher MobilityAJER JOURNALNo ratings yet

- Special Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesDocument11 pagesSpecial Report Soi Wafer Technology For Cmos Ics: Robert Simonton President, Simonton AssociatesMoaaz AhmedNo ratings yet

- Silicon On Insulator TechnologyDocument32 pagesSilicon On Insulator TechnologyJayanth bemesettyNo ratings yet

- Analytical Modeling of Double Gate MosfeDocument57 pagesAnalytical Modeling of Double Gate MosfeVijaya Kumar100% (1)

- Mosfet: By: Mohamed Ahmed EL - Maghawry Mohamed Adel Yomna MohammedDocument16 pagesMosfet: By: Mohamed Ahmed EL - Maghawry Mohamed Adel Yomna MohammedAhmed Mahmoud AhmedNo ratings yet

- EI2403 - VLSI Design 2 Marks With AnswersDocument23 pagesEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNo ratings yet

- FinfetDocument20 pagesFinfetBhautik Pandya100% (2)

- (SOI) Technology Have Emerged As An Efective Means of ExtendingDocument38 pages(SOI) Technology Have Emerged As An Efective Means of ExtendingShwetaAgarwalNo ratings yet

- 2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitDocument7 pages2014 MR - Metal-Layer Capacitors in The 65 NM CMOS Process and The Application For Low-Leakage Power-Rail ESD Clamp CircuitspaulsNo ratings yet

- VLSI Design Unit-2 Mosfet TransistorDocument5 pagesVLSI Design Unit-2 Mosfet Transistorselvi0412No ratings yet

- Introduction To VLSI Technology: Abhijeet KumarDocument32 pagesIntroduction To VLSI Technology: Abhijeet KumarPrithireddy ThenetiNo ratings yet

- 7.6.2. Poly-Silicon Gate TechnologyDocument14 pages7.6.2. Poly-Silicon Gate TechnologyHarshad KulkarniNo ratings yet

- Vlsi DesignDocument58 pagesVlsi Designy satishkumarNo ratings yet

- Vlsi Upto 3unitDocument105 pagesVlsi Upto 3unitAsha PagidipalliNo ratings yet

- Seminar On CmosDocument8 pagesSeminar On CmosRoberto HoodNo ratings yet

- Introduction To MOS TechnologiesDocument15 pagesIntroduction To MOS TechnologieslokeshwarrvrjcNo ratings yet

- Introduction To Vlsi TechnologyDocument32 pagesIntroduction To Vlsi TechnologysivaNo ratings yet

- BASIC VLSI DESIGN .PptsDocument32 pagesBASIC VLSI DESIGN .PptsNarayana Rao RevallaNo ratings yet

- Poly-Si Adv & DisadvDocument1 pagePoly-Si Adv & DisadvGaurav KumarNo ratings yet

- Course Coordinator Module CoordinatorDocument166 pagesCourse Coordinator Module CoordinatorBituNo ratings yet

- L 19 - Mse628a - 30 10 19Document25 pagesL 19 - Mse628a - 30 10 19Dhanishtha SinghNo ratings yet

- Wiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosDocument10 pagesWiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosraoNo ratings yet

- Assignment A1 001 A GIT0723Document14 pagesAssignment A1 001 A GIT0723Shafiq PanicKingNo ratings yet

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDocument38 pagesCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluNo ratings yet

- CMOS BasicsDocument41 pagesCMOS BasicsYeshoda MallikarjunaNo ratings yet

- Mosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickDocument7 pagesMosfet: Surface-Mount D2Pak Volts Amperes Watts MatchstickJudel AnovaNo ratings yet

- Chapter 4 Metal Oxide Semiconductor FET (MOSFET)Document47 pagesChapter 4 Metal Oxide Semiconductor FET (MOSFET)redhataNo ratings yet

- Robert Chau ICSICT Paper 101904Document5 pagesRobert Chau ICSICT Paper 101904yassirkelNo ratings yet

- Cmos Metal GateDocument56 pagesCmos Metal GateSubin AlexNo ratings yet

- Complementary MetalDocument5 pagesComplementary MetalesaidanNo ratings yet

- Analytical Model For Surface Potential and Inversion Charge of Dual Material Double Gate Son MosfetDocument5 pagesAnalytical Model For Surface Potential and Inversion Charge of Dual Material Double Gate Son Mosfetanil kasotNo ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar Reportshefeena_anaz100% (1)

- Finfet: Prepared By: Kirankumar Lad 10VL11FDocument14 pagesFinfet: Prepared By: Kirankumar Lad 10VL11FKirankumar LadNo ratings yet

- Fermi FET Technology Seminar ReportDocument42 pagesFermi FET Technology Seminar ReportPragati VawtulakrNo ratings yet

- Vlsi QBDocument34 pagesVlsi QBKaviya dharshini S -ECE-028No ratings yet

- Automated Optical Inspection: Advancements in Computer Vision TechnologyFrom EverandAutomated Optical Inspection: Advancements in Computer Vision TechnologyNo ratings yet

- On-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsFrom EverandOn-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsNo ratings yet

- Copper Electrodeposition for Nanofabrication of Electronics DevicesFrom EverandCopper Electrodeposition for Nanofabrication of Electronics DevicesNo ratings yet

- Auto-Transformer Design - A Practical Handbook for Manufacturers, Contractors and WiremenFrom EverandAuto-Transformer Design - A Practical Handbook for Manufacturers, Contractors and WiremenRating: 4 out of 5 stars4/5 (2)

- Metallic Oxynitride Thin Films by Reactive Sputtering and Related Deposition Methods: Process, Properties and ApplicationsFrom EverandMetallic Oxynitride Thin Films by Reactive Sputtering and Related Deposition Methods: Process, Properties and ApplicationsNo ratings yet

- Nirvana Fault TreeDocument39 pagesNirvana Fault Treeoscar samoNo ratings yet

- A Dual Band Antenna For GSM Applications 71Document5 pagesA Dual Band Antenna For GSM Applications 71api-257705796No ratings yet

- Operational Noise 0600DB0302Document2 pagesOperational Noise 0600DB0302John VernonNo ratings yet

- Hitachi Magnet HandbookDocument39 pagesHitachi Magnet HandbookSilverio AcuñaNo ratings yet

- Programmable Asic Interconnect 7: Actel ACTDocument14 pagesProgrammable Asic Interconnect 7: Actel ACTVivek100% (2)

- UGRD-EE6202 Electric Circuits Theory 2: Home UGRD-EE6202-2033T Week 14: Final Examination Final ExamDocument18 pagesUGRD-EE6202 Electric Circuits Theory 2: Home UGRD-EE6202-2033T Week 14: Final Examination Final ExamJitlee PapaNo ratings yet

- TLS-420 - SW InkoppDocument1 pageTLS-420 - SW InkoppvbsdxbNo ratings yet

- AWP Assignment 2Document12 pagesAWP Assignment 2Kapil SharmaNo ratings yet

- Apollo Experience Report Command and Service Module Controls and Displays SubsystemDocument27 pagesApollo Experience Report Command and Service Module Controls and Displays SubsystemBob AndrepontNo ratings yet

- TM M672320 340Document2 pagesTM M672320 340Ara AkramNo ratings yet

- Philips+PL9 1+LCD-TVDocument72 pagesPhilips+PL9 1+LCD-TVedsel72100% (1)

- AM and FMDocument11 pagesAM and FMritaempalmadoNo ratings yet

- Iecex Bas 06.0079u Annex 1Document4 pagesIecex Bas 06.0079u Annex 1adinugrohoNo ratings yet

- Swipguard: Installation GuideDocument2 pagesSwipguard: Installation GuidefasihulNo ratings yet

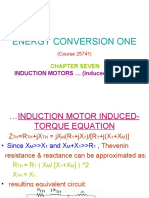

- Energy Conversion One: INDUCTION MOTORS (Induced Torque )Document10 pagesEnergy Conversion One: INDUCTION MOTORS (Induced Torque )prasad243243No ratings yet

- Sheet Contents Revision Info RevisionDocument19 pagesSheet Contents Revision Info RevisionjuanNo ratings yet

- List at Least 20 Electrical/electronic Components and Their Corresponding SymbolsDocument10 pagesList at Least 20 Electrical/electronic Components and Their Corresponding SymbolsMnemosyneNo ratings yet

- MV Prefabricated Equipment GAM Cubicle: Incoming or Outgoing Cable Unit Up To 24 KVDocument3 pagesMV Prefabricated Equipment GAM Cubicle: Incoming or Outgoing Cable Unit Up To 24 KVmas zak danielNo ratings yet

- Silicon Controlled Rectifiers (SCR) SpecificationsDocument3 pagesSilicon Controlled Rectifiers (SCR) SpecificationsdocsndlsNo ratings yet

- 3U EPS User ManualDocument45 pages3U EPS User ManualCalvin LauNo ratings yet

- Compactline Antenna, Single Polarized, 4 FT 7.125 - 8.5 GHZ: Technical Data Sheet Sb4-W71BdDocument2 pagesCompactline Antenna, Single Polarized, 4 FT 7.125 - 8.5 GHZ: Technical Data Sheet Sb4-W71BdJulián GiménezNo ratings yet

- DS8168GWWW 24V 10mmDocument6 pagesDS8168GWWW 24V 10mmSALV2049No ratings yet

- Chapter 8Document29 pagesChapter 8Deivasigamani SubramaniyanNo ratings yet

- "H-Bridge Quad Mosfet Driver For DC Motor Control": Submitted by Ritesh KakkarDocument16 pages"H-Bridge Quad Mosfet Driver For DC Motor Control": Submitted by Ritesh KakkarRitesh KakkarNo ratings yet

- Iv RepotDocument16 pagesIv Repotneethurj9No ratings yet

- Microwave MeasurementDocument56 pagesMicrowave MeasurementIndraysh Vijay [EC - 76]No ratings yet