Professional Documents

Culture Documents

Bde Unit 3

Bde Unit 3

Uploaded by

hiralbhavanaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Bde Unit 3

Bde Unit 3

Uploaded by

hiralbhavanaCopyright:

Available Formats

BDE CHAPTER-3 SUBJECT CODE: 4320703

INTRODUCTION:

Any Boolean function can be implemented using only AND And INVERT gates since the OR

function can be generated by a combination of these two gates, as shown in Figure 2.20(a). It

follows that these two gates can implement any arbitrary Boolean function and they are said to

form a complete set.

NEED OF SIMPLIFICATION IN IMPLEMENTATION OF BOOLEAN

FUNCTION:

The simplification of Boolean functions is mainly used to reduce the number of gates in a logic

circuit. Less number of gates means less power consumption, sometimes the circuit works faster

and also when number of gates is reduced, cost also comes down (Marcovitz, A. B., (2007), Mano,

M. M., and Ciletti, M. D., (2003) & Mano, M. M., (1984)). There are many ways to simplify a

logic design, such as algebraic simplification, Karnough maps, Tabulation Method and

Diagrammatic technique using 'Venn-like diagram' some of them are discussed in detail in

this introduction (Marcovitz, A. B., (2005), Anton, A. E., (2005), Mano, M. M., Colette, M. D.,

(2003), & Mano, M. M., (1984)). In this paper, a new fast systematic method for minimization of

the Boolean function is introduced. Such method is a very simple because there is no need to any

visual representation such as Karnough map or arrangement technique such as Tabulation

method and very easy for programming. This method is very suitable for high variables

(more than 4 variable) boolean function, and very simple for students (Mano, M. M., and

Ciletti, M. D., (2003) & Mano, M. M., (1984)). Furthermore, neural networks are used to

implement Boolean functions because they can recognize patterns even with noise, distortion or

deformation in shape. This is very important especially in communication applications.

KARNAUGH MAP:

In many digital circuits and practical problems we need to find expression with minimum

variables. We can minimize Boolean expressions of 3, 4 variables very easily using K-map

without using any Boolean algebra theorems. K-map can take two forms Sum of Product (SOP)

and Product of Sum (POS) according to the need of problem. K-map is table like representation

but it gives more information than TRUTH TABLE. We fill grid of K-map with 0’s and 1’s then

solve it by making groups.

Steps to solve expression using K-map-

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

1. Select K-map according to the number of variables.

2. Identify minters or masters as given in problem.

3. For SOP put 1’s in blocks of K-map respective to the minters (0’s elsewhere).

4. For POS put 0’s in blocks of K-map respective to the masters (1’s elsewhere).

5. Make rectangular groups containing total terms in power of two like 2, 4, 8.. (Except 1) and

try to cover as many elements as you can in one group.

6. From the groups made in step 5 find the product terms and sum them up for SOP form.

SOP FORM:

1. K-map of 3 variables –

K-map SOP form for 3 variables

Z= ∑A, B, C (1,3,6,7)

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

From red group we get product term—

A’C

From green group we get product term—

AB

Summing these product terms we get- Final expression (A’C+AB)

2. K-map for 4 variables –

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

K-map 4 variable SOP form

F(P,Q,R,S)=∑(0,2,5,7,8,10,13,15)

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

From red group we get product term—

QS

From green group we get product term—

Q’S’

Summing these product terms we get- Final expression (QS+Q’S’)

POS FORM:

1. K-map of 3 variables –

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

K-map 3 variable POS form

F(A,B,C)=π(0,3,6,7)

CANONICAL SUM OF PRODUCTS:

Canonical Sop form means Canonical Sum of Products form. In this form, each product term

contains all literals. So, these product terms are nothing but the min terms. Hence, canonical SoP

form is also called as sum of min terms form.

METHOD OF CONSTRUCTION KARNAUGH MAP:

The K-map is a systematic way of simplifying Boolean expressions. With the help of the K-map

method, we can find the simplest POS and SOP expression, which is known as the minimum

expression. The K-map provides a cookbook for simplification.

Just like the truth table, a K-map contains all the possible values of input variables and their

corresponding output values. However, in K-map, the values are stored in cells of the array. In

each cell, a binary value of each input variable is stored.

The K-map method is used for expressions containing 2, 3, 4, and 5 variables. For a higher number

of variables, there is another method used for simplification called the Quine-McClusky method.

In K-map, the number of cells is similar to the total number of variable input combinations. For

example, if the number of variables is three, the number of cells is 2 3=8, and if the number of

variables is four, the number of cells is 24. The K-map takes the SOP and POS forms. The K-map

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

grid is filled using 0's and 1's. The K-map is solved by making groups. There are the following

steps used to solve the expressions using K-map:

1. First, we find the K-map as per the number of variables.

2. Find the maxterm and minterm in the given expression.

3. Fill cells of K-map for SOP with 1 respective to the minterms.

4. Fill cells of the block for POS with 0 respective to the maxterm.

5. Next, we create rectangular groups that contain total terms in the power of two like 2, 4, 8,

and try to cover as many elements as we can in one group.

6. With the help of these groups, we find the product terms and sum them up for the SOP

form.

SIMPLEFICATION OF KARNAUGH MAP:

With this general idea of K-maps, let us now move on to the procedure employed in designing an

optimal (in terms of the number of logic gates used to realize the logic) digital system. We'll start

with a given problem statement.

Example 1:

Design a digital system whose output is defined as logically low if the 4-bit input binary

number is a multiple of 3; otherwise, the output will be logically high. The output is defined

if and only if the input binary number is greater than 2.

Step 1: Truth Table / Canonical Expression Leading to Min- or Max-Terms

The first step in designing any digital system is to have a clear idea of the variables involved in

the process, along with their state values. Further, depending on the problem statement, we have

to arrive at the number of output variables and their values for each and every combination of the

input literals, which can be conveniently represented in the form of a truth table.

In the given example:

The number of input variables = 4, which we will call A, B, C, and D.

The number of output variables = 1, which we will call Y.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Where:

Y = "Don't Care," if the input number is less than 3 (orange entries in the truth table)

Y = 0, if the input number is an integral multiple of 3 (green entries in the truth table)

Y = 1, if the input number is not an integral multiple of 3 (blue entries in the truth table)

Table 1. Truth table

Note that, in addition to the input and output columns, the truth table also has a column that gives

the decimal equivalent of the input binary combination, which makes it easy for us to arrive at the

minterm or maxterm expansion for the given problem. Thus for the given example:

Minterm expansion will be ∑m(4,5,7,8,10,11,13,14) + ∑d (0,1,2)

Maxterm expansion will be ∏M(3,6,9,12,15) · ∏D (0,1,2)

However, sometimes the logical expression which is to be simplified might be directly given in

terms of SOP or POS forms. In this case, the requirement for the truth table can be overlooked

provided that we express the given expression in its canonical form, from which the

corresponding minterms or maxterms can be obtained.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Step 2: Select and Populate K-Map

From Step 1, we know the number of input variables involved in the logical expression from which

the size of the K-map required will be decided. Further, we also know the number of such K-maps

required to design the desired system as the number of output variables would also be known

definitely. This means, that for the example considered, we require a single (due to one output

variable) K-map with 16 cells (as there are four input variables).

Next, we have to fill the K-map cells with one for each minterm, zero for each maxterm, and X for

"Don't Care" terms. The procedure is to be repeated for every single output variable. For this

example, we get the K-map as shown in Figure 2.

Figure 2. A completely filled 4-variable K-map

Step 3: Form the Groups

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

K-map simplification can also be referred to as the "simplification by grouping" technique as it

solely relies on the formation of clusters. That is, the main aim of the entire process is to gather

together as many ones (for SOP solution) or zeros (for POS solution) under one roof for each of

the output variables in the problem stated. However, while doing so, we have to strictly abide by

certain rules and regulations:

The process has to be initiated by grouping the bits which lie in adjacent cells such that the

group formed contains the maximum number of selected bits. This means that for an n-

variable K-map with 2n cells, try to group for 2 n cells first, then for 2 n-1 cells, next for 2n-

2

cells, and so on until the “group” contains only 2 0 cells, i.e., isolated bits (if any). Note that

the number of cells in the group must be equal to an integer power to 2, i.e., 1, 2, 4, 8. . . .

The procedure must be applied for all adjacent cells of the K-map, even when they appear to

be not adjacent—the top row is considered to be adjacent to the bottom row and the rightmost

column is considered to be adjacent to the leftmost column as if the K-map wraps around

from top to bottom and right to left. For example, Group 1 of SOP form solution in Table 2.

A bit appearing in one group can be repeated in another group provided that this leads to an

increase in the resulting group size. For example, cell 5 is repeated in both Group 3 and 4 in

the SOP form solution of Table 2 as it results in forming a group with two cells instead of a

group with just one cell.

"Don’t Care" conditions should be considered for the grouping activity if and only if they

help obtain a larger group. Otherwise, they are to be neglected. Here the "Don't Care" terms

in cells 0 and 1 are considered to create Group 2 of SOP solution form as it results in a group

with four cells instead of just two.

Table 2.

SOP Form Solution POS Form Solution

Number of groups

0 0

having 16 cells

Number of groups

0 0

having 8 cells

Number of groups having Group 1 (Cells 0,2,8,10)

Group 1 (Cells

4 cells (Blue Enclosures in 2 1

Group 2 (Cells 0,1,4,5) 0,1,2,3)

Figure 3)

Group 3 (Cells Group 4 (Cells Group 2 (Cells

Number of groups having 5,7) 5,13) 1,9)

2 cells (Orange Enclosures 4 2

in Figure 3) Group 5 (Cells Group 6 (Cells Group 3 (Cells

10,11) 10,14) 2,6)

Number of groups having Group 4 (Cell 12)

1 cell (Green Enclosures in 0 2

Figure 3) Group 5 (Cell 15)

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Thus, for the example considered, the K-map showing the groups can be obtained as given in

Figure 3 whose information is summarized in Table 1.

Figure 3. K-maps grouped for (a) SOP solution and (b) POS solution

Step 4: Simplified Logical Expression

For each of the resulting groups, we have to obtain the corresponding logical expression for the

input variables. This can be done by expressing the bits which are common amongst the Gray

code-words which represent the cells contained within the considered group. Another way to

describe the process of obtaining the simplified logical expression for a group is to eliminate the

variable(s) for which the corresponding bits appear within the group as both 0 and 1.

Finally, all these group-wise logical expressions need to be combined appropriately to form the

simplified Boolean equation for the output variable. The same procedure must be repeated for

every output variable of the given problem.

For instance, in the example considered, the logical term for Group 2 of the SOP form solution is

obtained as A̅C̅. This is because this group has 0 as the common Gray code-word bit both along

its rows as well as its columns, highlighted in Figure 4(a). This gives us the literals A̅ and C̅.

Similarly, in the case of Group 1 of POS form solution, we can obtain the logical expression as

A+B. This is because the group has the common Gray code-words as 0,0 along its row only (no

code-word bits are common along its columns) which correspond to the input variables A and B.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Figure 4. K-map simplification technique for (a) SOP solution and (b) POS solution

Following this same process, we can obtain the logical terms corresponding to each of the groups

to finally form the logical expression for the particular output, as shown in Table 3.

Table 3.

SOP Form Solution POS Form Solution

Groups Logical Expression Groups Logical Expression

Group 1 B̅D̅ Group 1 A+B

Group 2 A̅C̅ Group 2 B+C+D̅

Group 3 A̅BD Group 3 A+C̅+D

Group 4 BC̅D Group 4 A̅+B̅+C+D

Group 5 AB̅C Group 5 A̅+B̅+C̅+D̅

Group 6 ACD̅

Thus, Y = B̅D̅ + A̅C̅ + A̅BD + BC̅D + AB̅C + ACD̅ Thus, Y = (A+B) (B+C+D̅) (A+C̅+D) (A̅+B̅+C+D) (A̅+B̅+C̅+D̅)

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Step 5: System Design

Having obtained the simplified logical expression, we can decide on the type and the number of

gates required to realize the expected logic for every output bit, which further results in the

complete design of the desired system.

Thus, the digital system corresponding to SOP and POS forms of solution for the given example

can be designed using the basic gates like NOT, AND, and OR as shown in Figure 5(a) and 5(b).

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Figure 5. Digital system corresponding to (a) SOP form of solution and (b) POS form of solution

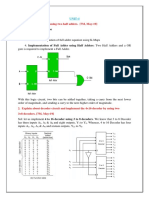

NAND/NOR IMPLEMENTATION OF BOOLEAN FUNCTION:

Any logic function can be implemented using NAND gates. To achieve this, first the logic function

has to be written in Sum of Product (SOP) form. Once logic function is converted to SOP, then is

very easy to implement using NAND gate. In other words any logic circuit with AND gates in first

level and OR gates in second level can be converted into a NAND-NAND gate circuit.

Consider the following SOP expression

F = W.X.Y + X.Y.Z + Y.Z.W

The above expression can be implemented with three AND gates in first stage and one OR gate

in second stage as shown in figure.

If bubbles are introduced at AND gates output and OR gates inputs (the same for NOR gates), the

above circuit becomes as shown in figure.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Now replace OR gate with input bubble with the NAND gate. Now we have circuit which is fully

implemented with just NAND gates.

Realization of logic gates using NAND gates

Implementing an inverter using NAND gate

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

Realization of logic function using NOR gates

Any logic function can be implemented using NOR gates. To achieve this, first the logic function

has to be written in Product of Sum (POS) form. Once it is converted to POS, then it's very easy

to implement using NOR gate. In other words any logic circuit with OR gates in first level and

AND gates in second level can be converted into a NOR-NOR gate circuit.

Consider the following POS expression

F = (X+Y) . (Y+Z)

The above expression can be implemented with three OR gates in first stage and one AND gate in

second stage as shown in figure.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

If bubble are introduced at the output of the OR gates and the inputs of AND gate, the above

circuit becomes as shown in figure.

Now replace AND gate with input bubble with the NOR gate. Now we have circuit which is fully

implemented with just NOR gates.

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

BDE CHAPTER-3 SUBJECT CODE: 4320703

V.P.M.P POLYTECHNIC ELECTRICAL DEPARTMENT

You might also like

- Cse 331 HW 1 2Document8 pagesCse 331 HW 1 2api-522855390No ratings yet

- Groups Notes by TrockersDocument17 pagesGroups Notes by Trockerstapiwa nzvatu100% (1)

- NG - Argument Reduction For Huge Arguments: Good To The Last BitDocument8 pagesNG - Argument Reduction For Huge Arguments: Good To The Last BitDerek O'ConnorNo ratings yet

- 16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 MuxDocument4 pages16-1 Mux Using 8-1 Mux, 4-1mux, and 2-1 Muxsatishbojjawar148458% (19)

- BADASS Tutorial Karnaugh MapsDocument16 pagesBADASS Tutorial Karnaugh MapsdjpsychoscientzNo ratings yet

- STLD Unit - Ii (Original Notes)Document59 pagesSTLD Unit - Ii (Original Notes)Saipriya KadiyalaNo ratings yet

- Co Assignment AnswersDocument14 pagesCo Assignment AnswersSravani GunnuNo ratings yet

- K MapDocument30 pagesK MapDollyRajdevNo ratings yet

- K MapDocument30 pagesK MapngeievyiNo ratings yet

- The Double-Base Number System and Its Application To Elliptic Curve CryptographyDocument30 pagesThe Double-Base Number System and Its Application To Elliptic Curve CryptographyVinh CuongNo ratings yet

- Extended K-Map For Minimizing Multiple Output Logic CircuitsDocument8 pagesExtended K-Map For Minimizing Multiple Output Logic CircuitsAnonymous e4UpOQEPNo ratings yet

- Unit IiDocument79 pagesUnit IiThiriveedhi SubbarayuduNo ratings yet

- Cs Important Questions by UjjwalDocument19 pagesCs Important Questions by Ujjwalkumawatujjwal18No ratings yet

- Major ProjectDocument78 pagesMajor ProjectManas MehrotraNo ratings yet

- Efficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogDocument12 pagesEfficient Implementation of 16-Bit Multiplier-Accumulator Using Radix-2 Modified Booth Algorithm and SPST Adder Using VerilogAnonymous e4UpOQEPNo ratings yet

- COEN 3103 Lesson 5 - Boolean Function Simplification Part 2 - Karnaugh Map MethodDocument48 pagesCOEN 3103 Lesson 5 - Boolean Function Simplification Part 2 - Karnaugh Map MethodAkosi LenaNo ratings yet

- "The Map Method For Synthesis of Combinational Logic Circuits" Karnaugh, Maurice (November 1953)Document7 pages"The Map Method For Synthesis of Combinational Logic Circuits" Karnaugh, Maurice (November 1953)inExcelsisDeo100% (1)

- MCC Esa99 FinalDocument14 pagesMCC Esa99 FinalAdemar CardosoNo ratings yet

- Tutorial KmapsDocument8 pagesTutorial KmapsCalledo JLNo ratings yet

- Logic Circuits Experiment 4Document14 pagesLogic Circuits Experiment 4Eman Albino100% (1)

- Digital System Design LecturesDocument132 pagesDigital System Design LecturesAnmar Hasan50% (2)

- Modified Quine-Mccluskey Method: Jadhav Vitthal, Buchade Amar, Pune, Maharashtra, IndiaDocument4 pagesModified Quine-Mccluskey Method: Jadhav Vitthal, Buchade Amar, Pune, Maharashtra, IndiaRiz WanNo ratings yet

- Logic Design NotesDocument193 pagesLogic Design NotesAnup Konnur100% (1)

- Question Bank For Digital Signal Processing Regulation 2013Document8 pagesQuestion Bank For Digital Signal Processing Regulation 2013PRIYA RAJINo ratings yet

- Numerical Solution of 2d Gray-Scott ModelDocument6 pagesNumerical Solution of 2d Gray-Scott ModelKarthik VazhuthiNo ratings yet

- Xperiment O. 6: Digital Logic Design Laboratory Hand BookDocument12 pagesXperiment O. 6: Digital Logic Design Laboratory Hand BookM. Ahmad RazaNo ratings yet

- Transition-Activity Aware Design of Reduction-Stages For Parallel MultipliersDocument6 pagesTransition-Activity Aware Design of Reduction-Stages For Parallel MultipliersBala MuruganNo ratings yet

- Chapter2 BOOLEANROBIAH99Document33 pagesChapter2 BOOLEANROBIAH99MARZIAH91No ratings yet

- (K-Map) KARNAUGH MAP PDFDocument13 pages(K-Map) KARNAUGH MAP PDFmaprofNo ratings yet

- Matlab Basics Tutorial: Electrical and Electronic Engineering & Electrical and Communication Engineering StudentsDocument23 pagesMatlab Basics Tutorial: Electrical and Electronic Engineering & Electrical and Communication Engineering StudentssushantnirwanNo ratings yet

- ADE_PreparatoryQBDocument3 pagesADE_PreparatoryQBShivaayNo ratings yet

- Combinational Logic CircuitsDocument22 pagesCombinational Logic CircuitsDanushkaniroshanNo ratings yet

- Digital Electronics Question Bank, Digital Electronics 2 Mark Questions & AnswersDocument22 pagesDigital Electronics Question Bank, Digital Electronics 2 Mark Questions & Answerssaipradeepkp92% (74)

- Dld Lab6 StmuDocument13 pagesDld Lab6 Stmuhassan aliNo ratings yet

- Data Structures Assignment: Problem 1Document7 pagesData Structures Assignment: Problem 1api-26041279No ratings yet

- Karnaugh Maps - Rules of Simplification: Grouping OnesDocument14 pagesKarnaugh Maps - Rules of Simplification: Grouping OnesProfessor RajputNo ratings yet

- Iterative Data Detection and Channel Estimation For Single-Parity Check-Product Coded MIMO Wireless Communications SystemDocument5 pagesIterative Data Detection and Channel Estimation For Single-Parity Check-Product Coded MIMO Wireless Communications SystemIsa FirmantoNo ratings yet

- Simplification Using K-MapDocument8 pagesSimplification Using K-MapSiegrique Ceasar A. JalwinNo ratings yet

- Ece III Logic Design (10es33) NotesDocument193 pagesEce III Logic Design (10es33) NotesAditya HegadeNo ratings yet

- ADE-Updated-questionbankDocument7 pagesADE-Updated-questionbankShivaayNo ratings yet

- International Journal of Engineering Research and Development (IJERD)Document6 pagesInternational Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Ex 2 SolutionDocument13 pagesEx 2 SolutionMian AlmasNo ratings yet

- Experiment-5 Simplification Using Karnaugh Map 5-1 Object:: Electrical Power Technical Engineering DeptDocument3 pagesExperiment-5 Simplification Using Karnaugh Map 5-1 Object:: Electrical Power Technical Engineering DeptMohammed Dyhia Ali100% (1)

- Final ExamDocument5 pagesFinal ExamSebastianCaceresNo ratings yet

- 14Document13 pages14admin2146No ratings yet

- Hassan Assignment 1 DLDDocument7 pagesHassan Assignment 1 DLDsanee rajpootNo ratings yet

- Smoothing and Differentiation of Data by Simplified Least Squares ProceduresDocument13 pagesSmoothing and Differentiation of Data by Simplified Least Squares ProceduresMadan LakshmananNo ratings yet

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Document10 pagesDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- Digital ElectronicsDocument28 pagesDigital Electronicspriya adhavanNo ratings yet

- Synthesizers: Mathematical Digital Delta-Sigma Modulators Fractional-NDocument4 pagesSynthesizers: Mathematical Digital Delta-Sigma Modulators Fractional-NbrufoNo ratings yet

- Ece-Iii-Logic Design (10es33) - Assignment PDFDocument3 pagesEce-Iii-Logic Design (10es33) - Assignment PDFmahesh24pkNo ratings yet

- Different Simplex MethodsDocument7 pagesDifferent Simplex MethodsdaselknamNo ratings yet

- 2 To 1 MuxDocument19 pages2 To 1 MuxTelmoDiez100% (1)

- Title:: Experiment - 02Document5 pagesTitle:: Experiment - 02MD Saifuzzaman SohanNo ratings yet

- K-Map MethodDocument3 pagesK-Map MethodfionaNo ratings yet

- Rate MatchingDocument5 pagesRate MatchingvgguhaNo ratings yet

- Chapter 2 RegularExpressionsDocument95 pagesChapter 2 RegularExpressionsአርቲስቶቹ Artistochu animation sitcom by habeshan memeNo ratings yet

- Maths Tuition Test (Class - 6) : A) 4386 B) 31,600 C) 63,712 D) 28693Document8 pagesMaths Tuition Test (Class - 6) : A) 4386 B) 31,600 C) 63,712 D) 28693Yedu KrishnaNo ratings yet

- Y3A Practice Book Answers White Rose Maths EditionDocument18 pagesY3A Practice Book Answers White Rose Maths EditionNgọc YếnNo ratings yet

- Workload Estimation For Low-Delay Segmented ConvolutionDocument4 pagesWorkload Estimation For Low-Delay Segmented ConvolutionRobert MoresNo ratings yet

- Quiz 2b SolutionsDocument6 pagesQuiz 2b SolutionsPaul JonesNo ratings yet

- Worksheet October 24 SolutionsDocument12 pagesWorksheet October 24 SolutionsodbayNo ratings yet

- Solutions Pamphlet: American Invitational Mathematics Examination (AIME)Document10 pagesSolutions Pamphlet: American Invitational Mathematics Examination (AIME)James SayerNo ratings yet

- VibraDocument20 pagesVibraGholamreza IlkhaniNo ratings yet

- DELCON PaperDocument7 pagesDELCON PaperNandi ?No ratings yet

- Mathematics: Quarter 1 - Module 7Document21 pagesMathematics: Quarter 1 - Module 7Gerald RabeNo ratings yet

- sEMIDETAILED LESSON PLAN (Hubby)Document5 pagessEMIDETAILED LESSON PLAN (Hubby)Joem'z Burlasa-Amoto Esler-DionaldoNo ratings yet

- Probabilities A. IntroductionDocument11 pagesProbabilities A. IntroductionBella LendioNo ratings yet

- mct4c Course OutlineDocument2 pagesmct4c Course Outlineapi-423501795No ratings yet

- Q1W1D2Document5 pagesQ1W1D2Angela RuleteNo ratings yet

- Eda6 - Sklearn - neighbors.KNeighborsClassifierDocument6 pagesEda6 - Sklearn - neighbors.KNeighborsClassifierAngelito alneg CarYu MendelNo ratings yet

- Instructional Strategies Chapter: Mathematics FrameworkDocument21 pagesInstructional Strategies Chapter: Mathematics FrameworkRosemarie DinggayNo ratings yet

- FET Colleges - Institutions of First ChoiceDocument156 pagesFET Colleges - Institutions of First ChoiceMike Stuart0% (1)

- Fowles 08Document18 pagesFowles 08jjmaldonisNo ratings yet

- Laboratory Activity #4 NumsolDocument4 pagesLaboratory Activity #4 Numsoljames ceballosNo ratings yet

- Joint Variation m3 L3 October 3-5Document5 pagesJoint Variation m3 L3 October 3-5Kheza Bohol Deliman Dañas100% (1)

- Nama: Etik Eliza NIM: B1A020107 Kelas: C Biologi Praktikum Statistika DeskriptifDocument23 pagesNama: Etik Eliza NIM: B1A020107 Kelas: C Biologi Praktikum Statistika DeskriptifEtik ElizaNo ratings yet

- Digital Assignment - I Computational Fluid Dynamics: Course Code-Mee4006Document19 pagesDigital Assignment - I Computational Fluid Dynamics: Course Code-Mee4006SIDDHANT KUMAR 17BEM0015No ratings yet

- Operations ResearchDocument293 pagesOperations Researchtechnical saurabhNo ratings yet

- Year 4 Maths Sample Test: Time Allowed: 45 MinutesDocument10 pagesYear 4 Maths Sample Test: Time Allowed: 45 Minutesemmanuel richardNo ratings yet

- AA Division AlgorithmDocument4 pagesAA Division AlgorithmSakinah Nurul FajriNo ratings yet

- Increments and Straight Lines: Babylon University / College of Engineering Building Construction / 1 StageDocument7 pagesIncrements and Straight Lines: Babylon University / College of Engineering Building Construction / 1 Stageهاني عاطف جبارNo ratings yet

- MATH4030 Differential Geometry, 2017-18 Solutions To MidtermDocument5 pagesMATH4030 Differential Geometry, 2017-18 Solutions To MidtermErland GarciaNo ratings yet