Professional Documents

Culture Documents

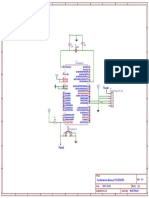

HP Compaq Presario CQ42 - Quanta Ax1 - Rev 1a-6

HP Compaq Presario CQ42 - Quanta Ax1 - Rev 1a-6

Uploaded by

samarxdasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HP Compaq Presario CQ42 - Quanta Ax1 - Rev 1a-6

HP Compaq Presario CQ42 - Quanta Ax1 - Rev 1a-6

Uploaded by

samarxdasCopyright:

Available Formats

1 2 3 4 5 6 7 8

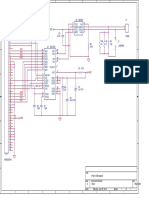

AUBURNDALE/CLARKSFIELD PROCESSOR (GND)

U16H U16I

AUBURNDALE/CLARKSFIELD PROCESSOR( RESERVED, CFG)

U16E

07

K27 VSS161

AT20 VSS1 VSS81 AE34 K9 VSS162 <12> DDR_VREF_DQ0 J17 SA_DIMM_VREF RSVD_NCTF_41 AT2

AT17 VSS2 VSS82 AE33 K6 VSS163 <13> DDR_VREF_DQ1 H17 SB_DIMM_VREF RSVD_NCTF_42 AT3

AR31 VSS3 VSS83 AE32 K3 VSS164 RSVD_NCTF_43 AR1

A AR28 AE31 J32 CFG0 AM30 AL28 A

VSS4 VSS84 VSS165 CFG[0] RSVD45

AR26 VSS5 VSS85 AE30 J30 VSS166 AM28 CFG[1] RSVD46 AL29

AR24 VSS6 VSS86 AE29 J21 VSS167 AP31 CFG[2] RSVD47 AP30

AR23 AE28 J19 CFG3 AL32 AP32

VSS7 VSS87 VSS168 CFG4 CFG[3] RSVD48

AR20 VSS8 VSS88 AE27 H35 VSS169 AL30 CFG[4] RSVD49 AL27

AR17 VSS9 VSS89 AE26 H32 VSS170 AM31 CFG[5] RSVD50 AT31

AR15 VSS10 VSS90 AE6 H28 VSS171 AN29 CFG[6]

AR12 AD10 H26 CFG7 AM32 AT32

VSS11 VSS91 VSS172 CFG[7] RSVD51

AR9 VSS12 VSS92 AC8 H24 VSS173 AK32 CFG[8] RSVD52 AP33

AR6 VSS13 VSS93 AC4 H22 VSS174 AK31 CFG[9] RSVD53 AR33

AR3 VSS14 VSS94 AC2 H18 VSS175 AK28 CFG[10] RSVD_NCTF_54 AT33

AP20 VSS15 VSS95 AB35 H15 VSS176 AJ28 CFG[11] RSVD_NCTF_55 AT34

AP17 VSS16 VSS96 AB34 H13 VSS177 AN30 CFG[12] RSVD_NCTF_56 AP35

AP13 VSS17 VSS97 AB33 H11 VSS178 AN32 CFG[13] RSVD_NCTF_57 AR35

AP10 VSS18 VSS98 AB32 H8 VSS179 AJ32 CFG[14] RSVD58 AR32

AP7 VSS19 VSS99 AB31 H5 VSS180 AJ29 CFG[15] RSVD_TP_59 E15

AP4 VSS20 VSS100 AB30 H2 VSS181 AJ30 CFG[16] RSVD_TP_60 F15

AP2 VSS21 VSS101 AB29 G34 VSS182 AK30 CFG[17]

AN34 VSS22 VSS102 AB28 G31 VSS183 H16 RSVD_TP_86 KEY A2

AN31 VSS23 VSS103 AB27 G20 VSS184 RSVD62 D15

AN23 VSS24 VSS104 AB26 G9 VSS185 AP25 RSVD1 RSVD63 C15

AN20 VSS25 VSS105 AB6 G6 VSS186 AL25 RSVD2 RSVD64 AJ15 RSVD64_R R172 *0_4

AN17 AA10 G3 AL24 AH15 RSVD65_R R171 *0_4

RESERVED

VSS26 VSS106 VSS187 RSVD3 RSVD65

AM29 VSS27 VSS107 Y8 F30 VSS188 AL22 RSVD4 RSVD_TP_66 AA5

AM27 VSS28 VSS108 Y4 F27 VSS189 AJ33 RSVD5 RSVD_TP_67 AA4

AM25 VSS29 VSS109 Y2 F25 VSS190 AG9 RSVD6 RSVD_TP_68 R8

AM20 VSS30 VSS110 W35 F22 VSS191 M27 RSVD7 RSVD_TP_69 AD3

AM17 VSS31 VSS111 W34 F19 VSS192 L28 RSVD8 RSVD_TP_70 AD2

AM14 VSS32 VSS112 W33 F16 VSS193

B AM11 VSS33 VSS113 W32 E35 VSS194 G25 RSVD11 RSVD_TP_71 AA2 B

AM8 VSS34 VSS114 W31 E32 VSS195 G17 RSVD12 RSVD_TP_72 AA1

AM5 VSS35 VSS115 W30 E29 VSS196 E31 RSVD13 RSVD_TP_73 R9

AM2 VSS36 VSS116 W29 E24 VSS197 E30 RSVD14 RSVD_TP_74 AG7

AL34 W28 E21 B19 AE3

AL31

AL23

VSS37

VSS38

VSS39

VSS VSS117

VSS118

VSS119

W27

W26

E18

E13

VSS198

VSS199

VSS200

VSS R44 *0_4 TP_RSVD17_R

A19

A20

RSVD15

RSVD16

RSVD17

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

V4

V5

AL20 W6 E11 R43 *0_4 TP_RSVD18_R B20 N2

VSS40 VSS120 VSS201 RSVD18 RSVD_TP_78

AL17 VSS41 VSS121 V10 E8 VSS202 U9 RSVD19 RSVD_TP_79 AD5

AL12 VSS42 VSS122 U8 E5 VSS203 T9 RSVD20 RSVD_TP_80 AD7

AL9 VSS43 VSS123 U4 E2 VSS204

AL6 VSS44 VSS124 U2 D33 VSS205 AC9 RSVD21 RSVD_TP_81 W3

AL3 VSS45 VSS125 T35 D30 VSS206 AB9 RSVD22 RSVD_TP_82 W2

AK29 VSS46 VSS126 T34 D26 VSS207 C1 RSVD_NCTF_23 RSVD_TP_83 N3

AK27 VSS47 VSS127 T33 D9 VSS208 A3 RSVD_NCTF_24 RSVD_TP_84 AE5

AK25 VSS48 VSS128 T32 D6 VSS209 J29 RSVD26 RSVD_TP_85 AD9

AK20 VSS49 VSS129 T31 D3 VSS210 J28 RSVD27

AK17 VSS50 VSS130 T30 C34 VSS211 A34 RSVD_NCTF_28

AJ31 VSS51 VSS131 T29 C32 VSS212 A33 RSVD_NCTF_29

AJ23 VSS52 VSS132 T28 C29 VSS213 C35 RSVD_NCTF_30 VSS AP34

AJ20 VSS53 VSS133 T27 C28 VSS214

AJ17 VSS54 VSS134 T26 C24 VSS215 B35 RSVD_NCTF_31

AJ14 VSS55 VSS135 T6 C22 VSS216 AJ13 RSVD32

AJ11 VSS56 VSS136 R10 C20 VSS217 AJ12 RSVD33

AJ8 VSS57 VSS137 P8 C19 VSS218 AH25 RSVD34

AJ5 VSS58 VSS138 P4 C16 VSS219 AK26 RSVD35

AJ2 VSS59 VSS139 P2 B31 VSS220 AL26 RSVD36

AH35 VSS60 VSS140 N35 B25 VSS221 AR2 RSVD_NCTF_37

AH34 VSS61 VSS141 N34 B21 VSS222 AJ26 RSVD38

C AH33 VSS62 VSS142 N33 B18 VSS223 AJ27 RSVD39 C

AH32 VSS63 VSS143 N32 B17 VSS224 AP1 RSVD_NCTF_40

AH31 VSS64 VSS144 N31 B13 VSS225

AH30 N30 B11 IC,AUB_CFD_rPGA,R1P0

VSS65 VSS145 VSS226

AH29 VSS66 VSS146 N29 B8 VSS227

AH28 VSS67 VSS147 N28 B6 VSS228

AH27 VSS68 VSS148 N27 B4 VSS229

AH26 VSS69 VSS149 N26 A29 VSS230

AH20 VSS70 VSS150 N6 A27 VSS231

AH17 VSS71 VSS151 M10 A23 VSS232

AH13 VSS72 VSS152 L35 A9 VSS233

AH9 VSS73 VSS153 L32

AH6 VSS74 VSS154 L29 AT35 VSS_NCTF1

AH3 VSS75 VSS155 L8 AT1 VSS_NCTF2

AG10 L5 AR34 For Discrete only

NCTF

VSS76 VSS156 VSS_NCTF3

AF8 VSS77 VSS157 L2 B34 VSS_NCTF4

AF4 VSS78 VSS158 K34 B2 VSS_NCTF5

AF2 VSS79 VSS159 K33 B1 VSS_NCTF6

AE35 VSS80 VSS160 K30 A35 VSS_NCTF7 CFG0 R155 *3.01K_NC

IC,AUB_CFD_rPGA,R1P0 CFG3 R146 3.01K/F_4

IC,AUB_CFD_rPGA,R1P0 CFG4 R144 *3.01K_NC

CFG7 R150 *3.01K/F_4

1 0

CFG[ 1:0 ] - PCI_Epress Configuration Select

D CFG4 Enabled; An external Display port * 11= 1 x 16 PEG D

(Display Port Disabled; No Physical Display Port device is connected to the Embedded * 10= 2 x 8 PEG

Presence) attached to Embedded Diplay Port Display port

The Clarkfield processor's PCI Express interface may

not meet PCI Express 2.0 jitter specifications. Intel CFG0

recommends placing a 3.01K +/- 5% pull down resistor to (PCI-Epress Single PEG Bifurcation enabled

PROJECT :AX1

VSS on CFG[7] pin for both rPGA and BGA components.

This pull down resistor should be removed when this

Configuration Select) Quanta Computer Inc.

issue is fixed. CFG3

Normal Operation Lane Numbers Reversed Size Document Number Rev

(PCI-Epress Static Custom

PROCESSER 4/4 (GND) 1A

Lane Reversal) 15 -> 0 , 14 -> 1

Date: Thursday, November 12, 2009 Sheet 6 of 40

1 2 3 4 5 6 7 8

You might also like

- SparkPlug CrossReference Updated 123015 7Document3 pagesSparkPlug CrossReference Updated 123015 7Alex VdbusscheNo ratings yet

- Comparison of Aluminum Casting AlloysDocument2 pagesComparison of Aluminum Casting Alloyszoran100% (1)

- VSX-295, 405, 425Document11 pagesVSX-295, 405, 425Geiler Antonio Luna MosqueraNo ratings yet

- Tabella Comparazione CandeleDocument2 pagesTabella Comparazione CandeleFrancesco Marzari ChiesaNo ratings yet

- Equivalencia 5Document1 pageEquivalencia 5andre alexandroNo ratings yet

- 140 KDocument15 pages140 KWillian BrucaloNo ratings yet

- Junta Doors Gmt-319 28 Nov 08 ADocument24 pagesJunta Doors Gmt-319 28 Nov 08 AAdriana MuñizNo ratings yet

- 13KRP3D3 00062636 3Document13 pages13KRP3D3 00062636 3Sourabh TiwariNo ratings yet

- International Standards Comparison Chart - Tool SteelDocument2 pagesInternational Standards Comparison Chart - Tool SteelAmirtharaaj VijayanNo ratings yet

- SMD Coduri Marcare SimplificataDocument0 pagesSMD Coduri Marcare SimplificataMuresan SanduNo ratings yet

- ET3610 Fm/Am LCD ET3610 12 Cmos: COB 36 (ET3610B) QFP 44 (ET3610Q)Document10 pagesET3610 Fm/Am LCD ET3610 12 Cmos: COB 36 (ET3610B) QFP 44 (ET3610Q)vetchboyNo ratings yet

- AM4 PinoutDocument28 pagesAM4 PinoutMichael PefhanyNo ratings yet

- Switchgear PanelDocument28 pagesSwitchgear PanelDHIRENDER DWIVEDINo ratings yet

- Gasket NissanDocument40 pagesGasket NissanSalimka007No ratings yet

- ATI BRASIL - Catálogo GeralDocument198 pagesATI BRASIL - Catálogo GeralAlan FagundesNo ratings yet

- TAPSON TS600 SCHEMATICDocument1 pageTAPSON TS600 SCHEMATICABHISHEK VISHWAKARMANo ratings yet

- CF Balston Cross Ref ChartDocument4 pagesCF Balston Cross Ref ChartMartin Alonso Garcia GarciaNo ratings yet

- D42 31280S 001 DDR5 ECC SODIMM 4800 40 2048x8 16GB-3106960Document18 pagesD42 31280S 001 DDR5 ECC SODIMM 4800 40 2048x8 16GB-3106960ManunoghiNo ratings yet

- Micro - Lecture (CH 1)Document41 pagesMicro - Lecture (CH 1)Hamza MohammedNo ratings yet

- FRU (Field Replaceable Unit) ListDocument14 pagesFRU (Field Replaceable Unit) ListChelsea TeaNo ratings yet

- Mercedes Engine Module ListDocument238 pagesMercedes Engine Module ListFabio ZanardoNo ratings yet

- 7 Segment Display Interfacing With Arm7Document12 pages7 Segment Display Interfacing With Arm7Rahi SarkarNo ratings yet

- Amplificador Pioneer A8 SMDocument10 pagesAmplificador Pioneer A8 SMvideosonNo ratings yet

- 256 Kbit (32Kb X 8) UV EPROM and OTP EPROM: DescriptionDocument17 pages256 Kbit (32Kb X 8) UV EPROM and OTP EPROM: DescriptionRafaelNo ratings yet

- Iprog Can AdapterDocument1 pageIprog Can AdapterAndrésFelipeCevallos100% (1)

- JB - Rev2 PDFDocument1 pageJB - Rev2 PDFSreekanthMylavarapuNo ratings yet

- Diode Cross ReferenceDocument26 pagesDiode Cross ReferenceSGI AUTOMOTIVE PVT LTDNo ratings yet

- Reset: 20MHZ X1 15pF C1 15pF C2Document1 pageReset: 20MHZ X1 15pF C1 15pF C2Chiton AguirreNo ratings yet

- BOM - DNT Amp V2Document2 pagesBOM - DNT Amp V2Rolando QuezadaNo ratings yet

- Tableau D'équivalence NGKDocument2 pagesTableau D'équivalence NGKDaniel HaeberliNo ratings yet

- Loewe q2500 681Document15 pagesLoewe q2500 681Karim KalidiNo ratings yet

- Opel F-16 Gear ClassificationDocument3 pagesOpel F-16 Gear ClassificationAdnan MatiullahNo ratings yet

- Codigos de Diodos SMDDocument14 pagesCodigos de Diodos SMDJorge RuizNo ratings yet

- Spare Parts Manual Honda Engine gx120 Ut2 sm12Document24 pagesSpare Parts Manual Honda Engine gx120 Ut2 sm12Carlos HugoNo ratings yet

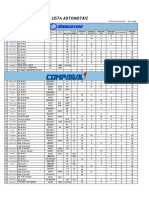

- Lista Automotriz Vendedores 07-11-2022Document2 pagesLista Automotriz Vendedores 07-11-2022yusbleidys rojas fuenmayorNo ratings yet

- Tabella Comparativa Delle Nomenclature ACCIAIDocument1 pageTabella Comparativa Delle Nomenclature ACCIAIZizuNo ratings yet

- Tabele Doboru Materiałów OERLIKONDocument3 pagesTabele Doboru Materiałów OERLIKONszystNo ratings yet

- Sharp 25ub1 - 25uf1Document11 pagesSharp 25ub1 - 25uf1winda rinaNo ratings yet

- ANYAGVÁLASZTÉKDocument1 pageANYAGVÁLASZTÉKPéter BorbásNo ratings yet

- Producto: AJ5 Nivel 4 Ref 1Document10 pagesProducto: AJ5 Nivel 4 Ref 1NataMoralesNo ratings yet

- Parts Guide: 1 EFT & RS232 Interface BoardDocument1 pageParts Guide: 1 EFT & RS232 Interface BoardmohammedNo ratings yet

- Tips GAMEBOYDocument7 pagesTips GAMEBOYRaphael JolonNo ratings yet

- GAGUT (Monitoring Mingguan Wig Session)Document22 pagesGAGUT (Monitoring Mingguan Wig Session)Gagut PurwantoNo ratings yet

- SolderingStation2 BOM v2.6Document2 pagesSolderingStation2 BOM v2.6Vu HaoNo ratings yet

- Partlist 5.1 Amplifier 12V Ta8221 With Spatializer - 2022-11-11Document1 pagePartlist 5.1 Amplifier 12V Ta8221 With Spatializer - 2022-11-11Taspen uddinNo ratings yet

- Stock Take Standart PartDocument3 pagesStock Take Standart PartEustachius Si W SeptiawanNo ratings yet

- Gti BHSDocument31 pagesGti BHSjk.venkateshNo ratings yet

- Pioneer VSX839RDS RecDocument32 pagesPioneer VSX839RDS Rec80quattroNo ratings yet

- BomDocument1 pageBomkikiNo ratings yet

- Ahu Technical Data Sheet: S.No Unit Tag Unit Model Capacity CFM Fanselection CFMDocument13 pagesAhu Technical Data Sheet: S.No Unit Tag Unit Model Capacity CFM Fanselection CFMShivam Jyoti SharmaNo ratings yet

- PananSonic Kv-s1025c Series - Kv-s1020c Series Scaner Service ManualDocument5 pagesPananSonic Kv-s1025c Series - Kv-s1020c Series Scaner Service ManualH.V KayaNo ratings yet

- Spec Traction Batterya (R1) - 1Document3 pagesSpec Traction Batterya (R1) - 1Hendi HendriansyahNo ratings yet

- Spare Parts List: Handheld Pneumatic Pick Hammers CP 0122 S H22, CP 0122 SL H22, CP 0125 S R25Document16 pagesSpare Parts List: Handheld Pneumatic Pick Hammers CP 0122 S H22, CP 0122 SL H22, CP 0125 S R25Ricardo VegaNo ratings yet

- Catálogo Frío 2017Document168 pagesCatálogo Frío 2017Alvaro Segura MoralesNo ratings yet

- DS1685 DS1687 PDFDocument34 pagesDS1685 DS1687 PDFJose HernandezNo ratings yet

- Guia de ProductoDocument15 pagesGuia de Productoalejandro lopezNo ratings yet

- B.TECH. III Yr. TIMETABLE ODD SEMESTER 2020 COMBINED, JIIT-128Document2 pagesB.TECH. III Yr. TIMETABLE ODD SEMESTER 2020 COMBINED, JIIT-128Abhijeet SinghNo ratings yet

- Recomendaciones XR 84W265811-18Document7 pagesRecomendaciones XR 84W265811-18Carlos GomezNo ratings yet

- 11S01 Black Tuesday (TrueType) PDFDocument1 page11S01 Black Tuesday (TrueType) PDFsamarxdasNo ratings yet

- All PDFDocument1 pageAll PDFsamarxdasNo ratings yet

- (A) Bench Terraces:: AdvantagesDocument1 page(A) Bench Terraces:: AdvantagessamarxdasNo ratings yet

- (A) Bench Terraces:: AdvantagesDocument4 pages(A) Bench Terraces:: AdvantagessamarxdasNo ratings yet

- Q. 1. Define The Administrative Responsibilities of Hazardous Waste Management ?Document3 pagesQ. 1. Define The Administrative Responsibilities of Hazardous Waste Management ?samarxdasNo ratings yet

- (A) Bench Terraces:: AdvantagesDocument7 pages(A) Bench Terraces:: AdvantagessamarxdasNo ratings yet

- Psedo CodeDocument7 pagesPsedo CodesamarxdasNo ratings yet

- Q.B. What Are The Role of Manager in Safety Management ?Document5 pagesQ.B. What Are The Role of Manager in Safety Management ?samarxdasNo ratings yet

- Construction ManagementDocument7 pagesConstruction ManagementsamarxdasNo ratings yet

- Barry White Smokey Robinson - Just To See HerDocument1 pageBarry White Smokey Robinson - Just To See HersamarxdasNo ratings yet

- Scheme Ibm Lenovo Thinkpad Sl400 Sl500Document94 pagesScheme Ibm Lenovo Thinkpad Sl400 Sl500Valentin GymNo ratings yet

- Caalogo Allen BradleyDocument27 pagesCaalogo Allen BradleyricardoqqNo ratings yet

- Processor Broadwell U: Ddr3LDocument44 pagesProcessor Broadwell U: Ddr3LYanto Sae50% (2)

- Ga z270x Ultra Gaming r102 SchematicDocument76 pagesGa z270x Ultra Gaming r102 Schematickhac Trinh VoNo ratings yet

- Revision History: Schematics IndexDocument15 pagesRevision History: Schematics IndexMark SorianoNo ratings yet

- Debug 1214Document17 pagesDebug 1214Ridwan HanafiNo ratings yet

- How To Fix DSDTDocument2 pagesHow To Fix DSDTbob bobbobNo ratings yet

- Zom e - I 315U: Heal TH Servi Ces Supporti NG Devi Ces SetDocument1 pageZom e - I 315U: Heal TH Servi Ces Supporti NG Devi Ces SetDano CuyNo ratings yet

- NM-A901 Yoga 910Document37 pagesNM-A901 Yoga 910Martin MarottaNo ratings yet

- FL1100Document67 pagesFL1100kindboomerNo ratings yet

- Ecs q67h2 Ad q65h2 Ad h67h2 AdDocument44 pagesEcs q67h2 Ad q65h2 Ad h67h2 AdDinuth DulsanduNo ratings yet

- 15CR Uma PV 1206Document58 pages15CR Uma PV 1206PaxOtiumNo ratings yet

- B450-A Pro MS-7B86 Rev2.0Document63 pagesB450-A Pro MS-7B86 Rev2.0tecnicomicroNo ratings yet

- Lenovo-Thinkpad-Sl400 Pegatron Rocky40 50 Uma Rev1-0-Pdf.41793Document94 pagesLenovo-Thinkpad-Sl400 Pegatron Rocky40 50 Uma Rev1-0-Pdf.41793mbah bejoNo ratings yet

- CHINA TV With TDA9373 (N501), TDA7057 (N602), TDA8356 or TDA8351 (N301)Document1 pageCHINA TV With TDA9373 (N501), TDA7057 (N602), TDA8356 or TDA8351 (N301)pepino46450% (2)

- OBS!!! Arduino UNO Is 5 V: USB Filtering Power Managemnet DAC I2C BufferDocument1 pageOBS!!! Arduino UNO Is 5 V: USB Filtering Power Managemnet DAC I2C BufferNishant BatraNo ratings yet

- Debug 1214Document4 pagesDebug 1214zavajackzNo ratings yet

- GR 10 ICT Unit 02 NP TamilDocument6 pagesGR 10 ICT Unit 02 NP Tamilthusi manchuNo ratings yet

- DP CardReader 15054 DriversDocument962 pagesDP CardReader 15054 DriversNoriel MillaresNo ratings yet

- Ga A55m DS2Document27 pagesGa A55m DS2Minh Nguyen PhuNo ratings yet

- Griffe G4-PGN513 DiagramDocument16 pagesGriffe G4-PGN513 DiagramncirNo ratings yet

- Acer Aspire V5-551G 1 Quanta ZRP - RevA1ADocument44 pagesAcer Aspire V5-551G 1 Quanta ZRP - RevA1ATom ArcillaNo ratings yet

- Z490 Ud Ac Rev1.01Document63 pagesZ490 Ud Ac Rev1.01marcNo ratings yet

- Debug 1214Document3 pagesDebug 1214Moh Ali MNo ratings yet

- GA H61M DS2 Rev. 3.0Document30 pagesGA H61M DS2 Rev. 3.0RohimNo ratings yet

- MS-16332 R0aDocument41 pagesMS-16332 R0aRisoSilvaNo ratings yet

- Stm32 Usb C PD Solutions PresentationDocument34 pagesStm32 Usb C PD Solutions Presentationnisaken634No ratings yet

- Acer Spin 3 SP314-51 Wistron Slinky 17893-1 Rev - 1Document106 pagesAcer Spin 3 SP314-51 Wistron Slinky 17893-1 Rev - 1KaterineCespedesBacarrezaNo ratings yet

- NM B601 YOGA530 - 530S - SVT - Lenovo IdeaPad 530S-15IKBDocument60 pagesNM B601 YOGA530 - 530S - SVT - Lenovo IdeaPad 530S-15IKBCarlosNo ratings yet

- Merlin Gerin, Telemecanique, SquareD - Cyberall GroupDocument334 pagesMerlin Gerin, Telemecanique, SquareD - Cyberall Groupernesto floresNo ratings yet