Professional Documents

Culture Documents

Noc18 cs54 Assignment9

Noc18 cs54 Assignment9

Uploaded by

hitech.sanjay7610Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Noc18 cs54 Assignment9

Noc18 cs54 Assignment9

Uploaded by

hitech.sanjay7610Copyright:

Available Formats

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

reviewer3@nptel.iitm.ac.in ▼

Courses » Embedded Systems-- Design Verification and Test

Announcements Course Ask a Question Progress Mentor FAQ

Unit 9 - Introduction to

Digital Testing

Course outline Assignment-8

How to access the The due date for submitting this assignment has passed. Due on 2018-09-26, 23:59 IST.

portal As per our records you have not submitted this assignment.

Introduction and 1) Murphy’s Law states that _______ 1 point

Modeling

If anything can go wrong, it will

Modeling and

If nothing goes wrong, it will

Synthesis issues

If anything can go wrong, it will not

Architectural

Synthesis of If nothing goes wrong, it will not

Hardwares

No, the answer is incorrect.

Score: 0

System-level Design

Accepted Answers:

Temporal Logic If anything can go wrong, it will

2) Figure below illustrates the process of Embedded Systems Design and Test flow. What is the block marked 1 point

Model Checking

“1” in the figure?

BDD and Symbolic

Model Checking

Introduction to

Digital Testing

Introduction to

Digital VLSI Testing

Automatic Test

Pattern Generation

(ATPG)

Quiz :

Assignment-8

Embedded System

Hardware Testing

Embedded System

Hardware Testing - II

Test Response storage

Advances in Integration

Embedded System

Hardware Testing Test Response compressor

Copy of Manufactured circuit under test

Advances in

Embedded System No, the answer is incorrect.

Hardware Testing - II Score: 0

Accepted Answers:

© 2014 NPTEL - Privacy & Terms - Honor Code - FAQs -

A project of In association with Funded by

Powered by

1 of 6 Friday 09 November 2018 07:06 AM

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

Data flow-based testing

None

No, the answer is incorrect.

Score: 0

Accepted Answers:

Design for testability

4) Figure below illustrates a process of ____ circuit testing. 1 point

Digital

Analog

Both of the above

None of the above

No, the answer is incorrect.

Score: 0

Accepted Answers:

Digital

5) For an n-input circuit, ____ test patterns are needed for functional testing. 1 point

2n

n2

2n

No, the answer is incorrect.

Score: 0

Accepted Answers:

2n

6) A circuit with n nets can have ___ possible stuck-at faults under single stuck-at fault model. 1 point

2n

n2

infinite

2n

No, the answer is incorrect.

Score: 0

Accepted Answers:

2n

7) How many test patterns are needed to test the circuit given in the figure below? Assume that structural 0 points

testing with single stuck at fault model is used.

2 of 6 Friday 09 November 2018 07:06 AM

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

25

60

192

160

No, the answer is incorrect.

Score: 0

Accepted Answers:

192

8) Functional and structural testing of the 32-Bit adder circuit shown below needs ____ and ____ test patterns, 1 point

respectively.

265, 23

2 * 65, 23

265, 2 * 3

65, 3

No, the answer is incorrect.

Score: 0

Accepted Answers:

265, 23

9) How many stuck-at faults are possible in the AND-gate shown below? 1 point

3 of 6 Friday 09 November 2018 07:06 AM

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

12

11

10

No, the answer is incorrect.

Score: 0

Accepted Answers:

12

10)A net having fan-out to k gates will have ___ stuck at fault locations 1 point

k+1

k-1

2k

None

No, the answer is incorrect.

Score: 0

Accepted Answers:

k+1

11)Which of the following statement is generally valid for a circuit? 1 point

All faults are “easy to test”

All faults are “difficult to test”

Few faults are “easy to test” and most others are “difficult to test”

Most faults are “easy to test” and few are “difficult to test”

No, the answer is incorrect.

Score: 0

Accepted Answers:

Most faults are “easy to test” and few are “difficult to test”

12)The test patterns for “easy to test faults” are derived by ____ 1 point

Fault simulation algorithms

Sensitization–propagation -justification approach

Boolean Difference approach

All the above

No, the answer is incorrect.

Score: 0

Accepted Answers:

Fault simulation algorithms

13)The test patterns for “difficult to test faults” are derived by ____ 1 point

Fault simulation algorithms

Sensitization–propagation -justification approach

both (a) and (b)

other than the above

4 of 6 Friday 09 November 2018 07:06 AM

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

No, the answer is incorrect.

Score: 0

Accepted Answers:

Sensitization–propagation -justification approach

14)Let us consider a 2-input AND gates shown in figure below where the inputs are marked using notations 1 point

from Roth’s 5-valued algebra. What is the output notation at the ? marked net i.e., output of gate G1?

No, the answer is incorrect.

Score: 0

Accepted Answers:

D

15)Consider figure of Question 14. What is the output notation at the ? marked net i.e., output of gate G2? 1 point

D̅

D

No, the answer is incorrect.

Score: 0

Accepted Answers:

D̅

16)Consider figure of Question 14. What is the output notation at the ? marked net i.e., output of gate G3? 1 point

No, the answer is incorrect.

Score: 0

Accepted Answers:

X

17)If one wants to take the path “e-f-g-h” in the figure below for propagating the fault effect to the output h. The 1 point

signals labelled as 1, 2, 3 in the nets of the path are assigned in terms of Roth’s 5 valued algebra. The signal value of the

net labelled with 1 is _____.

5 of 6 Friday 09 November 2018 07:06 AM

Embedded Systems-- Design Verification and Tes... https://onlinecourses.nptel.ac.in/noc18_cs54/uni...

No, the answer is incorrect.

Score: 0

Accepted Answers:

D

Previous Page End

6 of 6 Friday 09 November 2018 07:06 AM

You might also like

- Barefoot MicroMain35 Manual-Rev5Document7 pagesBarefoot MicroMain35 Manual-Rev5César WerlonNo ratings yet

- OME753 Systems Engineering MCQ - NPTELDocument23 pagesOME753 Systems Engineering MCQ - NPTELsebampitako duncanNo ratings yet

- Mindell: Automation's Finest Hour. Bell Labs and Automatic Control in wwIIDocument8 pagesMindell: Automation's Finest Hour. Bell Labs and Automatic Control in wwIIwatevaid100% (1)

- Unit 13 - Fault Simulation and Testability Measures: Week 10 AssignmentDocument6 pagesUnit 13 - Fault Simulation and Testability Measures: Week 10 AssignmentDeepak TiwariNo ratings yet

- Unit 1 - How To Access The Portal: Announcements Ask A Question Progress Mentor FAQDocument4 pagesUnit 1 - How To Access The Portal: Announcements Ask A Question Progress Mentor FAQNeeraj IdnaniNo ratings yet

- Unit 14 - Combinational Circuit Test Pattern Generation: Week 11 AssignmentDocument7 pagesUnit 14 - Combinational Circuit Test Pattern Generation: Week 11 AssignmentDeepak TiwariNo ratings yet

- Model Question M.SC - IT - Part I Paper I Computer Simulations and Modelling and Programme With Component MCQDocument28 pagesModel Question M.SC - IT - Part I Paper I Computer Simulations and Modelling and Programme With Component MCQSikandar SayyedNo ratings yet

- Unit 3 - Week 1: Assignment 1Document3 pagesUnit 3 - Week 1: Assignment 1Arun UpadhyayNo ratings yet

- Fundamentals of Additive Manufacturing Technologies - Unit 6 - Week 4 - Liquid Additive ManufacturingDocument2 pagesFundamentals of Additive Manufacturing Technologies - Unit 6 - Week 4 - Liquid Additive ManufacturingSaurav KumarNo ratings yet

- Unit 4 - Week 3: Assignment 3Document3 pagesUnit 4 - Week 3: Assignment 3Dr.T. Pridhar ThiagarajanNo ratings yet

- Fundamentals of Additive Manufacturing Technologies - Unit 3 - Week 1 - Introduction To Additive ManufacturingDocument2 pagesFundamentals of Additive Manufacturing Technologies - Unit 3 - Week 1 - Introduction To Additive ManufacturingSaurav KumarNo ratings yet

- Unit 1 - How To Access The Portal: Assignment-0Document3 pagesUnit 1 - How To Access The Portal: Assignment-0Aparna KambleNo ratings yet

- Fundamentals of Additive Manufacturing Technologies - Unit 5 - Week 3 - Computer Aided Process Planning For Additive ManufacturingDocument2 pagesFundamentals of Additive Manufacturing Technologies - Unit 5 - Week 3 - Computer Aided Process Planning For Additive ManufacturingSaurav KumarNo ratings yet

- W7 PaymentDocument4 pagesW7 Paymentsanjay.diddeeNo ratings yet

- Quiz Apdd1Document3 pagesQuiz Apdd1YASHVANTH UDAYAKUMARNo ratings yet

- NPTEL AssignmentDocument38 pagesNPTEL AssignmentGopal KumarNo ratings yet

- Unit 3 - Week 1: Assignment 1Document3 pagesUnit 3 - Week 1: Assignment 1NibeditNahakNo ratings yet

- Unit 6 - Week 5Document4 pagesUnit 6 - Week 5sanjay.diddeeNo ratings yet

- Unit 11 - Week 10Document4 pagesUnit 11 - Week 10sanjay.diddeeNo ratings yet

- Unit 11 - Week 10 - Principles of Pipelining: Assignment 10Document3 pagesUnit 11 - Week 10 - Principles of Pipelining: Assignment 10Rahi SarkarNo ratings yet

- Unit 2 - Week 1: Assignment 1Document3 pagesUnit 2 - Week 1: Assignment 1Raushan KashyapNo ratings yet

- W2A1Document3 pagesW2A1venkatachalapathy.thNo ratings yet

- Fundamentals of Additive Manufacturing Technologies - Unit 7 - Week 5 - Liquid Additive ManufacturingDocument2 pagesFundamentals of Additive Manufacturing Technologies - Unit 7 - Week 5 - Liquid Additive ManufacturingSaurav KumarNo ratings yet

- Assignment-7 Noc18 mg39 78Document4 pagesAssignment-7 Noc18 mg39 78Suman AgarwalNo ratings yet

- Unit 6 - Week 5: Assignment 5Document4 pagesUnit 6 - Week 5: Assignment 5shubhamNo ratings yet

- Noc20-Cs28 Week 07 Assignment 02Document6 pagesNoc20-Cs28 Week 07 Assignment 02Praveen Urs RNo ratings yet

- Unit 15 - Week 11: Assignment 11Document4 pagesUnit 15 - Week 11: Assignment 11Debraj ChatterjeeNo ratings yet

- Quiz 3Document3 pagesQuiz 3rishi tejuNo ratings yet

- Unit 2 - Week 1Document3 pagesUnit 2 - Week 1Gayle LokeshNo ratings yet

- Unit 8 - Fragments: Mid-Sem ExamDocument11 pagesUnit 8 - Fragments: Mid-Sem ExamS.Gangaram gangaramNo ratings yet

- Assignment-1 Noc18 Ee38 7Document4 pagesAssignment-1 Noc18 Ee38 7Gaurav PatilNo ratings yet

- 6 PDFDocument3 pages6 PDFksai.mbNo ratings yet

- Unit 9 - Week 8: Assignment - 8Document5 pagesUnit 9 - Week 8: Assignment - 8xperiaashNo ratings yet

- NptelDocument3 pagesNptelChaitanya CherryNo ratings yet

- Ad Hoc and Wireless Sensor Networks MCQDocument24 pagesAd Hoc and Wireless Sensor Networks MCQkingraajaNo ratings yet

- Unit 9 - Week 8: R1 - W8 - Assignment-8Document5 pagesUnit 9 - Week 8: R1 - W8 - Assignment-8AbhishekNo ratings yet

- Unit 2 - Introduction To Iots - Improving Quality of Life: Week1 AssessmentDocument30 pagesUnit 2 - Introduction To Iots - Improving Quality of Life: Week1 AssessmentPraghashrajaNo ratings yet

- Nptel QS Bank WSNDocument94 pagesNptel QS Bank WSNKirankumar PotnuruNo ratings yet

- Nptel How To AccessDocument39 pagesNptel How To AccessMR NÔÔBNo ratings yet

- Unit 7 - Physical Design: Week 4 AssignmentDocument3 pagesUnit 7 - Physical Design: Week 4 AssignmentpankajmudgilNo ratings yet

- Unit 1 - How To Access The Portal & Assignment - 00Document4 pagesUnit 1 - How To Access The Portal & Assignment - 00MR. DEVASHISH GAUTAMNo ratings yet

- Assignment 3Document5 pagesAssignment 3Rahi SarkarNo ratings yet

- Unit 5 - Week 3: Assignment 3Document5 pagesUnit 5 - Week 3: Assignment 3Mohit SharmaNo ratings yet

- Noc18 bt22 Assignment3Document5 pagesNoc18 bt22 Assignment3Debraj ChatterjeeNo ratings yet

- Noc18 mg42 Assignment9Document6 pagesNoc18 mg42 Assignment9GangadharNo ratings yet

- Computer Engineering As A Discipline Midterm Quiz 2Document6 pagesComputer Engineering As A Discipline Midterm Quiz 2marieNo ratings yet

- Unit 2 - Week 1: Assignment-1Document6 pagesUnit 2 - Week 1: Assignment-1suneethaNo ratings yet

- Unit 10 - Week 9: Assignment 9Document3 pagesUnit 10 - Week 9: Assignment 9jonNo ratings yet

- Unit 2 - Week 1Document396 pagesUnit 2 - Week 1sanskritiagarwal2022No ratings yet

- EC8702 Ad Hoc and Wireless Sensor Networks MCQDocument24 pagesEC8702 Ad Hoc and Wireless Sensor Networks MCQthirsh ragav100% (2)

- Art of C Programming - Unit 2 - Week 02Document3 pagesArt of C Programming - Unit 2 - Week 02Vikas DeshmukhNo ratings yet

- Unit 2 - Week 1: Assignment 1Document3 pagesUnit 2 - Week 1: Assignment 1jonNo ratings yet

- Noc19 cs04 Assignment5Document4 pagesNoc19 cs04 Assignment5Smart BoyNo ratings yet

- Test Your Understanding (Copy) : Attempt ReviewDocument4 pagesTest Your Understanding (Copy) : Attempt ReviewNikhil SahlotNo ratings yet

- Noc19-Cs72 Assignment Week 08Document4 pagesNoc19-Cs72 Assignment Week 08endriasmit_469556062No ratings yet

- Unit 9 - Week 8: Assignment 8Document4 pagesUnit 9 - Week 8: Assignment 8VibhaNo ratings yet

- Unit 9 - Week 8: Assignment 8Document4 pagesUnit 9 - Week 8: Assignment 8axar kumarNo ratings yet

- Unit 9 - Week 8: Assignment 8Document4 pagesUnit 9 - Week 8: Assignment 8VibhaNo ratings yet

- Unit 7 - Week 5: Assessment 5Document3 pagesUnit 7 - Week 5: Assessment 5skarthikpriyaNo ratings yet

- Dashboard Software Engineering Concepts Software Engineering Fundamentals Post-QuizDocument2 pagesDashboard Software Engineering Concepts Software Engineering Fundamentals Post-QuizPrakash Hegde100% (3)

- Smart Shopping Trolley Document PDFDocument3 pagesSmart Shopping Trolley Document PDFHarshavardhan SJNo ratings yet

- Tilting Assembly Gantry Stationary Base AssemblyDocument1 pageTilting Assembly Gantry Stationary Base AssemblyKMC BIOMEDICALNo ratings yet

- CSS 1st QuarterDocument4 pagesCSS 1st QuarterBarbie BeltranNo ratings yet

- Abb Acs800 01 U1 ManualDocument159 pagesAbb Acs800 01 U1 ManualsunhuynhNo ratings yet

- DC (Direct-Coupled) AmplifiersDocument20 pagesDC (Direct-Coupled) AmplifiersDevi Taufiq NurrohmanNo ratings yet

- DESINA Installation TechnologyDocument8 pagesDESINA Installation TechnologymansourNo ratings yet

- LEVEL I - ATA 23 CommunicationsDocument50 pagesLEVEL I - ATA 23 Communicationswagdi100% (1)

- Ns500ne 7115 PDFDocument191 pagesNs500ne 7115 PDFDejan PetrovicNo ratings yet

- Wi Fi SeetingsDocument84 pagesWi Fi SeetingsAndrew NkhuwaNo ratings yet

- LP2 PracticeDocument9 pagesLP2 PracticeJUAN PABLO MARTINEZ VARGASNo ratings yet

- Forward Error Correction - WikipediaDocument54 pagesForward Error Correction - WikipediapunithNo ratings yet

- MP 7503 Guia de SoporteDocument47 pagesMP 7503 Guia de SoporteSamuelDelgadoR.No ratings yet

- 133R0228 HLP-SK180 Series English Operating Manual V2013-04Document147 pages133R0228 HLP-SK180 Series English Operating Manual V2013-04salesiano05No ratings yet

- OptiX WDM Product System Commissioning-V1.0Document41 pagesOptiX WDM Product System Commissioning-V1.0Elfatih HashimNo ratings yet

- N133bge L31Document32 pagesN133bge L31Facundo MeierNo ratings yet

- Preliminary MaterialDocument8 pagesPreliminary Materialzbc zbc1234568No ratings yet

- Training - RTS IntercomDocument20 pagesTraining - RTS IntercommenalejaNo ratings yet

- UEE001 SyllabusDocument2 pagesUEE001 SyllabusashNo ratings yet

- Cam Module 5 RomDocument28 pagesCam Module 5 Romnamitha rNo ratings yet

- Navic + Gagan / Gps SMD Receiver Module: FeaturesDocument20 pagesNavic + Gagan / Gps SMD Receiver Module: Featuresramesh chivukulaNo ratings yet

- PYQ Phase Controlled RectifiersDocument32 pagesPYQ Phase Controlled Rectifiers14 Asif AkhtarNo ratings yet

- TC7660H High Frequency 7660 Dc-To-Dc Voltage Converter: Features General DescriptionDocument8 pagesTC7660H High Frequency 7660 Dc-To-Dc Voltage Converter: Features General Descriptionhanh_12No ratings yet

- Technical Comparison of Harmonic Mitigation PDFDocument9 pagesTechnical Comparison of Harmonic Mitigation PDFGurmeet SinghNo ratings yet

- Parametric Excitation Model For Waveguide Piano Synthesis PDFDocument4 pagesParametric Excitation Model For Waveguide Piano Synthesis PDFChoo Chee WeeNo ratings yet

- Transformers Ficha TecnicaDocument9 pagesTransformers Ficha TecnicaNelsonLeonNo ratings yet

- Configured Command CenterDocument5 pagesConfigured Command Centereng_eidsamyNo ratings yet

- KCMS 8Document6 pagesKCMS 8Dennis Ong JuniorNo ratings yet

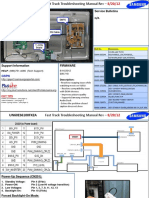

- Samsung UN60ES6100FXZA Fast TrackDocument4 pagesSamsung UN60ES6100FXZA Fast TrackAndreyNo ratings yet