Professional Documents

Culture Documents

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

Uploaded by

Abhishek PareekCopyright:

Available Formats

You might also like

- Mad in AmericaDocument13 pagesMad in AmericaSadia AshrafNo ratings yet

- Test Bank For Essentials of Health Information Management 4th Edition by BowieDocument12 pagesTest Bank For Essentials of Health Information Management 4th Edition by Bowiebevisphuonglc1u5No ratings yet

- Man d0834 d0836 Spec Sheet p1jpgDocument6 pagesMan d0834 d0836 Spec Sheet p1jpgFERNANDO FERRUSCA100% (2)

- ALL P-Cube QuestionsDocument10 pagesALL P-Cube QuestionsNicole NgNo ratings yet

- OBGYN and Infertility Handbook For CliniciansDocument237 pagesOBGYN and Infertility Handbook For CliniciansAmal Farah100% (2)

- Library Management SystemDocument58 pagesLibrary Management SystemPurushottam Choudhary100% (9)

- Digital To Analog Converters - TutorialspointDocument5 pagesDigital To Analog Converters - Tutorialspointdiether.gozumNo ratings yet

- Installation Instructions: EnglishDocument22 pagesInstallation Instructions: EnglishSandorGyorfiNo ratings yet

- Analog Crash Course Workbook GaDocument54 pagesAnalog Crash Course Workbook GaAbhishek RajNo ratings yet

- Ece 374 Part 7 Mosfet 3Document14 pagesEce 374 Part 7 Mosfet 3Zakaria ElwalilyNo ratings yet

- Multiplexer CheviDocument1 pageMultiplexer CheviDollyNo ratings yet

- Multilevel Inverter With Reducing Device Count:: Project Batch-15Document20 pagesMultilevel Inverter With Reducing Device Count:: Project Batch-15madhu madhaviNo ratings yet

- Home-Constructed, Building Block Op-Amp Circuits For Analog Computers Inverting IntegratorDocument5 pagesHome-Constructed, Building Block Op-Amp Circuits For Analog Computers Inverting IntegratorMsuttonNo ratings yet

- ECEN 325 Lab 4: Operational Amplifiers - Part IIDocument4 pagesECEN 325 Lab 4: Operational Amplifiers - Part IISam AlbaNo ratings yet

- Product Datasheet: Flyback Transformer - Ef20Document1 pageProduct Datasheet: Flyback Transformer - Ef20ingucvNo ratings yet

- Eng 86799Document2 pagesEng 86799Prasad RampalliNo ratings yet

- Polytechnic University of Puerto Rico Mechanical Engineering Department Mechatronics ME-5250 Professor: Sandra L. OrdóñezDocument15 pagesPolytechnic University of Puerto Rico Mechanical Engineering Department Mechatronics ME-5250 Professor: Sandra L. OrdóñezGabriel PachecoNo ratings yet

- Redwan Ahmed Miazee - HW - 1Document3 pagesRedwan Ahmed Miazee - HW - 1REDWAN AHMED MIAZEENo ratings yet

- Diode Clipper CircuitsDocument13 pagesDiode Clipper Circuitsmajdzmm12No ratings yet

- Ao6401 HF - Ko6401 HFDocument4 pagesAo6401 HF - Ko6401 HFsuan kwang TanNo ratings yet

- 2SB649AM Series: Bipolar General Purpose PNP Power Transistor - 1.5A / - 120V, - 160V / 20WDocument4 pages2SB649AM Series: Bipolar General Purpose PNP Power Transistor - 1.5A / - 120V, - 160V / 20WFreddy CamposNo ratings yet

- Lecture (Diode As Clamper)Document2 pagesLecture (Diode As Clamper)Sheikh HarisNo ratings yet

- PV+ PV-S COM Input Side Output Side: Voltage Detection CircuitDocument1 pagePV+ PV-S COM Input Side Output Side: Voltage Detection CircuitRamiro BraccoNo ratings yet

- RD07MVS1: Silicon RF Power MOS FET (Document10 pagesRD07MVS1: Silicon RF Power MOS FET (RickyNSNo ratings yet

- Surface-Mount 4-Circuit Low-Side Switch Array SPF5002: External Dimensions FeaturesDocument1 pageSurface-Mount 4-Circuit Low-Side Switch Array SPF5002: External Dimensions Featureskatty cumbeNo ratings yet

- Virtual LabsDocument1 pageVirtual LabsSai GanthodNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Nec Tokin PDFDocument2 pagesNec Tokin PDFAntero RafaelNo ratings yet

- Polka 10Document4 pagesPolka 10Francesc MasanaNo ratings yet

- Work3 2Document1 pageWork3 2Bas BasNo ratings yet

- Degree Electronic Engineeringe First Semester EXAMINATIONS 2020/2021Document3 pagesDegree Electronic Engineeringe First Semester EXAMINATIONS 2020/2021Peter JumreNo ratings yet

- Schematic LLM393Document1 pageSchematic LLM393Channa PrasadNo ratings yet

- Ds Ah 00658800Document2 pagesDs Ah 00658800acorkeryuNo ratings yet

- Animasi Dioda Dan Power SupllyDocument25 pagesAnimasi Dioda Dan Power SupllyPA videoNo ratings yet

- DC DC ConvertersDocument22 pagesDC DC ConvertersAnonymous UJs2uePNo ratings yet

- Advanced Electronics: Wave Shaping & Generating CircuitsDocument19 pagesAdvanced Electronics: Wave Shaping & Generating CircuitsGelvie LagosNo ratings yet

- A350 Hyd PDFDocument16 pagesA350 Hyd PDFSaleh El DalyNo ratings yet

- MULTIPLEXERDocument1 pageMULTIPLEXERShraavani TopleNo ratings yet

- Two Watt Meter Method: Voff 0 FREQ 50 VAMPL 311 Voff 0Document7 pagesTwo Watt Meter Method: Voff 0 FREQ 50 VAMPL 311 Voff 0Kornkanok PMNo ratings yet

- FinalExam ENM061 2021 04 07Document3 pagesFinalExam ENM061 2021 04 07Kostas GekasNo ratings yet

- DC Circuits: Fundamentals of Electric CircuitsDocument34 pagesDC Circuits: Fundamentals of Electric CircuitsHoàng HoàngAnhNo ratings yet

- Diagram Wiring RS 485: Power Supply Ke EvcDocument1 pageDiagram Wiring RS 485: Power Supply Ke EvcDatabase PalembangNo ratings yet

- 11.types of DiodesDocument13 pages11.types of DiodesAmmar HussamNo ratings yet

- Avh-13n-M1 (New Design) 2101Document2 pagesAvh-13n-M1 (New Design) 2101arihantidsNo ratings yet

- Exp 5 Zener Diode Characteristics and ApplicationsDocument4 pagesExp 5 Zener Diode Characteristics and ApplicationsGowsic PmNo ratings yet

- DA Converters: DigitalelectronicsiicourseDocument24 pagesDA Converters: DigitalelectronicsiicourseLeonardo Franzua Giraldo CardosoNo ratings yet

- Controller Design For BLDC MotorDocument15 pagesController Design For BLDC MotorAnonymous SdIsxrNo ratings yet

- BEE Lab For Ist YearsDocument32 pagesBEE Lab For Ist YearsMutya BalaNo ratings yet

- Enabele: New Project - PDSPRJ 12/19/2021 New Project - PDSPRJDocument1 pageEnabele: New Project - PDSPRJ 12/19/2021 New Project - PDSPRJ29Nyoman Danu Tri DamartaNo ratings yet

- Chapter 11 Part IDocument39 pagesChapter 11 Part Imstan11No ratings yet

- An 9723Document2 pagesAn 9723Stacy Mcclain100% (1)

- MultiplexerDocument1 pageMultiplexerMyra Ali KhanNo ratings yet

- Assignment 1 - Analog CircuitDocument1 pageAssignment 1 - Analog CircuitSV MNo ratings yet

- Power Electronics For RenewablesDocument22 pagesPower Electronics For RenewablesShiv Prakash M.Tech., Electrical Engineering, IIT(BHU)No ratings yet

- Small Signal Model AC AC IHDocument1 pageSmall Signal Model AC AC IHruanNo ratings yet

- Low-Side Switch Ics Spf5002A: (Surface-Mount 4-Circuits)Document2 pagesLow-Side Switch Ics Spf5002A: (Surface-Mount 4-Circuits)nurwi dikaNo ratings yet

- Circuit Analysis and Electronics Laboratory Calvin College: 22 April 2010Document11 pagesCircuit Analysis and Electronics Laboratory Calvin College: 22 April 2010beb5No ratings yet

- Diode Circuits ProblemDocument11 pagesDiode Circuits Problemsamantaramen86No ratings yet

- Slides of Lecture4Document34 pagesSlides of Lecture4rudra patraNo ratings yet

- Transformer: 5 AmpsDocument9 pagesTransformer: 5 AmpsMohammed Qaid AlathwaryNo ratings yet

- Digital Communication Systems First Edit - PDF 1Document3 pagesDigital Communication Systems First Edit - PDF 1Rakesh. N murthyNo ratings yet

- BEE Lab Manual - 2019 PDFDocument47 pagesBEE Lab Manual - 2019 PDFAdal ArasuNo ratings yet

- Flyback Converter Daniel W. HartDocument11 pagesFlyback Converter Daniel W. HartABHISHEK SHAWNo ratings yet

- Exp2.Study of RC Triggering CircuitDocument3 pagesExp2.Study of RC Triggering CircuitAbdullah MohammedNo ratings yet

- Auto Transformer: Auto Transformer Is Kind of Electrical Transformer Where Primary and Secondary Shares SameDocument8 pagesAuto Transformer: Auto Transformer Is Kind of Electrical Transformer Where Primary and Secondary Shares SameAbhishek PareekNo ratings yet

- Finite Automata 04 _ Class NotesDocument83 pagesFinite Automata 04 _ Class NotesAbhishek PareekNo ratings yet

- Star Delta Transformation: Wle 204 Circuit Theory Unit 2 Elementary Network AnalysisDocument14 pagesStar Delta Transformation: Wle 204 Circuit Theory Unit 2 Elementary Network AnalysisAbhishek PareekNo ratings yet

- My NameDocument2 pagesMy NameAbhishek PareekNo ratings yet

- Time DomainDocument3 pagesTime DomainAbhishek PareekNo ratings yet

- Frequency Domain - WikipediaDocument6 pagesFrequency Domain - WikipediaAbhishek PareekNo ratings yet

- Nuc Kit D34010wyk Product BriefDocument4 pagesNuc Kit D34010wyk Product BriefAbhishek PareekNo ratings yet

- Malaviya National Institute of Technology Jaipur: J. L. N. Marg, Malaviya Nagar, Jaipur-302017 (Rajasthan)Document8 pagesMalaviya National Institute of Technology Jaipur: J. L. N. Marg, Malaviya Nagar, Jaipur-302017 (Rajasthan)Abhishek PareekNo ratings yet

- VITEEE2020 EnglishandAptitudeDocument1 pageVITEEE2020 EnglishandAptitudeAbhishek PareekNo ratings yet

- Nuc Kit D34010wyk Product BriefDocument4 pagesNuc Kit D34010wyk Product BriefAbhishek PareekNo ratings yet

- Elec - Magnetism Course OutlineDocument4 pagesElec - Magnetism Course OutlineBernard PanganibanNo ratings yet

- Guru 1 - 5 Whats NewDocument19 pagesGuru 1 - 5 Whats NewLuca RosacutaNo ratings yet

- Egypt: Gec08-Science, Technology & Society Modern AgesDocument7 pagesEgypt: Gec08-Science, Technology & Society Modern AgesNo NameNo ratings yet

- OpenCV by Example - Sample ChapterDocument25 pagesOpenCV by Example - Sample ChapterPackt PublishingNo ratings yet

- SOCIOLOGICAL FOUNDATION ReportDocument14 pagesSOCIOLOGICAL FOUNDATION Reportᜃᜒᜈ᜔ᜎᜒ ᜇᜒᜋᜈ᜔ᜇᜒᜋᜈ᜔No ratings yet

- LAS 1A The Magic PomegranateDocument2 pagesLAS 1A The Magic PomegranateCherry Maravilla Basa MingoaNo ratings yet

- Crompton Instruments Integra Ci3: Digital Metering SystemDocument4 pagesCrompton Instruments Integra Ci3: Digital Metering SystemAmit BhatiaNo ratings yet

- Prevalence of Interpersonal Violence Against Athletes in The Sport Context (2017)Document5 pagesPrevalence of Interpersonal Violence Against Athletes in The Sport Context (2017)Juan Kmilo Martinez FernandezNo ratings yet

- OS Manual Oretronic III Rec4105LDocument152 pagesOS Manual Oretronic III Rec4105LJose ReedNo ratings yet

- Wtt12L-B2562: PowerproxDocument7 pagesWtt12L-B2562: PowerproxJCNo ratings yet

- Department of Education: A. Background Information For Learners B. Most Essential Learning CompetencyDocument9 pagesDepartment of Education: A. Background Information For Learners B. Most Essential Learning CompetencyCamille CaigaNo ratings yet

- AFI - 10-248 - Fitness ProgramDocument89 pagesAFI - 10-248 - Fitness ProgramDongelxNo ratings yet

- PSM SeminarDocument33 pagesPSM SeminarSamarth JainNo ratings yet

- Module 1 PDFDocument18 pagesModule 1 PDFYashaswiniNo ratings yet

- Influence of Ni On Martensitic Phase Transformations in NiTi Shape Memory Alloys 2010 Acta MaterialiaDocument15 pagesInfluence of Ni On Martensitic Phase Transformations in NiTi Shape Memory Alloys 2010 Acta MaterialiaJhonk FigueroaNo ratings yet

- Event Proposal FullDocument4 pagesEvent Proposal FullDarren Kate LicupaNo ratings yet

- Infectious Diseases 2022 Virtual Abstract BookDocument53 pagesInfectious Diseases 2022 Virtual Abstract BookSriNo ratings yet

- Mco 2 3 337 PDF PDFDocument4 pagesMco 2 3 337 PDF PDFhendra ardiantoNo ratings yet

- Luxacore IndicationDocument10 pagesLuxacore IndicationAnonymous UT3s7CNo ratings yet

- Fundmentals Energy ProcessDocument11 pagesFundmentals Energy ProcessepjxNo ratings yet

- 2595 0118 BRJP 02 03 0255Document5 pages2595 0118 BRJP 02 03 0255tariNo ratings yet

- Hearst Demystifying Media Fireside Chat - The Bloomberg Way With Matthew WinklerDocument16 pagesHearst Demystifying Media Fireside Chat - The Bloomberg Way With Matthew WinklerDemystifying MediaNo ratings yet

- Biological Conservation: Policy AnalysisDocument8 pagesBiological Conservation: Policy AnalysisEmilio Lecaros BustamanteNo ratings yet

- Why We Are Shallow by F. Sionil JoseDocument3 pagesWhy We Are Shallow by F. Sionil JosePrecy M AgatonNo ratings yet

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

Uploaded by

Abhishek PareekOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

13 DAC & CMOS Implementation of Logics - DPP-13 (Lec-14)

Uploaded by

Abhishek PareekCopyright:

Available Formats

1

EE/EC/CS & IT/IN CRASH COURSE-2023

Digital Electronics

DAC & CMOS Implementation of Logics DPP-13

1. Which of the following is FALSE for a CMOS 4. The DAC produces analog output corresponding to

Transmission Gate? digital signal in

(a) It has one NMOS and one PMOS connected in off set switch

0

Parallel + S2 –

0.5V 0.5V

(b) Control Input is connected to gate of NMOS and – +

complement of the control input to gate of PMOS Roff = R/7

(c) It has one NMOS and one PMOS connected in 1

S0 R

R

–

Series 0

1 S1 R/2 + V0

(d) It works as a controlled electronic switch

0

1 S2 R/4

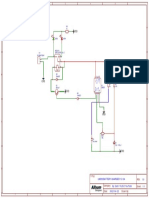

2. The circuit shown in the following figure is a _______ 0

– +

gate. V(1) = 0.5V

+ –

V(0) = 0.5 V

VDD

Where S2 is MSB and S0 is LSB

(a) 1’s complement format

A B (b) 2’s complement format

(c) Straight binary format

Out (d) BCD format

5.

A off set switch

0

+ S2 –

0.5V 0.5V

– +

B Roff = R/7

1 R

S0 R

–

0 +

(a) AND (b) OR 1 S1 R/2 V0

(c) NAND (d) NOR 0

1 S2 R/4

– 0

3. What is the minimum number of CMOS required for V(1) = 0.5V

+

V(0) = 0.5 V

constructing a two input NOR logic gate? + –

Where S2 is MSB and S0 is LSB

The following changes are made in the circuit.

(i) Offset switch is removed.

(ii) Switch S2 is replaced by S2 and

(iii) Resistor R/4 is replaced by R/3

Now, the DAC produces analog output corresponding

to digital signal in

(a) 1’complement format

(b) 2’s complement format

(c) straight binary format

(d) BCD format

2

6. In the CMOS inverter circuit shown below, if output

gets accidentally shorted, then

+VDD

T2

x y

T1

(a) T1 is at high risk of getting damaged.

(b) T2 is at high risk of geeting damaged.

(c) T1 and T2 both are at high risk of getting damaged.

(d) Neither T1 nor T2 is at risk of getting damaged

3

Answer Key

1. (c)

2. (c)

3. (4)

4. (a)

5. (a)

6. (b)

For more questions, kindly visit the library section: Link for app: https://physicswallah.live/tabs/tabs/library-tab

For more questions, kindly visit the library section: Link for web: https://links.physicswallah.live/vyJw

PW Mobile APP: https://play.google.com/store/apps/details?id=xyz.penpencil.physicswala

For PW Website: https://www.physicswallah.live/contact-us

You might also like

- Mad in AmericaDocument13 pagesMad in AmericaSadia AshrafNo ratings yet

- Test Bank For Essentials of Health Information Management 4th Edition by BowieDocument12 pagesTest Bank For Essentials of Health Information Management 4th Edition by Bowiebevisphuonglc1u5No ratings yet

- Man d0834 d0836 Spec Sheet p1jpgDocument6 pagesMan d0834 d0836 Spec Sheet p1jpgFERNANDO FERRUSCA100% (2)

- ALL P-Cube QuestionsDocument10 pagesALL P-Cube QuestionsNicole NgNo ratings yet

- OBGYN and Infertility Handbook For CliniciansDocument237 pagesOBGYN and Infertility Handbook For CliniciansAmal Farah100% (2)

- Library Management SystemDocument58 pagesLibrary Management SystemPurushottam Choudhary100% (9)

- Digital To Analog Converters - TutorialspointDocument5 pagesDigital To Analog Converters - Tutorialspointdiether.gozumNo ratings yet

- Installation Instructions: EnglishDocument22 pagesInstallation Instructions: EnglishSandorGyorfiNo ratings yet

- Analog Crash Course Workbook GaDocument54 pagesAnalog Crash Course Workbook GaAbhishek RajNo ratings yet

- Ece 374 Part 7 Mosfet 3Document14 pagesEce 374 Part 7 Mosfet 3Zakaria ElwalilyNo ratings yet

- Multiplexer CheviDocument1 pageMultiplexer CheviDollyNo ratings yet

- Multilevel Inverter With Reducing Device Count:: Project Batch-15Document20 pagesMultilevel Inverter With Reducing Device Count:: Project Batch-15madhu madhaviNo ratings yet

- Home-Constructed, Building Block Op-Amp Circuits For Analog Computers Inverting IntegratorDocument5 pagesHome-Constructed, Building Block Op-Amp Circuits For Analog Computers Inverting IntegratorMsuttonNo ratings yet

- ECEN 325 Lab 4: Operational Amplifiers - Part IIDocument4 pagesECEN 325 Lab 4: Operational Amplifiers - Part IISam AlbaNo ratings yet

- Product Datasheet: Flyback Transformer - Ef20Document1 pageProduct Datasheet: Flyback Transformer - Ef20ingucvNo ratings yet

- Eng 86799Document2 pagesEng 86799Prasad RampalliNo ratings yet

- Polytechnic University of Puerto Rico Mechanical Engineering Department Mechatronics ME-5250 Professor: Sandra L. OrdóñezDocument15 pagesPolytechnic University of Puerto Rico Mechanical Engineering Department Mechatronics ME-5250 Professor: Sandra L. OrdóñezGabriel PachecoNo ratings yet

- Redwan Ahmed Miazee - HW - 1Document3 pagesRedwan Ahmed Miazee - HW - 1REDWAN AHMED MIAZEENo ratings yet

- Diode Clipper CircuitsDocument13 pagesDiode Clipper Circuitsmajdzmm12No ratings yet

- Ao6401 HF - Ko6401 HFDocument4 pagesAo6401 HF - Ko6401 HFsuan kwang TanNo ratings yet

- 2SB649AM Series: Bipolar General Purpose PNP Power Transistor - 1.5A / - 120V, - 160V / 20WDocument4 pages2SB649AM Series: Bipolar General Purpose PNP Power Transistor - 1.5A / - 120V, - 160V / 20WFreddy CamposNo ratings yet

- Lecture (Diode As Clamper)Document2 pagesLecture (Diode As Clamper)Sheikh HarisNo ratings yet

- PV+ PV-S COM Input Side Output Side: Voltage Detection CircuitDocument1 pagePV+ PV-S COM Input Side Output Side: Voltage Detection CircuitRamiro BraccoNo ratings yet

- RD07MVS1: Silicon RF Power MOS FET (Document10 pagesRD07MVS1: Silicon RF Power MOS FET (RickyNSNo ratings yet

- Surface-Mount 4-Circuit Low-Side Switch Array SPF5002: External Dimensions FeaturesDocument1 pageSurface-Mount 4-Circuit Low-Side Switch Array SPF5002: External Dimensions Featureskatty cumbeNo ratings yet

- Virtual LabsDocument1 pageVirtual LabsSai GanthodNo ratings yet

- UntitledDocument1 pageUntitledHelder CruzNo ratings yet

- Nec Tokin PDFDocument2 pagesNec Tokin PDFAntero RafaelNo ratings yet

- Polka 10Document4 pagesPolka 10Francesc MasanaNo ratings yet

- Work3 2Document1 pageWork3 2Bas BasNo ratings yet

- Degree Electronic Engineeringe First Semester EXAMINATIONS 2020/2021Document3 pagesDegree Electronic Engineeringe First Semester EXAMINATIONS 2020/2021Peter JumreNo ratings yet

- Schematic LLM393Document1 pageSchematic LLM393Channa PrasadNo ratings yet

- Ds Ah 00658800Document2 pagesDs Ah 00658800acorkeryuNo ratings yet

- Animasi Dioda Dan Power SupllyDocument25 pagesAnimasi Dioda Dan Power SupllyPA videoNo ratings yet

- DC DC ConvertersDocument22 pagesDC DC ConvertersAnonymous UJs2uePNo ratings yet

- Advanced Electronics: Wave Shaping & Generating CircuitsDocument19 pagesAdvanced Electronics: Wave Shaping & Generating CircuitsGelvie LagosNo ratings yet

- A350 Hyd PDFDocument16 pagesA350 Hyd PDFSaleh El DalyNo ratings yet

- MULTIPLEXERDocument1 pageMULTIPLEXERShraavani TopleNo ratings yet

- Two Watt Meter Method: Voff 0 FREQ 50 VAMPL 311 Voff 0Document7 pagesTwo Watt Meter Method: Voff 0 FREQ 50 VAMPL 311 Voff 0Kornkanok PMNo ratings yet

- FinalExam ENM061 2021 04 07Document3 pagesFinalExam ENM061 2021 04 07Kostas GekasNo ratings yet

- DC Circuits: Fundamentals of Electric CircuitsDocument34 pagesDC Circuits: Fundamentals of Electric CircuitsHoàng HoàngAnhNo ratings yet

- Diagram Wiring RS 485: Power Supply Ke EvcDocument1 pageDiagram Wiring RS 485: Power Supply Ke EvcDatabase PalembangNo ratings yet

- 11.types of DiodesDocument13 pages11.types of DiodesAmmar HussamNo ratings yet

- Avh-13n-M1 (New Design) 2101Document2 pagesAvh-13n-M1 (New Design) 2101arihantidsNo ratings yet

- Exp 5 Zener Diode Characteristics and ApplicationsDocument4 pagesExp 5 Zener Diode Characteristics and ApplicationsGowsic PmNo ratings yet

- DA Converters: DigitalelectronicsiicourseDocument24 pagesDA Converters: DigitalelectronicsiicourseLeonardo Franzua Giraldo CardosoNo ratings yet

- Controller Design For BLDC MotorDocument15 pagesController Design For BLDC MotorAnonymous SdIsxrNo ratings yet

- BEE Lab For Ist YearsDocument32 pagesBEE Lab For Ist YearsMutya BalaNo ratings yet

- Enabele: New Project - PDSPRJ 12/19/2021 New Project - PDSPRJDocument1 pageEnabele: New Project - PDSPRJ 12/19/2021 New Project - PDSPRJ29Nyoman Danu Tri DamartaNo ratings yet

- Chapter 11 Part IDocument39 pagesChapter 11 Part Imstan11No ratings yet

- An 9723Document2 pagesAn 9723Stacy Mcclain100% (1)

- MultiplexerDocument1 pageMultiplexerMyra Ali KhanNo ratings yet

- Assignment 1 - Analog CircuitDocument1 pageAssignment 1 - Analog CircuitSV MNo ratings yet

- Power Electronics For RenewablesDocument22 pagesPower Electronics For RenewablesShiv Prakash M.Tech., Electrical Engineering, IIT(BHU)No ratings yet

- Small Signal Model AC AC IHDocument1 pageSmall Signal Model AC AC IHruanNo ratings yet

- Low-Side Switch Ics Spf5002A: (Surface-Mount 4-Circuits)Document2 pagesLow-Side Switch Ics Spf5002A: (Surface-Mount 4-Circuits)nurwi dikaNo ratings yet

- Circuit Analysis and Electronics Laboratory Calvin College: 22 April 2010Document11 pagesCircuit Analysis and Electronics Laboratory Calvin College: 22 April 2010beb5No ratings yet

- Diode Circuits ProblemDocument11 pagesDiode Circuits Problemsamantaramen86No ratings yet

- Slides of Lecture4Document34 pagesSlides of Lecture4rudra patraNo ratings yet

- Transformer: 5 AmpsDocument9 pagesTransformer: 5 AmpsMohammed Qaid AlathwaryNo ratings yet

- Digital Communication Systems First Edit - PDF 1Document3 pagesDigital Communication Systems First Edit - PDF 1Rakesh. N murthyNo ratings yet

- BEE Lab Manual - 2019 PDFDocument47 pagesBEE Lab Manual - 2019 PDFAdal ArasuNo ratings yet

- Flyback Converter Daniel W. HartDocument11 pagesFlyback Converter Daniel W. HartABHISHEK SHAWNo ratings yet

- Exp2.Study of RC Triggering CircuitDocument3 pagesExp2.Study of RC Triggering CircuitAbdullah MohammedNo ratings yet

- Auto Transformer: Auto Transformer Is Kind of Electrical Transformer Where Primary and Secondary Shares SameDocument8 pagesAuto Transformer: Auto Transformer Is Kind of Electrical Transformer Where Primary and Secondary Shares SameAbhishek PareekNo ratings yet

- Finite Automata 04 _ Class NotesDocument83 pagesFinite Automata 04 _ Class NotesAbhishek PareekNo ratings yet

- Star Delta Transformation: Wle 204 Circuit Theory Unit 2 Elementary Network AnalysisDocument14 pagesStar Delta Transformation: Wle 204 Circuit Theory Unit 2 Elementary Network AnalysisAbhishek PareekNo ratings yet

- My NameDocument2 pagesMy NameAbhishek PareekNo ratings yet

- Time DomainDocument3 pagesTime DomainAbhishek PareekNo ratings yet

- Frequency Domain - WikipediaDocument6 pagesFrequency Domain - WikipediaAbhishek PareekNo ratings yet

- Nuc Kit D34010wyk Product BriefDocument4 pagesNuc Kit D34010wyk Product BriefAbhishek PareekNo ratings yet

- Malaviya National Institute of Technology Jaipur: J. L. N. Marg, Malaviya Nagar, Jaipur-302017 (Rajasthan)Document8 pagesMalaviya National Institute of Technology Jaipur: J. L. N. Marg, Malaviya Nagar, Jaipur-302017 (Rajasthan)Abhishek PareekNo ratings yet

- VITEEE2020 EnglishandAptitudeDocument1 pageVITEEE2020 EnglishandAptitudeAbhishek PareekNo ratings yet

- Nuc Kit D34010wyk Product BriefDocument4 pagesNuc Kit D34010wyk Product BriefAbhishek PareekNo ratings yet

- Elec - Magnetism Course OutlineDocument4 pagesElec - Magnetism Course OutlineBernard PanganibanNo ratings yet

- Guru 1 - 5 Whats NewDocument19 pagesGuru 1 - 5 Whats NewLuca RosacutaNo ratings yet

- Egypt: Gec08-Science, Technology & Society Modern AgesDocument7 pagesEgypt: Gec08-Science, Technology & Society Modern AgesNo NameNo ratings yet

- OpenCV by Example - Sample ChapterDocument25 pagesOpenCV by Example - Sample ChapterPackt PublishingNo ratings yet

- SOCIOLOGICAL FOUNDATION ReportDocument14 pagesSOCIOLOGICAL FOUNDATION Reportᜃᜒᜈ᜔ᜎᜒ ᜇᜒᜋᜈ᜔ᜇᜒᜋᜈ᜔No ratings yet

- LAS 1A The Magic PomegranateDocument2 pagesLAS 1A The Magic PomegranateCherry Maravilla Basa MingoaNo ratings yet

- Crompton Instruments Integra Ci3: Digital Metering SystemDocument4 pagesCrompton Instruments Integra Ci3: Digital Metering SystemAmit BhatiaNo ratings yet

- Prevalence of Interpersonal Violence Against Athletes in The Sport Context (2017)Document5 pagesPrevalence of Interpersonal Violence Against Athletes in The Sport Context (2017)Juan Kmilo Martinez FernandezNo ratings yet

- OS Manual Oretronic III Rec4105LDocument152 pagesOS Manual Oretronic III Rec4105LJose ReedNo ratings yet

- Wtt12L-B2562: PowerproxDocument7 pagesWtt12L-B2562: PowerproxJCNo ratings yet

- Department of Education: A. Background Information For Learners B. Most Essential Learning CompetencyDocument9 pagesDepartment of Education: A. Background Information For Learners B. Most Essential Learning CompetencyCamille CaigaNo ratings yet

- AFI - 10-248 - Fitness ProgramDocument89 pagesAFI - 10-248 - Fitness ProgramDongelxNo ratings yet

- PSM SeminarDocument33 pagesPSM SeminarSamarth JainNo ratings yet

- Module 1 PDFDocument18 pagesModule 1 PDFYashaswiniNo ratings yet

- Influence of Ni On Martensitic Phase Transformations in NiTi Shape Memory Alloys 2010 Acta MaterialiaDocument15 pagesInfluence of Ni On Martensitic Phase Transformations in NiTi Shape Memory Alloys 2010 Acta MaterialiaJhonk FigueroaNo ratings yet

- Event Proposal FullDocument4 pagesEvent Proposal FullDarren Kate LicupaNo ratings yet

- Infectious Diseases 2022 Virtual Abstract BookDocument53 pagesInfectious Diseases 2022 Virtual Abstract BookSriNo ratings yet

- Mco 2 3 337 PDF PDFDocument4 pagesMco 2 3 337 PDF PDFhendra ardiantoNo ratings yet

- Luxacore IndicationDocument10 pagesLuxacore IndicationAnonymous UT3s7CNo ratings yet

- Fundmentals Energy ProcessDocument11 pagesFundmentals Energy ProcessepjxNo ratings yet

- 2595 0118 BRJP 02 03 0255Document5 pages2595 0118 BRJP 02 03 0255tariNo ratings yet

- Hearst Demystifying Media Fireside Chat - The Bloomberg Way With Matthew WinklerDocument16 pagesHearst Demystifying Media Fireside Chat - The Bloomberg Way With Matthew WinklerDemystifying MediaNo ratings yet

- Biological Conservation: Policy AnalysisDocument8 pagesBiological Conservation: Policy AnalysisEmilio Lecaros BustamanteNo ratings yet

- Why We Are Shallow by F. Sionil JoseDocument3 pagesWhy We Are Shallow by F. Sionil JosePrecy M AgatonNo ratings yet