Professional Documents

Culture Documents

Codec Block Diagram-2

Codec Block Diagram-2

Uploaded by

arfaaliOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Codec Block Diagram-2

Codec Block Diagram-2

Uploaded by

arfaaliCopyright:

Available Formats

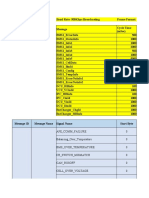

Date: December 07, 2020 filter.

bdf Project: filter

Parameter Value

INCLOCK_PERIOD 20000

INCLOCK_SETTINGS "USED"

VALID_LOCK_CYCLES 1

INVALID_LOCK_CYCLES 1

VALID_LOCK_MULTIPLIER 1

INVALID_LOCK_MULTIPLIER 1

OPERATION_MODE "NORMAL"

CLOCK0_BOOST 1

CLOCK0_DIVIDE 1

CLOCK0_SETTINGS "UNUSED"

CLOCK0_TIME_DELAY "0"

CLOCK1_BOOST 1

CLOCK1_DIVIDE 1

CLOCK1_SETTINGS "UNUSED"

CLOCK1_TIME_DELAY "0"

CLOCK2_BOOST 1

CLOCK2_DIVIDE 1

CLOCK2_SETTINGS "UNUSED"

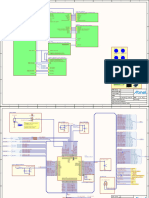

11.2896MHz codec clock

CLOCK2_TIME_DELAY "0"

CLOCK_EXT_BOOST 4 May deviate due to discrete multipliers/dividers

CLOCK_EXT_DIVIDE 18 44.1kHz 16bit sampling 256fs

CLOCK_EXT_SETTINGS "USED"

Using Audio CD sampling settings,

CLOCK_EXT_TIME_DELAY "0"

which gives us 2 options for the codec clock AUD_XCLK: 256fs and 384fs

OUTCLOCK_PHASE_SHIFT 0

(read the manual) altclklock

50MHz master clock

CLOCK_50 INPUT

VCC

inclock OUTPUT AUD_XCK

PIN_G7

PIN_AF14

clock_ext

Starts with 0 and rises long after PLL stabilises

inst (used as power on reset)

sync

PIN_H7

Digital Audio interface, master mode clk Ds Synchronous parallel interfaces

PIN_K7 Da s2p_adaptor fir

64x44.1kHz

AUD_BCLK INPUT

AUD_BCLK ADCDAT[15..0] ADCdat[15..0]

VCC

inst5 ADCstb ADCstb

AUD_ADCDAT INPUT

AUD_ADCDAT

PIN_K8 VCC ADCrdy ADCrdy

AUD_ADCLRCK INPUT

AUD_ADCLRCK

VCC

AUD_DACDAT

AUD_DACDAT OUTPUT

PIN_J7 AUD_DACLRCK INPUT

VCC

sync AUD_DACLRCK

DACDAT[15..0] DACdat[15..0]

clk Ds CLOCK_50 DACstb DACstb

Da RST_N DACrdy DACrdy

PIN_H8

inst1

inst6 CLOCK_50

RST_N

inst3

Synchronizers "sync" are

codec_init

used with all asynchronous

sync

inputs that are sampled CLOCK_50 SCLK OUTPUT FPGA_I2C_SCLK

PIN_J12

very close to their change. clk Ds RES_N SDIN OUTPUT FPGA_I2C_SDAT

KEY[0] INPUT

VCC Da 2-wire MPU interface

PIN_AA14 (i2c compatible) PIN_K12

inst2

inst4

Page 1 of 1 Revision: filter

You might also like

- Case StudyDocument4 pagesCase StudyShivang Bhatt100% (1)

- Timer SecDocument1 pageTimer SecAnggraini IsmailNo ratings yet

- Full - 0 Empty - 0: FIFO GeneratorDocument1 pageFull - 0 Empty - 0: FIFO GeneratorDaniel FloresNo ratings yet

- THU2 - NGAY3-7 L24 - V15.1 / PLC - 1 (CPU 1215C DC/DC/DC) / Program BlocksDocument5 pagesTHU2 - NGAY3-7 L24 - V15.1 / PLC - 1 (CPU 1215C DC/DC/DC) / Program BlocksĐại Anh HùngNo ratings yet

- LI708Document1 pageLI708pernetiNo ratings yet

- Reply Daly BattrixxDocument40 pagesReply Daly Battrixxyogesh kumar jaiswalNo ratings yet

- Arbol - Primates - 212 - Adriana Botero - Santiago DuarteDocument1 pageArbol - Primates - 212 - Adriana Botero - Santiago DuarteAdriana Marcela Botero PitoNo ratings yet

- Bài 1Document2 pagesBài 1Hưng Trần ĐứcNo ratings yet

- ClockDocument1 pageClockLam Pham TungNo ratings yet

- SAML21 Xplained Pro Design Documentation Release Rev4Document21 pagesSAML21 Xplained Pro Design Documentation Release Rev4nelepag194No ratings yet

- 36 Lansang vs. Court of AppealsDocument1 page36 Lansang vs. Court of AppealsRoushael Cient MontealtoNo ratings yet

- A Meta-Analysis of Passive Descent Versus Immediate Pushing in NulliparousDocument10 pagesA Meta-Analysis of Passive Descent Versus Immediate Pushing in NulliparousNoraNo ratings yet

- CV Review 35Document1 pageCV Review 35Pean CkNo ratings yet

- T7 B12 Flight 93 Calls - Jeremy Glick FDR - FBI 302 Transcript - Joanne Makely 911 Call 412Document48 pagesT7 B12 Flight 93 Calls - Jeremy Glick FDR - FBI 302 Transcript - Joanne Makely 911 Call 4129/11 Document ArchiveNo ratings yet

- Vesda Laser Focus 250Document2 pagesVesda Laser Focus 250WERMERMNo ratings yet

- PCUPDocument6 pagesPCUPBonn PustaNo ratings yet

- IC-A210 Manual PDFDocument40 pagesIC-A210 Manual PDFErick Morales UrbinaNo ratings yet

- Training Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchDocument3 pagesTraining Memorandum of Agreement/Waiver: Polytechnic University of The Philippines Quezon City BranchAnton ArponNo ratings yet

- Using Option Open Interest To Develop Short Term Price TargetsDocument11 pagesUsing Option Open Interest To Develop Short Term Price TargetsShaun DingNo ratings yet

- Pa2 Class 11 Commerce Blue Print PDFDocument1 pagePa2 Class 11 Commerce Blue Print PDFKash Ghuman tvNo ratings yet

- BL en BlancoDocument1 pageBL en Blancoana bejaranoNo ratings yet

- Parth Purandare SAP: 80101190556 1. Introduce YourselfDocument4 pagesParth Purandare SAP: 80101190556 1. Introduce YourselfParth Hemant PurandareNo ratings yet

- 05968Document4 pages05968Miguel ChaconNo ratings yet

- Robin CVDocument6 pagesRobin CVAulya MuctNo ratings yet

- Experiment #4 Title: Testing of Reinforcing Steel BarsDocument9 pagesExperiment #4 Title: Testing of Reinforcing Steel BarsAnne Kristel Dela RosaNo ratings yet

- Keyboard Shortcuts For Windows and MacDocument13 pagesKeyboard Shortcuts For Windows and MacJahirul HaqueNo ratings yet

- Duolingo 50 Words Essay Questions and AnswerDocument7 pagesDuolingo 50 Words Essay Questions and AnswerMaria AgnesNo ratings yet

- CandidateHallTicket PDFDocument1 pageCandidateHallTicket PDFAditya YadavNo ratings yet

- Generators: Model: PDG25 25 KVA Available in Single Phase and Three PhaseDocument2 pagesGenerators: Model: PDG25 25 KVA Available in Single Phase and Three Phaseefmartin21No ratings yet

- The Adoption of The Principles of Equity Jurisprudence Into The ADocument12 pagesThe Adoption of The Principles of Equity Jurisprudence Into The AAjinkya PatilNo ratings yet

- Adtran HDSL2 H2turDocument90 pagesAdtran HDSL2 H2tursexton hardfortNo ratings yet

- TLEICT9 Module (Week 1) PDFDocument5 pagesTLEICT9 Module (Week 1) PDFAN GelNo ratings yet

- CMD Message: Deepak Kumar Hota Chairman & Managing Director BemlDocument1 pageCMD Message: Deepak Kumar Hota Chairman & Managing Director BemlMadhurya KrishnaNo ratings yet

- Recereum WhitePaperDocument23 pagesRecereum WhitePaperLord VNo ratings yet

- People Vs ObsaniaDocument2 pagesPeople Vs Obsaniaminri721No ratings yet

- 2 Classes and Objects2018-10-23 14 - 17 - 43Document71 pages2 Classes and Objects2018-10-23 14 - 17 - 43RiyaNo ratings yet

- Brio125-3: Spare Parts CatalogueDocument56 pagesBrio125-3: Spare Parts CatalogueRomanos St.No ratings yet

- Lab - Manual LP V (2019PATERN)Document39 pagesLab - Manual LP V (2019PATERN)Vaishnavi DhimateNo ratings yet

- Application For ECFMG Certification - InstructionsDocument2 pagesApplication For ECFMG Certification - InstructionszidaneNo ratings yet