Professional Documents

Culture Documents

PT2399

PT2399

Uploaded by

ZriastyCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PT2399

PT2399

Uploaded by

ZriastyCopyright:

Available Formats

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

DESCRIPTION

PT2399 is an echo audio processor IC utilizing CMOS Technology which is equipped with ADC and

DAC, high sampling frequency and an internal memory of 44K Digital processing is used to generate

the delay time, it also features an internal VCO circuit in the system clock, thereby, making the fre-

quency easily adjustable. PT2399 boast of very low distortion (THD<0.5%) and very low noise

(No<-90dBV), thus producing high quality audio output. The pin assignments and application circuit are

optimized for easy PCB layout and cost saving advantage.

FEATURES

• CMOS Technology

• Least External Components

• Auto Reset Function

• Low Noise, No<-90dBV Typical

• Low Distortion, THD<0.5% Typical

• External Adjustable VCO

• Available in 16 pins, DIP or SOP

APPLICATIONS

• Video Tape Recorder

• Video Compact Disk

• Television

• CD Player

• Car Stereo

• KARAOKE Mixer

• Electronic Musical Instrument

• Audio Equipment with Echo Processor

PT2399 V1.4 -1- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

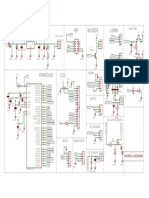

BLOCK DIAGRAM

LPF2-OUT

LPF1-OUT

OP2-OUT

OP1-OUT

LPF1-IN

LPF2-IN

OP2-IN

OP1-IN

CC1

CC0

16 15 14 13 12 11 10 9 8 7

4.7K 4.7K

MOD

_

+

_ COMP LPF2

_ _ _ DEM

+ +

+ +

LPF1

DI DO0 DO1

1/2 Vcc

MO MI CLOCK

AUTO

RESET

44K Bits VCO

RAM

1 2 3 4 5 6

AGND

DGND

VCO

VCC

REF

CLK_O

PT2399 V1.4 -2- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

PIN CONFIGURATION

VCC 1 16 L P F1 -I N

REF 2 15 L P F1 -O U T

AGND 3 14 L P F2 -O U T

DGND 4 13 L P F2 -I N

P T2399

C L K_ O 5 12 O P 2- O U T

VCO 6 11 O P 2- IN

CC1 7 10 O P 1- IN

CC0 8 9 O P 1- O U T

PIN DESCRIPTION

Pin Name I/O Description Pin No.

VCC - Analog Supply Voltage Input 1

REF - Analog Reference Voltage (1/2VCC) 2

AGND - Analog Ground 3

DGND - Digital Ground 4

CLK_O O System Clock Output Pin 5

VCO I Frequency Adjustment Pin 6

CC1 - Current Control 1 7

CC0 - Current Control 0 8

OP1-OUT O OP Amplifier 1 Input/Output, This pin can be used as 9

Modulated/Demodulated Integrator by connecting

OP1-IN I Capacitor 10

OP2-IN I OP Amplifier 2 Input/Output, This pin can be used as 11

Modulated/Demodulated Integrator by connecting

OP2-OUT O Capacitor 12

LPF2-IN I 13

Low Pass Filter 2 Input/Output Pin

LPF2-OUT O 14

LPF1-OUT O 15

Low Pass Filter 1 Input/Output Pin

LPF1-IN I 16

PT2399 V1.4 -3- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

FUNCTION DESCRIPTION

ECHO MODE

Please refer to the diagram below:

Vout

Vin

+ Low P ass

Filter

A /D Delay Time

Circuit

D/A Low P ass

Filter

AUTO RESET FUNCTION

The waveform of the signal during power on is given below:

Power ON

Reset Time = 400 ms

PT2399 V1.4 -4- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

ABSOLUTE MAXIMUM RATING

(Unless otherwise specified, Ta=25℃)

Parameter Symbol Rating Unit

Supply Voltage Vcc 6.5 V

Supply Current Icc 100 mA

Power Dissipation Pd 1.7 W

Operation Temperature Topr -40 to +85 ℃

Storage Temperature Tstg -65 to +150 ℃

RECOMMENDED OPERATING CONDITIONS

Parameter Symbol Min. Typ. Max. Unit

Supply Voltage Vcc 4.5 5 5.5 V

Clock Frequency fck - 4 5 MHz

AC CHARACTERISTICS

(Unless otherwise specified: Vcc=5.0V, fin=1KHz, Vi=100mVrms, fck=2MHz, Ta=25℃)

Parameter Symbol Test Condition Min. Typ. Max. Unit

Supply Voltage Vcc - 4.5 5.0 5.5 V

Supply Current Icc - - 30 40 mA

Voltage Gain Gv RL=47KΩ - -0.5 2.5 dB

Max. Output Voltage Vomax THD=10% 1.5 2 2.5 Vrms

Output Distortion THD filter=A-weighting - 0.3 1.0 %

Output Noise Voltage No filter=A-weighting - -90 -80 dBV

Power Supply Rejection ΔVcc=-20dBV(0.1Vrms),

PSRR - -40 -30 dB

Ratio f=100Hz

PT2399 V1.4 -5- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

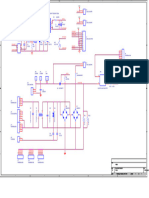

APPLICATION CIRCUIT

ECHO

3900pF 15K 4.7 µF

Input

+

100K

4.7 µF

10K

+5V 1 16

560pF +

100 µF 47 µF 10K

0.1 µF +

+

2 15 4.7K 10 µF

5.6K Output

10 µF

3 14 + 10K

+

0.01µ F 50K

4 13

PT23 99 15K

5 12

20K R 560pF 10K

3300pF

6 11

0.082 µF

7 10 10K

0.1 µF 0.082 µF

AGND DGND

8 9

0.1 µF

Note:

External Resistor having a value of 10 KΩ to 50 KΩ may be used. The recommended Resistor Value(R)

is 10 KΩ. When the value of the Resistor (R) increases, the range of the Delay Time also increases.

PT2399 V1.4 -6- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

SURROUND/DELAY

5600pF 15K 4.7 µF

Input

100K

10K

+5V 1 16

100 µF 47 µF 560pF 15K

0.1 µF

2 15

2.7K

10 µF

3 14 Output

0.01µ F

4 13

PT23 99 15K

5 12

R 560pF 10K

5600pF

6 11

0.1 µF

7 10 15K

0.1 µF 0.1 µF AGND DGND

8 9

0.1 µF

Note: Please refer to Table 1 for the Resistor/Delay Time values.

PT2399 V1.4 -7- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

TABLE 1: RESISTOR/DELAY TIME VALUES

R 27.6K 21.3K 17.2K 14.3K 12.1K 10.5K 9.2K 8.2K

fck 2.0M 2.5M 3.0M 3.5M 4.0M 4.5M 5.0M 5.5M

td 342ms 273ms 228ms 196ms 171ms 151ms 136.6ms 124.1ms

THD 1.0% 0.8% 0.63% 0.53% 0.46% 0.41% 0.36% 0.33%

R 7.2K 6.4K 5.8K 5.4K 4.9K 4.5K 4K 3.4K

fck 6.0M 6.5M 7.0M 7.5M 8.0M 8.5M 9.0M 10M

td 113.7ms 104.3ms 97.1ms 92.2ms 86.3ms 81ms 75.9ms 68.1ms

THD 0.29% 0.27% 0.25% 0.25% 0.23% 0.22% 0.21% 0.19%

R 2.8K 2.4K 2K 1.67K 1.47K 1.28K 1.08K 894

fck 11M 12M 13M 14M 15M 16M 17M 18M

td 61.6ms 56.6ms 52.3ms 48.1ms 45.8ms 43ms 40.6ms 38.5ms

THD 0.18% 0.16% 0.15% 0.15% 0.15% 0.15% 0.14% 0.14%

R 723 519 288 0.5

fck 19M 20M 21M 22M

td 36.6ms 34.4ms 32.6ms 31.3ms

THD 0.14% 0.13% 0.13% 0.13%

Note:

1. R = External Resistor (Ω), please refer to PT2399 Surround/Delay Time Application Circuit.

2. fck = Clock Frequency (Hz).

3. td = Delay Time

4. THD = Total Harmonic Distortion

PT2399 V1.4 -8- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

ORDER INFORMATION

Part Number Package Type Top Code

PT2399 16 Pins, DIP, 300mil PT2399

PT2399S 16 Pins, SOP, 300mil PT2399S

PT2399-SN 16 Pins, SOP, 150mil PT2399-SN

PT2399 (L) 16 Pins, DIP, 300mil PT2399

PT2399S (L) 16 Pins, SOP, 300mil PT2399S

PT2399-SN (L) 16 Pins, SOP, 150mil PT2399-SN

Notes:

1. (L), (C) or (S) = Lead Free.

2. The Lead Free mark is put in front of the date code.

PT2399 V1.4 -9- October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

PACKAGE INFORMATION

16 PINS, DIP, 300 MIL

PT2399 V1.4 - 10 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

Symbol Min. Nom. Max.

A - - 0.210

A1 0.015 - -

A2 0.115 0.130 0.195

b 0.014 0.018 0.022

b1 0.014 0.018 0.020

b2 0.045 0.060 0.070

b3 0.030 0.039 0.045

c 0.008 0.010 0.014

c1 0.008 0.010 0.011

D 0.780 0.790 0.800

D1 0.005 - -

E 0.300 0.310 0.325

E1 0.240 0.250 0.280

e 0.100 BSC.

eA 0.300 BSC.

eB - - 0.430

eC 0.000 - 0.060

L 0.115 0.130 0.150

Notes:

1. Controlling Dimension: INCHES.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensions “A”, “A1” and “L” are measured with the package seated in JEDEC Seating Plane

Gauge GS-3.

4. “D, “D1” and “E1” dimensions do not include mold flash or protrusions. Mold flash or protrusions

shall not exceed 0.010 inch.

5. “E” and “eA” measured with the leads constrained to be perpendicular to datum -C-.

6. “eB” and “eA” are measured at the lead tips with the leads unconstrained.

7. N is the maximum number of terminal positions (N=16).

8. Pointed or rounded lead tips are preferred to ease insertion.

9. “b2” and “b3” maximum dimensions do not include dambar protrusions. Dambar protrusions shall

not exceed 0.010 (0.25mm).

10. Variation AB is a full lead package.

11. Distance between leads including dambar protrusions to be 0.005 in minimum.

12. Datum plane -H- coincident with the bottom of lead where lead exits body.

13. Refer to JEDEC MS-001 Variation AB.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2399 V1.4 - 11 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

16 PINS, SOP, 300 MIL

Symbol Min. Max

A 2.35 2.65

A1 0.10 0.30

B 0.33 0.51

C 0.23 0.32

D 10.10 10.50

E 7.40 7.60

e 1.27 BSC.

H 10.00 10.65

h 0.25 0.75

L 0.40 1.27

α 0o 8o

PT2399 V1.4 - 12 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

Notes:

1. Controlling Dimension: MILLIMETER

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and

gate burrs shall not exceed 0.15mm (0.006 in) per side.

4. Dimension “E” does not include interlead flash or protrusions. Interlead flash and protrusions shall

not exceed 0.25 mm (0.010 in.) per side

5.. The chamfer on the body is optional. If it is not present, a visual index feature must be located

within the crosshatched area

6. L is the length of the terminal for soldering to a substrate.

7. N is the number of terminal positions (N=16).

8 The lead width B, as measured 0.36 mm (0.014in) or greater above the seating plane, shall not

exceed a maximum value of 0.61mm (0.024in.)

9. Refer to JEDEC MS-013 Variation AA.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2399 V1.4 - 13 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

16 PINS, SOP, 150MIL

PT2399 V1.4 - 14 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

PT2399 V1.4 - 15 - October, 2005

Tel: 886-2-66296288

Fax: 886-2-29174598

URL: http://www.princeton.com.tw

Echo Processor IC PT2399

Symbol Min. Typ. Max.

A 1.35 - 1.75

A1 0.10 - 0.25

A2 1.25 - 1.65

b 0.31 - 0.51

b1 0.28 - 0.48

c 0.17 - 0.25

c1 0.17 - 0.23

D 9.90 BSC.

E 6.00 BSC.

E1 3.90 BSC.

e 1.27 BSC.

L 0.40 - 1.27

L1 1.04 REF.

L2 0.25 BSC.

R 0.07 - -

R1 0.07 -

h 0.25 - 0.50

θ 0° - 8°

θ1 5° - 15°

θ2 0° - -

Note:

1. Dimensioning and tolerancing per ANSI Y 14.5M-1994

2. Controlling Dimension: MILLIMETERS.

3. Dimension D does not include mold flash protrusions or gate burrs. Mold flash, protrusions or

gate burrs shall not exceed 0.15 mm (0.006 in) per end. Dimension E1 does not include

interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25mm per side. D

and E1 dimensions are determined at datum H.

4. The package top may be smaller than the package bottom. Dimensions D and E1 are

determined at the outermost extremes of the plastic body exclusive of mold flash, tie bar burrs,

gate burrs and interlead flash, but including any mismatch between the top and bottom of the

plastic body.

5. Datums A & B to be determined at datum H.

6. N is the number of terminal positions. (N=8)

7. The dimensions apply to the flat section of the lead between 0.10 to 0.25mm from the lead tip.

8. Dimension “b” does not include dambar protrusion. Allowable dambar protrusion shall be

0.10mm total in excess of the “b” dimension at maximum material condition. The dambar cannot

be located on the lower radius of the foot.

9. This chamfer feature is optional. If it is not present, then a pin 1 identifier must be located within

the index area indicated.

10. Refer to JEDEC MS-012, Variation AC.

JEDEC is the registered trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2399 V1.4 - 16 - October, 2005

You might also like

- Discrete-Time Digital Signal Processing - Oppenheim, Schafer & Buck PDFDocument895 pagesDiscrete-Time Digital Signal Processing - Oppenheim, Schafer & Buck PDFKishanNo ratings yet

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Ducati2 SCH 20140506 0930 PDFDocument34 pagesDucati2 SCH 20140506 0930 PDFRiza VirsadaNo ratings yet

- PT 2399Document11 pagesPT 2399Ruggero StellaNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- 19 Exercise IEC61850 E SWDocument21 pages19 Exercise IEC61850 E SWlephuonganh_2001No ratings yet

- Program Comments: Mov - W ENO EN Always - OnDocument25 pagesProgram Comments: Mov - W ENO EN Always - OnAmbar Jati WaluyoNo ratings yet

- Description: 6-Channel Audio Processor IC PT2322Document21 pagesDescription: 6-Channel Audio Processor IC PT2322Tatap MasukNo ratings yet

- Autoplex system-RICDocument1 pageAutoplex system-RICPrakash BhuvanendranNo ratings yet

- D V B S R B H P S C M: Ivaylo Mashev, Nikolay Kakanakov, Dimitar GrozevDocument6 pagesD V B S R B H P S C M: Ivaylo Mashev, Nikolay Kakanakov, Dimitar GrozevSALAH NETNo ratings yet

- 8051 DatasheetDocument105 pages8051 Datasheetvarsha muthyalaNo ratings yet

- Secure Soic Click Schematic v100Document1 pageSecure Soic Click Schematic v100Gogo GogevNo ratings yet

- 970ff Acer Travelmate 5220 5520 7520 7520g Extensa 5120 5420 Wistron Pomona Texcoco Rev - 1 SCH PDFDocument49 pages970ff Acer Travelmate 5220 5520 7520 7520g Extensa 5120 5420 Wistron Pomona Texcoco Rev - 1 SCH PDFLouis DiasNo ratings yet

- Hanover 6500 BB-PL Lab1 Ver5Document4 pagesHanover 6500 BB-PL Lab1 Ver5Federico RossettiNo ratings yet

- STC89C51RC_FeaturesDocument14 pagesSTC89C51RC_FeaturesWilliam lopexNo ratings yet

- Emx5000-12/20 Circuit Diagram 7/9 (DSP-SPX)Document3 pagesEmx5000-12/20 Circuit Diagram 7/9 (DSP-SPX)Jeff BrintonNo ratings yet

- lpc1114 SynthDocument1 pagelpc1114 SynthMirel-Cătălin ChirilăNo ratings yet

- SM J100M Tshoo 7 PDFDocument50 pagesSM J100M Tshoo 7 PDFRosbel HernandezNo ratings yet

- Chip OutPSM TemplateDocument20 pagesChip OutPSM TemplateVbaluyoNo ratings yet

- Cxa 1124Document24 pagesCxa 1124alireza.athensNo ratings yet

- Daewoo DHT200NT Divx Vribatto Ii DVD SMDocument22 pagesDaewoo DHT200NT Divx Vribatto Ii DVD SMLeordeanu FlorianNo ratings yet

- JVC MX-J100 PDFDocument10 pagesJVC MX-J100 PDFJuan De la BarreraNo ratings yet

- Block Diagrams: Main SectionDocument10 pagesBlock Diagrams: Main Sectionpaco37No ratings yet

- BL0306 Igual Ao PT2395 PDFDocument2 pagesBL0306 Igual Ao PT2395 PDFRobson DiasNo ratings yet

- E2 Rothschild DSC: rPGA Arrandale + Fcbga PCH Ibexpeak-M + N10M-NS-SDocument66 pagesE2 Rothschild DSC: rPGA Arrandale + Fcbga PCH Ibexpeak-M + N10M-NS-SAMEN HAG MOSANo ratings yet

- VCC VCC VCC GND GND: Sheet - 1Document1 pageVCC VCC VCC GND GND: Sheet - 1Chandra Sekaran100% (1)

- TEX1000-LCD: User ManualDocument60 pagesTEX1000-LCD: User ManualFelipe Quinde100% (2)

- Walkie Talkie GERBERDocument1 pageWalkie Talkie GERBERAbhishek TiwariNo ratings yet

- Volvi2 - Usb BD - 1 - 0703Document1 pageVolvi2 - Usb BD - 1 - 0703Francisco RomeroNo ratings yet

- IBM Thinkpad Z61 (Quanta BW2)Document80 pagesIBM Thinkpad Z61 (Quanta BW2)Maks ProstNo ratings yet

- PLC ArchitectureDocument4 pagesPLC ArchitecturekapsarcNo ratings yet

- Zasilanie ISP Buzzer L298N: SwitcheDocument1 pageZasilanie ISP Buzzer L298N: SwitcheSCNo ratings yet

- Interfacing The 8051 MicrocontrollerDocument9 pagesInterfacing The 8051 Microcontrollerummulkhulsu100% (1)

- OLUPS SCR B21 SchematicsDocument1 pageOLUPS SCR B21 SchematicsaananthuajaysNo ratings yet

- Amplificador-Microfone_2024-07-02Document1 pageAmplificador-Microfone_2024-07-02Leonardo AlmeidaNo ratings yet

- Preliminary: 6-Channel Audio Processor ICDocument18 pagesPreliminary: 6-Channel Audio Processor ICВлад ВолошинNo ratings yet

- Atmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFDocument312 pagesAtmel 9111 LIN Networking ATA6612C ATA6613C - Datasheet PDFAnkadi Sikari ReddyNo ratings yet

- SA-MAX700 Diagrama y Voltajes - 48016Document41 pagesSA-MAX700 Diagrama y Voltajes - 48016loquiNo ratings yet

- Description: 6-Ch Audio Selector PT2323Document17 pagesDescription: 6-Ch Audio Selector PT2323panjoelsNo ratings yet

- CD9088CB-FORWARD ZH-CN enDocument3 pagesCD9088CB-FORWARD ZH-CN enmohamed tawfikNo ratings yet

- Snx-300 Service Manual (Eg)Document15 pagesSnx-300 Service Manual (Eg)Adriano CarvalhoNo ratings yet

- 21bec0499 VL2023240100568 Ast05Document4 pages21bec0499 VL2023240100568 Ast05Om PotdarNo ratings yet

- Description: Echo Processor ICDocument4 pagesDescription: Echo Processor ICdasyir baeNo ratings yet

- Indoor-Garden MEGA DAS PDFDocument1 pageIndoor-Garden MEGA DAS PDFAhmad RizalNo ratings yet

- Ec2 UsbDocument1 pageEc2 UsbzkovaNo ratings yet

- Schematic Inductor Meter 2022-01-19 FiyoihfdnyDocument1 pageSchematic Inductor Meter 2022-01-19 FiyoihfdnyIpoelNo ratings yet

- GPS EspDocument5 pagesGPS Espjak broseNo ratings yet

- Schematic - Sismun Line Coci - 2021-11-18Document1 pageSchematic - Sismun Line Coci - 2021-11-18CAHYA FIRDHOUS100% (1)

- Schematic Mcu Card 6 For stm32Document1 pageSchematic Mcu Card 6 For stm32Lai Viet ThangNo ratings yet

- Manual de Electronica - Pic Programmer All-Flash Usb Kit128Document32 pagesManual de Electronica - Pic Programmer All-Flash Usb Kit128Erik MatomaNo ratings yet

- Tonepad Orangesqueezer2Document1 pageTonepad Orangesqueezer2Marco AurelioNo ratings yet

- MC34119Document17 pagesMC34119Joe ErdeNo ratings yet

- Jura XJ9 Wiring DiagramDocument3 pagesJura XJ9 Wiring DiagramGrom Neposeda50% (2)

- Arb 1479Document4 pagesArb 1479home madeNo ratings yet

- Isl 94202Document89 pagesIsl 94202Aura SantiagoNo ratings yet

- Level 3 Repair: 8-1. Block DiagramDocument54 pagesLevel 3 Repair: 8-1. Block DiagramAndroid Schematics and CircuitsNo ratings yet

- Smartsim340 Schematic v100Document1 pageSmartsim340 Schematic v100bruno magalhãesNo ratings yet

- Project Code: 91.44K01.001 PCB P/N: ? Part Number: 03215: CRT LCD TV OutDocument49 pagesProject Code: 91.44K01.001 PCB P/N: ? Part Number: 03215: CRT LCD TV OutLuis SilveiraNo ratings yet

- LEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingFrom EverandLEARN MPLS FROM SCRATCH PART-B: A Beginners guide to next level of networkingNo ratings yet

- LG-838-2 MK: Legacy - 8 Inch - SubwooferDocument2 pagesLG-838-2 MK: Legacy - 8 Inch - Subwoofergln2No ratings yet

- Applsci 09 00259 PDFDocument17 pagesApplsci 09 00259 PDFMohamed ElsayedNo ratings yet

- Exp7 NewDocument11 pagesExp7 NewMohammed A. ElsayedNo ratings yet

- Introduction To Engineering: A Starter's Guide With Hands-On Digital Multimedia and Robotics ExplorationsDocument176 pagesIntroduction To Engineering: A Starter's Guide With Hands-On Digital Multimedia and Robotics Explorationssnri0da9No ratings yet

- Properties of Discrete Time Convolution: Stephen KruzickDocument4 pagesProperties of Discrete Time Convolution: Stephen KruzickLoredana MariaNo ratings yet

- Noise PSDDocument4 pagesNoise PSDdi diNo ratings yet

- Images TBDocument916 pagesImages TBsebastianNo ratings yet

- Ec8093-Digital Image Processing: Dr.K.Kalaivani Associate Professor Dept. of EIE Easwari Engineering CollegeDocument37 pagesEc8093-Digital Image Processing: Dr.K.Kalaivani Associate Professor Dept. of EIE Easwari Engineering CollegeKALAIVANINo ratings yet

- Tom, Dick and Mary Discover The FFTDocument15 pagesTom, Dick and Mary Discover The FFTNataniel MaggioraNo ratings yet

- LABEX3 SolDocument57 pagesLABEX3 SolKea Hottendorf0% (1)

- Session 1Document23 pagesSession 1Noorullah ShariffNo ratings yet

- Unit 3Document30 pagesUnit 3Rakesh MenonNo ratings yet

- 1 Darlington Pair AmplifierDocument2 pages1 Darlington Pair AmplifierSheikh Noor MohammadNo ratings yet

- Spectrum and Signal Analys - Pulsed RF (Agilent)Document29 pagesSpectrum and Signal Analys - Pulsed RF (Agilent)Wesley GeorgeNo ratings yet

- Iniyavan Thesisdraft Delft PDFDocument102 pagesIniyavan Thesisdraft Delft PDFthitanaNo ratings yet

- Band Pass Filter - Passive RC Filter TutorialDocument6 pagesBand Pass Filter - Passive RC Filter Tutorialmr mrNo ratings yet

- DSP-AX1/RX-V1: Av Amplifier/Av ReceiverDocument120 pagesDSP-AX1/RX-V1: Av Amplifier/Av ReceiverKarl Symon SuarezNo ratings yet

- Analog and Digital Communication SyllabusDocument3 pagesAnalog and Digital Communication SyllabusSrinivas SamalNo ratings yet

- Studi Analisis Setting Filter Aktif Terhadap Peningkatan Kualitas Daya Listrik Di Gedung Perkuliahan Fakultas Teknik Universitas Udayana Jalan PB SudirmanDocument6 pagesStudi Analisis Setting Filter Aktif Terhadap Peningkatan Kualitas Daya Listrik Di Gedung Perkuliahan Fakultas Teknik Universitas Udayana Jalan PB Sudirmansatriya DhinataNo ratings yet

- 222 - EC8501, EC6501 Digital Communication - NotesDocument96 pages222 - EC8501, EC6501 Digital Communication - NotesFebin C.S.No ratings yet

- Model of Resonance, Object For Max MSPDocument5 pagesModel of Resonance, Object For Max MSPpasNo ratings yet

- PSTNDocument26 pagesPSTNderejeNo ratings yet

- Seismic Data AnalysisDocument12 pagesSeismic Data Analysismanuel_henao_5No ratings yet

- Como Gravar Vocalizacoes de Primatas - InglesDocument13 pagesComo Gravar Vocalizacoes de Primatas - IngleslagartojrNo ratings yet

- Direction of Radio Finding Via MUSIC (Multiple Signal Classification) Algorithm For Hardware Design SystemDocument6 pagesDirection of Radio Finding Via MUSIC (Multiple Signal Classification) Algorithm For Hardware Design Systemantonio ScacchiNo ratings yet

- ModulationDocument9 pagesModulationJaneNo ratings yet

- Analog Reconstruction Filter For HDTV Using The THS8133, THS8134, THS8135, THS8200Document9 pagesAnalog Reconstruction Filter For HDTV Using The THS8133, THS8134, THS8135, THS8200Vikrant1No ratings yet

- Lec-04 Image Enhancement IIDocument41 pagesLec-04 Image Enhancement IImariiNo ratings yet

- IndtsDocument5 pagesIndtsSrinivas NiceNo ratings yet