Professional Documents

Culture Documents

Output

Output

Uploaded by

abhishek509.pCopyright:

Available Formats

You might also like

- 5 Steps To CPA Profits PDFDocument40 pages5 Steps To CPA Profits PDFimtool0% (1)

- 3D Reconstruction USING MULTIPLE 2D IMAGESDocument4 pages3D Reconstruction USING MULTIPLE 2D IMAGESKifayat UllahNo ratings yet

- PhaseCam3D Learning Phase Masks For Passive Single View Depth EstimationDocument12 pagesPhaseCam3D Learning Phase Masks For Passive Single View Depth EstimationJ SpencerNo ratings yet

- Escaner de TunelesDocument2 pagesEscaner de TunelesDiana CristinaNo ratings yet

- Leica LAS X Software Module Cast Iron Expert ENDocument2 pagesLeica LAS X Software Module Cast Iron Expert ENhaze.eslemNo ratings yet

- Wang Et Al. - 2020 - Research Status and Prospects On Plant Canopy Structure Measurement Using Visual Sensors Based On THDocument27 pagesWang Et Al. - 2020 - Research Status and Prospects On Plant Canopy Structure Measurement Using Visual Sensors Based On THgopal91carpenter_515No ratings yet

- BCStudio enDocument1 pageBCStudio enhbjbghjbnNo ratings yet

- Tracking of Industrial Objects by Using CAD Models: October 2007Document10 pagesTracking of Industrial Objects by Using CAD Models: October 2007thanhit08No ratings yet

- 2D23D Final Report Team B3Document31 pages2D23D Final Report Team B3Jeremy LeungNo ratings yet

- Nays2DH Examples EnglishDocument44 pagesNays2DH Examples EnglishPiere Christofer Salas HerreraNo ratings yet

- Paper 3Document6 pagesPaper 3Nishanthan KNo ratings yet

- Tutoriales 1 y 2Document44 pagesTutoriales 1 y 2Gabriela Fonseca cruzNo ratings yet

- Generating Synthetic Imagery For TRN Using PANGU and Unreal EngineDocument1 pageGenerating Synthetic Imagery For TRN Using PANGU and Unreal EngineShen GeNo ratings yet

- Development of A Stereo Vision Measurement Architecture For An Underwater RobotDocument4 pagesDevelopment of A Stereo Vision Measurement Architecture For An Underwater RobotCarlos Humberto LlanosNo ratings yet

- Submitted byDocument13 pagesSubmitted byVaishnavi BalikeNo ratings yet

- Brochure Geomagic Wrap SoftwareDocument4 pagesBrochure Geomagic Wrap SoftwarebehipiluwuNo ratings yet

- Shaders and SPIR-V: Mike BaileyDocument4 pagesShaders and SPIR-V: Mike Baileyaaron bairdNo ratings yet

- A Simple Method For Measuring Local Buckling of Thin PlatesDocument4 pagesA Simple Method For Measuring Local Buckling of Thin PlatesAbhishek VaggarNo ratings yet

- Intergration of LIDAR and Camera Data For 3D ReconstructionDocument2 pagesIntergration of LIDAR and Camera Data For 3D Reconstructioncos19890628No ratings yet

- Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization of Paper Web of Paper Web of Paper Web of Paper Web of Paper WebDocument1 pageWet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization of Paper Web of Paper Web of Paper Web of Paper Web of Paper WebWilton Wagner de CarvalhoNo ratings yet

- Implementation of 3D Scanner Using IR Distance Sensor Ijariie8280Document6 pagesImplementation of 3D Scanner Using IR Distance Sensor Ijariie8280MERYEM LAHBOUBNo ratings yet

- Li DeepFusion Lidar-Camera Deep Fusion For Multi-Modal 3D Object Detection CVPR 2022 PaperDocument10 pagesLi DeepFusion Lidar-Camera Deep Fusion For Multi-Modal 3D Object Detection CVPR 2022 PaperhaisabiNo ratings yet

- Real-Time Relative Mobile Target Positioning Using GPS-assisted Stereo VideogrammetryDocument11 pagesReal-Time Relative Mobile Target Positioning Using GPS-assisted Stereo VideogrammetryzaidalkabiNo ratings yet

- Moving Vehicle Detection and Speed Measurement in Video Sequence IJERTV2IS100920Document4 pagesMoving Vehicle Detection and Speed Measurement in Video Sequence IJERTV2IS100920aniket wadheNo ratings yet

- Key TRDocument10 pagesKey TRqwertyNo ratings yet

- Sfm-Net: Learning of Structure and Motion From Video: Sudheendra Vijayanarasimhan Susanna Ricco Cordelia SchmidDocument9 pagesSfm-Net: Learning of Structure and Motion From Video: Sudheendra Vijayanarasimhan Susanna Ricco Cordelia SchmidMalik Hashmat100% (1)

- MadhubalakichuDocument29 pagesMadhubalakichuHaaa Yh9No ratings yet

- Edge Detection Canny Algorithm Using Adaptive Threshold TechniqueDocument7 pagesEdge Detection Canny Algorithm Using Adaptive Threshold TechniqueDiana MaldonadoNo ratings yet

- Scan It, Mesh It, Surface It. in MinutesDocument4 pagesScan It, Mesh It, Surface It. in MinutesSam BaNo ratings yet

- CamodocalDocument9 pagesCamodocalherusyahputraNo ratings yet

- 3d Systems Wrap en Letter Web 2019-11-01Document4 pages3d Systems Wrap en Letter Web 2019-11-01Sam BaNo ratings yet

- Imaging and Image Representation: 2.1 Sensing LightDocument30 pagesImaging and Image Representation: 2.1 Sensing LightBerita TerkiniNo ratings yet

- Signal Processing: Yan Liu, Zhaoning You, Tiegang GaoDocument12 pagesSignal Processing: Yan Liu, Zhaoning You, Tiegang GaoAjnas MuhammedNo ratings yet

- Omer Mohamed Omer Ba-SaleemDocument36 pagesOmer Mohamed Omer Ba-SaleemHaider JuttNo ratings yet

- Tensor FPGADocument24 pagesTensor FPGAdreadrebirth2342No ratings yet

- Camera Based Spectacles For Visually Impaired (Camspects)Document6 pagesCamera Based Spectacles For Visually Impaired (Camspects)GRD JournalsNo ratings yet

- Pointseg: Real-Time Semantic Segmentation Based On 3D Lidar Point CloudDocument7 pagesPointseg: Real-Time Semantic Segmentation Based On 3D Lidar Point CloudOscar MarteNo ratings yet

- Stereomorph 3D Tutorial: How To Collect 3D Points and Curves Using A Stereo Camera SetupDocument67 pagesStereomorph 3D Tutorial: How To Collect 3D Points and Curves Using A Stereo Camera SetupInes Apituley SopacuaNo ratings yet

- P L S - Lecture-2Document31 pagesP L S - Lecture-2هیوا حسینNo ratings yet

- Deep Continuous FusionDocument16 pagesDeep Continuous FusionManoj BhatNo ratings yet

- Conference RA GCS - IPC 1Document1 pageConference RA GCS - IPC 1Smaranika SwainNo ratings yet

- Fixed Single-Camera 3D Laser Scanning: Giulio Zausa Ca' Foscari University of Venice 870040@stud - Unive.itDocument11 pagesFixed Single-Camera 3D Laser Scanning: Giulio Zausa Ca' Foscari University of Venice 870040@stud - Unive.itmfmaquinas2No ratings yet

- 3DRIMR 3D Reconstruction and Imaging Via Mmwave Radar Based On Deep LearningDocument8 pages3DRIMR 3D Reconstruction and Imaging Via Mmwave Radar Based On Deep LearningGuilherme OliveiraNo ratings yet

- An Effective Camera To LiDAR Spatiotemporal CalibrationDocument15 pagesAn Effective Camera To LiDAR Spatiotemporal CalibrationEdson KitaniNo ratings yet

- ZoomNet Part-Aware Adaptive Zooming Neural Network For 3D Object DetectionDocument9 pagesZoomNet Part-Aware Adaptive Zooming Neural Network For 3D Object DetectionbishNo ratings yet

- Opto-Digital Methods For Image Processing and Three-Dimensional ScanningDocument1 pageOpto-Digital Methods For Image Processing and Three-Dimensional ScanningRigoberto Juarez SalazarNo ratings yet

- Real-Time Color-Based SortingDocument5 pagesReal-Time Color-Based SortingaditdharkarNo ratings yet

- Siggraph2019 HydraDocument114 pagesSiggraph2019 Hydra王璨No ratings yet

- Stereo Vision IROS05Document7 pagesStereo Vision IROS05bidwejNo ratings yet

- A Simple, Low Cost, 3D Scanning System Using The Laser Light-Sectioning MethodDocument6 pagesA Simple, Low Cost, 3D Scanning System Using The Laser Light-Sectioning Methodsantoimam112No ratings yet

- TendenciasDocument3 pagesTendenciasdavidNo ratings yet

- Computer Graphics Challenges: - Suppose We Can Create A Precise Computer Representation of The 3D World - QuestionsDocument6 pagesComputer Graphics Challenges: - Suppose We Can Create A Precise Computer Representation of The 3D World - QuestionsD SNo ratings yet

- s8 Mechanical April 2011Document2 pagess8 Mechanical April 2011vvvasudevNo ratings yet

- Background Subtraction With Real-Time Semantic SegmentationDocument16 pagesBackground Subtraction With Real-Time Semantic SegmentationJEEVIT HNo ratings yet

- 2012 - A Benchmark For The Evaluation of RGB-D SLAM Systems - SturmDocument8 pages2012 - A Benchmark For The Evaluation of RGB-D SLAM Systems - SturmRiriNo ratings yet

- Poster Presentation Prateek RastogiDocument1 pagePoster Presentation Prateek RastogiprateekNo ratings yet

- Master ThesisDocument77 pagesMaster ThesisAymen NasriNo ratings yet

- Anisimova VulkanAndAnimation.4pp PDFDocument5 pagesAnisimova VulkanAndAnimation.4pp PDFVladimir ZaltNo ratings yet

- An Application Designed For Ballistic Calculations of Detected ObjectsDocument2 pagesAn Application Designed For Ballistic Calculations of Detected ObjectsAddy EmmanuelNo ratings yet

- Efficient and Robust LiDAR-Based End-to-End NavigationDocument8 pagesEfficient and Robust LiDAR-Based End-to-End NavigationYifeng CaoNo ratings yet

- Julia Dault: Born 1977, Toronto Lives and Works in New YorkDocument4 pagesJulia Dault: Born 1977, Toronto Lives and Works in New YorkUn BigoteNo ratings yet

- Course Module EL. 107 Week 2Document22 pagesCourse Module EL. 107 Week 2Joevannie AceraNo ratings yet

- Seven Refractories Aluminio PDFDocument15 pagesSeven Refractories Aluminio PDFjose.figueroa@foseco.comNo ratings yet

- System Wiring DiagramsDocument87 pagesSystem Wiring Diagramshcastens3989100% (1)

- Eng 101SC ReviewMLAWorksheets ReviewPracticeWorksCited PDFDocument38 pagesEng 101SC ReviewMLAWorksheets ReviewPracticeWorksCited PDFjeanninestankoNo ratings yet

- Sportsmen and TechnologyDocument11 pagesSportsmen and TechnologyAkshita KapilNo ratings yet

- Call For Abstracts: 2nd Victim Support Asia ConferenceDocument2 pagesCall For Abstracts: 2nd Victim Support Asia ConferenceAnkit YadavNo ratings yet

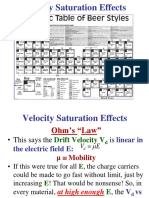

- Transport4 - High Electric Fields - Velocity SaturationDocument16 pagesTransport4 - High Electric Fields - Velocity SaturationMạnh Huy BùiNo ratings yet

- Pigment Volume Concentration Part IDocument5 pagesPigment Volume Concentration Part IEmilio HipolaNo ratings yet

- Pcc-67t8o2qk-Dci ReceiptDocument2 pagesPcc-67t8o2qk-Dci ReceiptDeejay KingNo ratings yet

- Grant Noble - The Trader's EdgeDocument128 pagesGrant Noble - The Trader's EdgeneerajmattaNo ratings yet

- The Carrefour AssignmentDocument16 pagesThe Carrefour AssignmentMohit MalviyaNo ratings yet

- Pediatric Hospital PresentationDocument61 pagesPediatric Hospital PresentationLindsay Khryss Cendy MadahanNo ratings yet

- LP Maximization Graphical Method 2021Document28 pagesLP Maximization Graphical Method 2021liesly buticNo ratings yet

- Tizon, R. - Patient History, Gordon's, Lab Results, Drug StudyDocument10 pagesTizon, R. - Patient History, Gordon's, Lab Results, Drug StudyRoyce Vincent TizonNo ratings yet

- Indebted Part 2 The Virgin The Bad Boy Sadie BlackDocument296 pagesIndebted Part 2 The Virgin The Bad Boy Sadie BlackVidhya R100% (2)

- Week 7 Lab Tutorial Using ThingsBoardDocument8 pagesWeek 7 Lab Tutorial Using ThingsBoard2022616436No ratings yet

- All of Managers Have Entered The Meeting Room, Except The President Director and Personnel ManagerDocument7 pagesAll of Managers Have Entered The Meeting Room, Except The President Director and Personnel ManagerALIFIA PUSPITANo ratings yet

- 1 Analytic FunctionDocument3 pages1 Analytic FunctionrobNo ratings yet

- The Purpose and Nature of External AuditDocument9 pagesThe Purpose and Nature of External AuditFeb OktafihartoNo ratings yet

- John Cruise I Kelly Kordes Anton - Adobe Indesign Cs3 U PraksiDocument270 pagesJohn Cruise I Kelly Kordes Anton - Adobe Indesign Cs3 U PraksiD-JOPNo ratings yet

- Festivals of India Impact of Festivals On EnvironmentDocument27 pagesFestivals of India Impact of Festivals On EnvironmentJasvinder Singh80% (30)

- 2 Ethico-legal-POWERPOINT-BASIC As of January 12, 2009 (1) .Document81 pages2 Ethico-legal-POWERPOINT-BASIC As of January 12, 2009 (1) .Crystal Mae Castrodes Daquipil100% (1)

- Collibra Prescriptive Path v2Document4 pagesCollibra Prescriptive Path v2AhamedSharifNo ratings yet

- Mummified Fetus in CowDocument2 pagesMummified Fetus in CowgnpobsNo ratings yet

- Content On New Born NNB&PNBDocument39 pagesContent On New Born NNB&PNBSabita JanaNo ratings yet

- Drainage Handbook SpecificationsDocument57 pagesDrainage Handbook Specificationshussainelarabi100% (1)

- 29primary AngleClosure GlauDocument9 pages29primary AngleClosure GlauShari' Si WahyuNo ratings yet

- Ethnobotany AssignmentDocument11 pagesEthnobotany AssignmentMelissa KittycatNo ratings yet

Output

Output

Uploaded by

abhishek509.pOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Output

Output

Uploaded by

abhishek509.pCopyright:

Available Formats

See discussions, stats, and author profiles for this publication at: https://www.researchgate.

net/publication/378234606

A High Frame Rate Stereovision Tracking System

Poster · May 2008

DOI: 10.13140/RG.2.2.12763.95526

CITATIONS READS

0 7

1 author:

Siraj Sabihuddin

W3NG Inc.

18 PUBLICATIONS 345 CITATIONS

SEE PROFILE

All content following this page was uploaded by Siraj Sabihuddin on 15 February 2024.

The user has requested enhancement of the downloaded file.

F a s tT ra c k

A High Frame Rate Stereovision Tracking System

Jamin Islam1, Siraj Sabihuddin1, W. James MacLean1, Valeri Kirischian2 ,Vadim Geurkov2, Lev Kirischian2, Michael Belshaw3, Michael Greenspan3

1

Dept. of Electrical & Computer Engineering, University of Toronto; 2Dept. of Electrical & Computer Engineering, Ryerson University; 3Dept. of Electrical & Computer Engineering, Queen’s University

3) Rectification

Project Goals: To construct a

stereo vision system capable of Transforms a pair of stereo images

Hardware Design

tracking objects at 200fps. into a parallel camera geometry so ● Storage of N scanlines ● Inverse Warp

that corresponding point features in into dual-ported BRAMs computes warped

3D will lie on the same scanline in camera

data

camera control ● Provides 2x2 region of coordinate location

Motivation: Remote satellite both images. Address Generator

start

pixels for interpolation via homographies

● Computes the ideal

original

Contains 2 BRAMs to pixel intensity for a

capture, high speed motion

●

coordinates

Pixel Sync

Reduces the stereo correspondence Buffer Inverse Warp Control

alternate read for given warped

stereo extraction coordinate location

tracking. problem to a one-dimensional warped

coordinates

● Provides read signal

using Bilinear

search. read

address

Out of Range

OOR &

coefficients

& address to output Interpolation

2x2 pixel OOR &

computed disparities

region coefficients

HL & HR are 3x3 homographies rectification

data

stereo

data

Rectification-to-

which transform the image planes

System Components

Bilinear Interpolator

Stereo Interface

rectification disparity read

and make them collinear & control control

horizontal

1) Stereo Imaging 2) Calibration 4) Stereo 5) Tracking Homographies are calculated

Un-rectified

using calibration parameters Performance

Hardware 3) Rectification Extraction and implemented in hardware Stereo

as a 1st-order Taylor Series Resolution:

640x480 pixels Images

polynomial P

Left Images Right Images

Freq. (MHz) Frames/Sec

Images

Acquired

Images

warped

Depth

Acquired

Object

Pose 31.25 50.862 Result:

Acquired 62.50 101.72 Rectified

125.0 203.45 Stereo

HL HR

Images

CL CR

1) Stereo Imaging & Hardware Platform 4) Stereo Extraction

200fps Stereo Frame Grabber Hardware Design Stereo extraction is based on a Maximum Likelihood

USB Dynamic Programming (DPML) algorithm developed

by Cox et al.

μC Algorithm

200 FPS 200 FPS 1) Initialize cost and match matrices.

Sensor Xilinx Xilinx Sensor 2) Compute the cost and match matrix values b/w all

FPGA FPGA

XC3S200 XC3S200

right and left image pixels in a scanline (OC/NOC).

3) Compute optimal stereo disparities via a backward

Control of two Parameter Real-time High speed VGA DAC VGA DAC pass through the match matrix.

200fps image control via Visualization image comm. High Speed Interface 4) Repeat for all scanlines in the image.

sensors. PC over USB. via VGA DACs. with AP1100.

Parallelization

● Exploit anti-diagonal structure of DPML cost

AP1100 FPGA Platform matrix for SIMD parallelization

● Pixel level pipelining to improve throughput and

High Speed Interface

and Amirix PCI Interface clock frequency.

SRAM SRAM ● Interleaving to pipeline forward and backward

Bank Bank

Xilinx phases of algorithm – scanline level pipelining.

FPGA

XC2VP100

Performance 320x240 ● 1.24 fps

SW Result:

640x480 ● 0.18 fps

Processed data Standalone system

The figures to the right

320x240 ● 248 fps

Dense

shows depth estimation HW

stored in SRAM that operates

results at 128 pixel max.

640x480 ● 123 fps Disparity

memory banks. without PC. 320x240 ● 200 fps Map

disparity and the indicated 640x480 ● 200 fps Goal Right Input Image Ground Truth HW Result

resolutions.

2) Calibration 5) Tracking

Calibration is the process of Tracking with Iterative Range Data

Model

determining the position and Closest Point (ICP) From Stereo Object's

orientation of the cameras Calibration Extraction

Pre-filter Data Data Nearest Point

Pose

with respect to a world reference 1) Find correspondences between model Transform SVD

Parameters & data using last pose estimate -

ROI

Points Points

Neighbor

Pairs

system.

Intrinsic Parameters: Nearest Neighbor (NN).

Calibration determines values Focal Length 2) Find transform using correspondences - Transform

for two types of parameters: Principal Point Singular Value Decomposition (SVD)

3) Apply transform to update data 3250 Pre-filter / ROI NN Approach

Intrinsic & Extrinsic Skew Coefficient 200fps goal 3000

Radial Distortion 4) Repeat 10 times. T

Fixed point 16bit 2750 ● Initially, data is ● Parallel brute force

2500

filtered using region approach.

Number of NN cyc/sec

FPGA @ 100Mhz

Tangential Distortion 2250

2000

of interest based on

3040

1750 inferred XY SVD

Extrinsic Parameters: NN Brute Force 1500

1250

Using integers

coordinates

● Data is then

●

SVD performed by using Microblaze μC.

A checkerboard pattern (as shown Rotation Speed Comparison

1000

750

x86 @ 3.4ghz

converted to world ●

To decrease overhead on μC the

on the right) is used to discover Translation 500

250

188 95 XYZ form and a formation of the covariance matrix is

Compare using 2048 bounding box is used performed in hardware.

these calibration parameters for 0

CPU FPGA-1 cmp FPGA-32 to further sub-sample

each camera in the stereo pair. model points & 512 data. cmp

and invalid points are HW CPU

points. rejected.

View publication stats

You might also like

- 5 Steps To CPA Profits PDFDocument40 pages5 Steps To CPA Profits PDFimtool0% (1)

- 3D Reconstruction USING MULTIPLE 2D IMAGESDocument4 pages3D Reconstruction USING MULTIPLE 2D IMAGESKifayat UllahNo ratings yet

- PhaseCam3D Learning Phase Masks For Passive Single View Depth EstimationDocument12 pagesPhaseCam3D Learning Phase Masks For Passive Single View Depth EstimationJ SpencerNo ratings yet

- Escaner de TunelesDocument2 pagesEscaner de TunelesDiana CristinaNo ratings yet

- Leica LAS X Software Module Cast Iron Expert ENDocument2 pagesLeica LAS X Software Module Cast Iron Expert ENhaze.eslemNo ratings yet

- Wang Et Al. - 2020 - Research Status and Prospects On Plant Canopy Structure Measurement Using Visual Sensors Based On THDocument27 pagesWang Et Al. - 2020 - Research Status and Prospects On Plant Canopy Structure Measurement Using Visual Sensors Based On THgopal91carpenter_515No ratings yet

- BCStudio enDocument1 pageBCStudio enhbjbghjbnNo ratings yet

- Tracking of Industrial Objects by Using CAD Models: October 2007Document10 pagesTracking of Industrial Objects by Using CAD Models: October 2007thanhit08No ratings yet

- 2D23D Final Report Team B3Document31 pages2D23D Final Report Team B3Jeremy LeungNo ratings yet

- Nays2DH Examples EnglishDocument44 pagesNays2DH Examples EnglishPiere Christofer Salas HerreraNo ratings yet

- Paper 3Document6 pagesPaper 3Nishanthan KNo ratings yet

- Tutoriales 1 y 2Document44 pagesTutoriales 1 y 2Gabriela Fonseca cruzNo ratings yet

- Generating Synthetic Imagery For TRN Using PANGU and Unreal EngineDocument1 pageGenerating Synthetic Imagery For TRN Using PANGU and Unreal EngineShen GeNo ratings yet

- Development of A Stereo Vision Measurement Architecture For An Underwater RobotDocument4 pagesDevelopment of A Stereo Vision Measurement Architecture For An Underwater RobotCarlos Humberto LlanosNo ratings yet

- Submitted byDocument13 pagesSubmitted byVaishnavi BalikeNo ratings yet

- Brochure Geomagic Wrap SoftwareDocument4 pagesBrochure Geomagic Wrap SoftwarebehipiluwuNo ratings yet

- Shaders and SPIR-V: Mike BaileyDocument4 pagesShaders and SPIR-V: Mike Baileyaaron bairdNo ratings yet

- A Simple Method For Measuring Local Buckling of Thin PlatesDocument4 pagesA Simple Method For Measuring Local Buckling of Thin PlatesAbhishek VaggarNo ratings yet

- Intergration of LIDAR and Camera Data For 3D ReconstructionDocument2 pagesIntergration of LIDAR and Camera Data For 3D Reconstructioncos19890628No ratings yet

- Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization of Paper Web of Paper Web of Paper Web of Paper Web of Paper WebDocument1 pageWet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization Wet-End Characterization of Paper Web of Paper Web of Paper Web of Paper Web of Paper WebWilton Wagner de CarvalhoNo ratings yet

- Implementation of 3D Scanner Using IR Distance Sensor Ijariie8280Document6 pagesImplementation of 3D Scanner Using IR Distance Sensor Ijariie8280MERYEM LAHBOUBNo ratings yet

- Li DeepFusion Lidar-Camera Deep Fusion For Multi-Modal 3D Object Detection CVPR 2022 PaperDocument10 pagesLi DeepFusion Lidar-Camera Deep Fusion For Multi-Modal 3D Object Detection CVPR 2022 PaperhaisabiNo ratings yet

- Real-Time Relative Mobile Target Positioning Using GPS-assisted Stereo VideogrammetryDocument11 pagesReal-Time Relative Mobile Target Positioning Using GPS-assisted Stereo VideogrammetryzaidalkabiNo ratings yet

- Moving Vehicle Detection and Speed Measurement in Video Sequence IJERTV2IS100920Document4 pagesMoving Vehicle Detection and Speed Measurement in Video Sequence IJERTV2IS100920aniket wadheNo ratings yet

- Key TRDocument10 pagesKey TRqwertyNo ratings yet

- Sfm-Net: Learning of Structure and Motion From Video: Sudheendra Vijayanarasimhan Susanna Ricco Cordelia SchmidDocument9 pagesSfm-Net: Learning of Structure and Motion From Video: Sudheendra Vijayanarasimhan Susanna Ricco Cordelia SchmidMalik Hashmat100% (1)

- MadhubalakichuDocument29 pagesMadhubalakichuHaaa Yh9No ratings yet

- Edge Detection Canny Algorithm Using Adaptive Threshold TechniqueDocument7 pagesEdge Detection Canny Algorithm Using Adaptive Threshold TechniqueDiana MaldonadoNo ratings yet

- Scan It, Mesh It, Surface It. in MinutesDocument4 pagesScan It, Mesh It, Surface It. in MinutesSam BaNo ratings yet

- CamodocalDocument9 pagesCamodocalherusyahputraNo ratings yet

- 3d Systems Wrap en Letter Web 2019-11-01Document4 pages3d Systems Wrap en Letter Web 2019-11-01Sam BaNo ratings yet

- Imaging and Image Representation: 2.1 Sensing LightDocument30 pagesImaging and Image Representation: 2.1 Sensing LightBerita TerkiniNo ratings yet

- Signal Processing: Yan Liu, Zhaoning You, Tiegang GaoDocument12 pagesSignal Processing: Yan Liu, Zhaoning You, Tiegang GaoAjnas MuhammedNo ratings yet

- Omer Mohamed Omer Ba-SaleemDocument36 pagesOmer Mohamed Omer Ba-SaleemHaider JuttNo ratings yet

- Tensor FPGADocument24 pagesTensor FPGAdreadrebirth2342No ratings yet

- Camera Based Spectacles For Visually Impaired (Camspects)Document6 pagesCamera Based Spectacles For Visually Impaired (Camspects)GRD JournalsNo ratings yet

- Pointseg: Real-Time Semantic Segmentation Based On 3D Lidar Point CloudDocument7 pagesPointseg: Real-Time Semantic Segmentation Based On 3D Lidar Point CloudOscar MarteNo ratings yet

- Stereomorph 3D Tutorial: How To Collect 3D Points and Curves Using A Stereo Camera SetupDocument67 pagesStereomorph 3D Tutorial: How To Collect 3D Points and Curves Using A Stereo Camera SetupInes Apituley SopacuaNo ratings yet

- P L S - Lecture-2Document31 pagesP L S - Lecture-2هیوا حسینNo ratings yet

- Deep Continuous FusionDocument16 pagesDeep Continuous FusionManoj BhatNo ratings yet

- Conference RA GCS - IPC 1Document1 pageConference RA GCS - IPC 1Smaranika SwainNo ratings yet

- Fixed Single-Camera 3D Laser Scanning: Giulio Zausa Ca' Foscari University of Venice 870040@stud - Unive.itDocument11 pagesFixed Single-Camera 3D Laser Scanning: Giulio Zausa Ca' Foscari University of Venice 870040@stud - Unive.itmfmaquinas2No ratings yet

- 3DRIMR 3D Reconstruction and Imaging Via Mmwave Radar Based On Deep LearningDocument8 pages3DRIMR 3D Reconstruction and Imaging Via Mmwave Radar Based On Deep LearningGuilherme OliveiraNo ratings yet

- An Effective Camera To LiDAR Spatiotemporal CalibrationDocument15 pagesAn Effective Camera To LiDAR Spatiotemporal CalibrationEdson KitaniNo ratings yet

- ZoomNet Part-Aware Adaptive Zooming Neural Network For 3D Object DetectionDocument9 pagesZoomNet Part-Aware Adaptive Zooming Neural Network For 3D Object DetectionbishNo ratings yet

- Opto-Digital Methods For Image Processing and Three-Dimensional ScanningDocument1 pageOpto-Digital Methods For Image Processing and Three-Dimensional ScanningRigoberto Juarez SalazarNo ratings yet

- Real-Time Color-Based SortingDocument5 pagesReal-Time Color-Based SortingaditdharkarNo ratings yet

- Siggraph2019 HydraDocument114 pagesSiggraph2019 Hydra王璨No ratings yet

- Stereo Vision IROS05Document7 pagesStereo Vision IROS05bidwejNo ratings yet

- A Simple, Low Cost, 3D Scanning System Using The Laser Light-Sectioning MethodDocument6 pagesA Simple, Low Cost, 3D Scanning System Using The Laser Light-Sectioning Methodsantoimam112No ratings yet

- TendenciasDocument3 pagesTendenciasdavidNo ratings yet

- Computer Graphics Challenges: - Suppose We Can Create A Precise Computer Representation of The 3D World - QuestionsDocument6 pagesComputer Graphics Challenges: - Suppose We Can Create A Precise Computer Representation of The 3D World - QuestionsD SNo ratings yet

- s8 Mechanical April 2011Document2 pagess8 Mechanical April 2011vvvasudevNo ratings yet

- Background Subtraction With Real-Time Semantic SegmentationDocument16 pagesBackground Subtraction With Real-Time Semantic SegmentationJEEVIT HNo ratings yet

- 2012 - A Benchmark For The Evaluation of RGB-D SLAM Systems - SturmDocument8 pages2012 - A Benchmark For The Evaluation of RGB-D SLAM Systems - SturmRiriNo ratings yet

- Poster Presentation Prateek RastogiDocument1 pagePoster Presentation Prateek RastogiprateekNo ratings yet

- Master ThesisDocument77 pagesMaster ThesisAymen NasriNo ratings yet

- Anisimova VulkanAndAnimation.4pp PDFDocument5 pagesAnisimova VulkanAndAnimation.4pp PDFVladimir ZaltNo ratings yet

- An Application Designed For Ballistic Calculations of Detected ObjectsDocument2 pagesAn Application Designed For Ballistic Calculations of Detected ObjectsAddy EmmanuelNo ratings yet

- Efficient and Robust LiDAR-Based End-to-End NavigationDocument8 pagesEfficient and Robust LiDAR-Based End-to-End NavigationYifeng CaoNo ratings yet

- Julia Dault: Born 1977, Toronto Lives and Works in New YorkDocument4 pagesJulia Dault: Born 1977, Toronto Lives and Works in New YorkUn BigoteNo ratings yet

- Course Module EL. 107 Week 2Document22 pagesCourse Module EL. 107 Week 2Joevannie AceraNo ratings yet

- Seven Refractories Aluminio PDFDocument15 pagesSeven Refractories Aluminio PDFjose.figueroa@foseco.comNo ratings yet

- System Wiring DiagramsDocument87 pagesSystem Wiring Diagramshcastens3989100% (1)

- Eng 101SC ReviewMLAWorksheets ReviewPracticeWorksCited PDFDocument38 pagesEng 101SC ReviewMLAWorksheets ReviewPracticeWorksCited PDFjeanninestankoNo ratings yet

- Sportsmen and TechnologyDocument11 pagesSportsmen and TechnologyAkshita KapilNo ratings yet

- Call For Abstracts: 2nd Victim Support Asia ConferenceDocument2 pagesCall For Abstracts: 2nd Victim Support Asia ConferenceAnkit YadavNo ratings yet

- Transport4 - High Electric Fields - Velocity SaturationDocument16 pagesTransport4 - High Electric Fields - Velocity SaturationMạnh Huy BùiNo ratings yet

- Pigment Volume Concentration Part IDocument5 pagesPigment Volume Concentration Part IEmilio HipolaNo ratings yet

- Pcc-67t8o2qk-Dci ReceiptDocument2 pagesPcc-67t8o2qk-Dci ReceiptDeejay KingNo ratings yet

- Grant Noble - The Trader's EdgeDocument128 pagesGrant Noble - The Trader's EdgeneerajmattaNo ratings yet

- The Carrefour AssignmentDocument16 pagesThe Carrefour AssignmentMohit MalviyaNo ratings yet

- Pediatric Hospital PresentationDocument61 pagesPediatric Hospital PresentationLindsay Khryss Cendy MadahanNo ratings yet

- LP Maximization Graphical Method 2021Document28 pagesLP Maximization Graphical Method 2021liesly buticNo ratings yet

- Tizon, R. - Patient History, Gordon's, Lab Results, Drug StudyDocument10 pagesTizon, R. - Patient History, Gordon's, Lab Results, Drug StudyRoyce Vincent TizonNo ratings yet

- Indebted Part 2 The Virgin The Bad Boy Sadie BlackDocument296 pagesIndebted Part 2 The Virgin The Bad Boy Sadie BlackVidhya R100% (2)

- Week 7 Lab Tutorial Using ThingsBoardDocument8 pagesWeek 7 Lab Tutorial Using ThingsBoard2022616436No ratings yet

- All of Managers Have Entered The Meeting Room, Except The President Director and Personnel ManagerDocument7 pagesAll of Managers Have Entered The Meeting Room, Except The President Director and Personnel ManagerALIFIA PUSPITANo ratings yet

- 1 Analytic FunctionDocument3 pages1 Analytic FunctionrobNo ratings yet

- The Purpose and Nature of External AuditDocument9 pagesThe Purpose and Nature of External AuditFeb OktafihartoNo ratings yet

- John Cruise I Kelly Kordes Anton - Adobe Indesign Cs3 U PraksiDocument270 pagesJohn Cruise I Kelly Kordes Anton - Adobe Indesign Cs3 U PraksiD-JOPNo ratings yet

- Festivals of India Impact of Festivals On EnvironmentDocument27 pagesFestivals of India Impact of Festivals On EnvironmentJasvinder Singh80% (30)

- 2 Ethico-legal-POWERPOINT-BASIC As of January 12, 2009 (1) .Document81 pages2 Ethico-legal-POWERPOINT-BASIC As of January 12, 2009 (1) .Crystal Mae Castrodes Daquipil100% (1)

- Collibra Prescriptive Path v2Document4 pagesCollibra Prescriptive Path v2AhamedSharifNo ratings yet

- Mummified Fetus in CowDocument2 pagesMummified Fetus in CowgnpobsNo ratings yet

- Content On New Born NNB&PNBDocument39 pagesContent On New Born NNB&PNBSabita JanaNo ratings yet

- Drainage Handbook SpecificationsDocument57 pagesDrainage Handbook Specificationshussainelarabi100% (1)

- 29primary AngleClosure GlauDocument9 pages29primary AngleClosure GlauShari' Si WahyuNo ratings yet

- Ethnobotany AssignmentDocument11 pagesEthnobotany AssignmentMelissa KittycatNo ratings yet