Professional Documents

Culture Documents

09-Advanced Computer Architecture

09-Advanced Computer Architecture

Uploaded by

sudhakar kOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

09-Advanced Computer Architecture

09-Advanced Computer Architecture

Uploaded by

sudhakar kCopyright:

Available Formats

www.jntuworld.

com

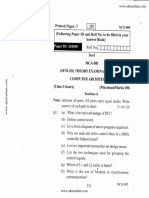

R09

Code No: D109110509

JAWAHARLAL NEHRU TECHNOLOGICAL UNIVERSITY HYDERABAD

M.Tech I Semester Regular Examinations March 2010

ADVANCED COMPUTER ARCHITECTURE

(COMPUTER SCIENCE)

Time: 3hours Max.Marks:60

Answer any five questions

All questions carry equal marks

---

1. a) Explain Amdahl’s Law.

b) Explain various operations in the instruction set.

2. a) Explain the basics of RISC instruction set.

b) Explain the implementation of a RISC instruction set.

3. a) Explain the first miss penalty reduction technique in multilevel caches.

b) Suppose that in 1000 memory references there are 40 misses in the first-level

L D

cache and 20 misses in the second level cache. What are the various miss rates?

Assume the miss penalty from the L2 cache to memory is 100 clock cycles, the hit

time of the L2 cache is 10 clock cycles, the hit time of L1 is 1 clock cycle, and

R

there are 1.5 memory references per instruction, what is the average memory

access time and the average stall cycles per instruction? Ignore the impact of

writes.

O

W

4. Explain Dynamic scheduling using Tomasulo’s approach.

U

5. a) Explain hardware versus software speculation mechanisms.

b) Briefly explain loop unrolling and scheduling.

6.

N T

Explain multiprocessor cache coherence.

7. a)

b)

8. a)

J

Explain about Ethernet, the local area network.

Explain the cost and performance of a cluster for transaction processing.

Explain the architecture of Trimedia TM32.

b) Define cluster? Give designing principles of cluster?

******

www.jntuworld.com

You might also like

- Az 204 PDFDocument16 pagesAz 204 PDFAshvini MahajanNo ratings yet

- 09 - Distributed SystemsDocument1 page09 - Distributed Systemssudhakar kNo ratings yet

- 09-Advanced Computer ArchitectureDocument1 page09-Advanced Computer Architecturesudhakar kNo ratings yet

- Computer NetworksDocument2 pagesComputer Networkssudhakar kNo ratings yet

- 09-Advanced Computer ArchitectureDocument1 page09-Advanced Computer Architecturesudhakar kNo ratings yet

- 09-Embedded SystemsDocument1 page09-Embedded Systemssudhakar kNo ratings yet

- 09-Fundamentals of Real Time SystemsDocument1 page09-Fundamentals of Real Time Systemssudhakar kNo ratings yet

- Short. 1: Printed ftcs-505 (Foltowing To Filled in Your Answer RollDocument4 pagesShort. 1: Printed ftcs-505 (Foltowing To Filled in Your Answer RollIshita SharmaNo ratings yet

- R09-Network ProgrammingDocument1 pageR09-Network Programmingsudhakar kNo ratings yet

- Nr-Advanced Computer ArchitechurDocument1 pageNr-Advanced Computer Architechursudhakar kNo ratings yet

- Mscit 102Document2 pagesMscit 102api-3782519No ratings yet

- Computer System ArchitectureDocument1 pageComputer System Architecturesudhakar kNo ratings yet

- Adhnt 101Document2 pagesAdhnt 101api-3782519No ratings yet

- r7410407 Operating SystemsDocument4 pagesr7410407 Operating SystemsShoaib AhmedNo ratings yet

- 09-Embedded System DesignDocument1 page09-Embedded System Designsudhakar kNo ratings yet

- 031323Document2 pages031323Chetan GuliaNo ratings yet

- Microcontroller EndsemDocument1 pageMicrocontroller EndsemSwarnashree RoyNo ratings yet

- Cao Previous QNDocument9 pagesCao Previous QNanusha deviNo ratings yet

- 09-Network Security-1Document1 page09-Network Security-1sudhakar kNo ratings yet

- IET DAVV 2014 ComDocument15 pagesIET DAVV 2014 Comjainam dudeNo ratings yet

- 09-Internet WorkingDocument1 page09-Internet Workingsudhakar kNo ratings yet

- 09-Adhoc and Sensor NetworksDocument1 page09-Adhoc and Sensor Networkssudhakar kNo ratings yet

- 4th Sem. / Comp. Engg. Subject: Computer OrganizationDocument2 pages4th Sem. / Comp. Engg. Subject: Computer Organizationmukulranag4No ratings yet

- 9D55101 Advanced DSP ApplicationsDocument1 page9D55101 Advanced DSP ApplicationssubbuNo ratings yet

- 09-Information Security-1Document1 page09-Information Security-1sudhakar kNo ratings yet

- 4th Sem. / Comp / IT Subject: Computer OrganizationDocument2 pages4th Sem. / Comp / IT Subject: Computer Organizationmukulranag4No ratings yet

- MCS 022 June2010 June2023Document80 pagesMCS 022 June2010 June2023kalpanajaiswal2005No ratings yet

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Document7 pages2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraNo ratings yet

- X62303 (CS1251 Cs1202a)Document2 pagesX62303 (CS1251 Cs1202a)tamilarasi87thulasiNo ratings yet

- A0406 MachatronicsDocument1 pageA0406 Machatronicssudhakar kNo ratings yet

- I MCSE-011 I MCA (Revised) Term-End Examination 1:3 June, 2018Document2 pagesI MCSE-011 I MCA (Revised) Term-End Examination 1:3 June, 2018rayNo ratings yet

- S3 Bca 2017 Reg - SupplyDocument9 pagesS3 Bca 2017 Reg - SupplyLeslie QwerNo ratings yet

- S3 Bca 2016 Reg - SupplyDocument8 pagesS3 Bca 2016 Reg - SupplyLeslie QwerNo ratings yet

- MP (4th) Dec11Document1 pageMP (4th) Dec11Sahil .S.PawarNo ratings yet

- MP (4th) Dec11Document1 pageMP (4th) Dec11Sahil .S.PawarNo ratings yet

- Embedded System DesignDocument23 pagesEmbedded System DesignlosssssssssNo ratings yet

- Network 2019 QPDocument2 pagesNetwork 2019 QPafhfadNo ratings yet

- Btech Cse 5 Sem Operating Systems pcs5g001 2020Document2 pagesBtech Cse 5 Sem Operating Systems pcs5g001 2020Vibrant PixelsNo ratings yet

- COA Question PaperDocument2 pagesCOA Question PaperwahidNo ratings yet

- 1 - Computer System Overview, Operating System Overview PDFDocument2 pages1 - Computer System Overview, Operating System Overview PDFRemon Hanna Wadie YoussefNo ratings yet

- S19 Operating SystemDocument31 pagesS19 Operating SystemKamini SalunkheNo ratings yet

- EC206 CO Modelqn2 Ktustudents - inDocument3 pagesEC206 CO Modelqn2 Ktustudents - ingpuonlineNo ratings yet

- Paper ID (A0406)Document2 pagesPaper ID (A0406)Anonymous ey6J2bNo ratings yet

- Contain?: of A of inDocument3 pagesContain?: of A of inanjaniit12No ratings yet

- Btech Cs 4 Sem Operating System ncs401 2019Document2 pagesBtech Cs 4 Sem Operating System ncs401 2019Vishal Kumar SharmaNo ratings yet

- Co Question BankDocument6 pagesCo Question Banksubramanyam62No ratings yet

- Computer Network 2021Document2 pagesComputer Network 2021manoj kumarNo ratings yet

- 09-Algorithms For Vlsi Design AutomationDocument1 page09-Algorithms For Vlsi Design AutomationroobetNo ratings yet

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksCigi ManojNo ratings yet

- B3607-Real Time Operating SystemsDocument1 pageB3607-Real Time Operating Systemssudhakar kNo ratings yet

- It 2018Document46 pagesIt 2018Rehan TariqNo ratings yet

- KCS401 - OS - Final Question BankDocument6 pagesKCS401 - OS - Final Question Bankparidhiagarwal129No ratings yet

- Ia2 QPDocument2 pagesIa2 QPravirayappaNo ratings yet

- MCS 012 June2010 June2023Document120 pagesMCS 012 June2010 June2023sorcererstuffNo ratings yet

- Operating System Sample Paper 5th Semester MSBTE Diploma in Computer Engineering GroupDocument2 pagesOperating System Sample Paper 5th Semester MSBTE Diploma in Computer Engineering GroupSanjay Dudani69% (13)

- Comp. GraphicsDocument2 pagesComp. GraphicsAnnu AttriNo ratings yet

- B5802 - Embedded SystemsDocument1 pageB5802 - Embedded Systemssudhakar kNo ratings yet

- Natural Computing with Python: Learn to implement genetic and evolutionary algorithms to solve problems in a pythonic wayFrom EverandNatural Computing with Python: Learn to implement genetic and evolutionary algorithms to solve problems in a pythonic wayNo ratings yet

- Concurrent, Real-Time and Distributed Programming in Java: Threads, RTSJ and RMIFrom EverandConcurrent, Real-Time and Distributed Programming in Java: Threads, RTSJ and RMINo ratings yet

- NR Computer CommunicationsDocument1 pageNR Computer Communicationssudhakar kNo ratings yet

- R09-Wireless Communications and NetworksDocument1 pageR09-Wireless Communications and Networkssudhakar kNo ratings yet

- R09-Wireless Lans and PansDocument1 pageR09-Wireless Lans and Panssudhakar kNo ratings yet

- R09-Biomedical Signal ProcessingDocument1 pageR09-Biomedical Signal Processingsudhakar kNo ratings yet

- R09-Advanced Digital Signal Processing - SSPDocument2 pagesR09-Advanced Digital Signal Processing - SSPsudhakar kNo ratings yet

- R09-Random Processes and Time Series AnalysisDocument1 pageR09-Random Processes and Time Series Analysissudhakar kNo ratings yet

- 09-Advanced Chemical Reaction EngineeringDocument1 page09-Advanced Chemical Reaction Engineeringsudhakar kNo ratings yet

- 09-Energy Conservation SystemsDocument1 page09-Energy Conservation Systemssudhakar kNo ratings yet

- 09-Engineering Analysis of Flight VehiclesDocument1 page09-Engineering Analysis of Flight Vehiclessudhakar kNo ratings yet

- 09-Advanced Computer GraphicsDocument1 page09-Advanced Computer Graphicssudhakar kNo ratings yet

- Computer NetworksDocument2 pagesComputer Networkssudhakar kNo ratings yet

- A0302-Molecular Biology & VirologyDocument1 pageA0302-Molecular Biology & Virologysudhakar kNo ratings yet

- b5402 HVDC TransmissionDocument1 pageb5402 HVDC Transmissionsudhakar kNo ratings yet

- Nr-R09-Power Electroniccontrol of DC DrivesDocument1 pageNr-R09-Power Electroniccontrol of DC Drivessudhakar kNo ratings yet

- Nr-R09-Machine Modelling and AnalysisDocument1 pageNr-R09-Machine Modelling and Analysissudhakar kNo ratings yet

- 09-Network Security-1Document1 page09-Network Security-1sudhakar kNo ratings yet

- R09-Network ProgrammingDocument1 pageR09-Network Programmingsudhakar kNo ratings yet

- Nr-R09-Advanced Instrumentation SystemsDocument1 pageNr-R09-Advanced Instrumentation Systemssudhakar kNo ratings yet

- Nr-r09-Dynamics of Electrical MachinesDocument1 pageNr-r09-Dynamics of Electrical Machinessudhakar kNo ratings yet

- Nr-Computer OrganizationDocument1 pageNr-Computer Organizationsudhakar kNo ratings yet

- 09-Digital Control SystemsDocument2 pages09-Digital Control Systemssudhakar kNo ratings yet

- NR r09 Energy Conversion SystemsDocument1 pageNR r09 Energy Conversion Systemssudhakar kNo ratings yet

- 09-Biomedical InstrumentationDocument1 page09-Biomedical Instrumentationsudhakar kNo ratings yet

- Nr-R09-Advanced MicroprocessorsDocument1 pageNr-R09-Advanced Microprocessorssudhakar kNo ratings yet

- Nr-Digital Control SystemsDocument1 pageNr-Digital Control Systemssudhakar kNo ratings yet

- Nr-Advanced Digital Signal ProcessingDocument1 pageNr-Advanced Digital Signal Processingsudhakar kNo ratings yet

- Nr-Advanced Mechanics of SolidsDocument2 pagesNr-Advanced Mechanics of Solidssudhakar kNo ratings yet

- 09 InternetworkingDocument1 page09 Internetworkingsudhakar kNo ratings yet

- 09-Embedded SystemsDocument1 page09-Embedded Systemssudhakar kNo ratings yet

- 09-Advanced Control SystemsDocument1 page09-Advanced Control Systemssudhakar kNo ratings yet

- Tve 12 - CSS 1ST Semester Midterm Module 5 (Fernandez)Document14 pagesTve 12 - CSS 1ST Semester Midterm Module 5 (Fernandez)Aneza Jane JuanesNo ratings yet

- Lesson: 4 Quarter - Module 3Document3 pagesLesson: 4 Quarter - Module 3John Mark PrestozaNo ratings yet

- Hitachi Zaxis130w 160w 180w 210w Hydraulic Circut DiagramDocument1 pageHitachi Zaxis130w 160w 180w 210w Hydraulic Circut Diagramron100% (27)

- RedTech30 AEC Case StudyDocument3 pagesRedTech30 AEC Case StudySumitNo ratings yet

- CIS 145 Final ProjectDocument3 pagesCIS 145 Final Projectjames.jc.castro2002No ratings yet

- Process 1: PCB and Button CheckDocument4 pagesProcess 1: PCB and Button CheckadibNo ratings yet

- Rapport Final Team4 1Document36 pagesRapport Final Team4 1achwek hariziNo ratings yet

- Computer - NEB - 2079 Model Set AnsDocument14 pagesComputer - NEB - 2079 Model Set AnsArun BaralNo ratings yet

- Um HDL Mcip Rf.10 (Mesh Gateway)Document24 pagesUm HDL Mcip Rf.10 (Mesh Gateway)Stéfano OrtizNo ratings yet

- Xcode 4 Transition GuideDocument109 pagesXcode 4 Transition GuideLuis A. Castillo H.No ratings yet

- Passportautomation PDFDocument20 pagesPassportautomation PDFrahul karnNo ratings yet

- Robot/System Controller: Dynamic Next-Generation ControllerDocument2 pagesRobot/System Controller: Dynamic Next-Generation ControllerEddie Martin Díaz SánchezNo ratings yet

- 2843-1633683417627-Tutorial - 4.1 (2 Hours)Document3 pages2843-1633683417627-Tutorial - 4.1 (2 Hours)Kasuni AbeynayakeNo ratings yet

- Imre - Get Better at Software Engineering With AIDocument19 pagesImre - Get Better at Software Engineering With AIAvi SutantoNo ratings yet

- Mapping Types in HibernateDocument8 pagesMapping Types in HibernateramchandaniraviNo ratings yet

- How To Setup and Configure Elatec Tcpconv Network Hardware: Card ReaderDocument3 pagesHow To Setup and Configure Elatec Tcpconv Network Hardware: Card ReadersololoNo ratings yet

- Redhat VirtualizationDocument54 pagesRedhat VirtualizationAnkur Verma50% (2)

- MS BKRPDocument50 pagesMS BKRPEdward StarkNo ratings yet

- 5 - Collections TutorialsDocument4 pages5 - Collections TutorialsJyotishalok SaxenaNo ratings yet

- Prototype (Final)Document16 pagesPrototype (Final)Manish JangidNo ratings yet

- Computer Networks IDocument329 pagesComputer Networks IShweta100% (1)

- 0.0.0.0 Lab - Configuring Devices For Use With Cisco Configuration Professional (CCP) 2.5 - InstructorDocument12 pages0.0.0.0 Lab - Configuring Devices For Use With Cisco Configuration Professional (CCP) 2.5 - InstructorSalem TrabelsiNo ratings yet

- Ranchhod RangilaDocument13 pagesRanchhod Rangilapalakgabani3No ratings yet

- NetApp Pre - NS0-184 60q-DEMODocument25 pagesNetApp Pre - NS0-184 60q-DEMOSubhajit RoychoudhuryNo ratings yet

- Dell Inspiron 1464 1564 1764 Quanta UM3 UM6 Discrete SchematicsDocument60 pagesDell Inspiron 1464 1564 1764 Quanta UM3 UM6 Discrete SchematicsjampcarlosNo ratings yet

- Barney ErrorDocument79 pagesBarney ErrorDylanAlbertNivala2022No ratings yet

- The C++ Type System Is Your Friend 2016Document39 pagesThe C++ Type System Is Your Friend 2016jaansegusNo ratings yet

- Product Datasheet: Compact PLC Base Twido - 100..240 V AC Supply - 24 I 24 V DC - 16 ODocument12 pagesProduct Datasheet: Compact PLC Base Twido - 100..240 V AC Supply - 24 I 24 V DC - 16 OAnthony Fluker CuevaNo ratings yet

- Seismic Raises $8M Led by Polychain and A16z - HackMDDocument3 pagesSeismic Raises $8M Led by Polychain and A16z - HackMDbonobomonkeyNo ratings yet