Professional Documents

Culture Documents

VLSI Lab Evaluation Sheet

VLSI Lab Evaluation Sheet

Uploaded by

neelambikas.20.beec0 ratings0% found this document useful (0 votes)

1 views2 pagesCopyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

1 views2 pagesVLSI Lab Evaluation Sheet

VLSI Lab Evaluation Sheet

Uploaded by

neelambikas.20.beecCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

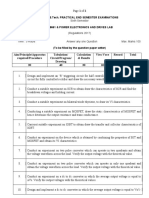

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

ACHARYA INSTITUTE OF TECHNOLOGY

SOLDEVANAHALLI, BENGALURU

LIST OF EXPERIMENTS AND EVALUATION SHEET

Sub: VLSI Lab Code: 18ECL77

Name: Sem/Sec:

Sl. CO1 CO2 CO3 CO4 Total Faculty

No Name of the Experiment (10M) Marks Sign

(10M) (10M) (10M)

(40M)

1a Capture the schematic CMOS Inverter for

different widths of inverter and compute

Propagation delay rise time and fall time

Draw the layout for inverter for Wp/Wn

1b

=40um/20um using optimum layout methods

and verify DRC and LVS extract parasitic

and compute pre layout and post layout

simulation

2a Draw the schematic of 2 input NAND gate

for different strengths X,2X and 4X and

compute Propagation delay rise time and fall

time

2b

Draw the layout for 2 input NAND for

Wp/Wn =40um/20um using optimum layout

methods and verify DRC and LVS extract

parasitic and compute pre layout and post

layout simulation

3a Draw the schematic of common source

amplifier with PMOS mirror circuit and

measure UGB and amplification Factor for

different transistor parameters

3b

Draw the layout of common source amplifier

using optimum layout methods verify DRC

and LVS extract parasitic and compute pre

layout and post layout simulation

4a Capture the Schematic of a 2 – Stage

Operational Amplifier and measure the

following: UGB, Bandwidth. Gain Margin

and Phase Margin with and without coupling

capacitance

Use the Op-Amp in the Inverting and Non-

4b Inverting configuration and verify its

functionality

Draw the layout of common source amplifier

using optimum layout methods verify DRC

and LVS extract parasitic and compute pre

layout and post layout simulation

5a Write Verilog code for 4 bit UP/Down

asynchronous reset counter and verify the

functionality using Test bench

Synthesis the design by setting area and time

5b

constraints and find the Critical Path and

Maximum Frequency of Operation

6a Write Verilog code for 4 bit adder and verify the

functionality using Test bench

Synthesis the design by setting area and time

constraints and identify Critical path, Maximum

6b delay, Total number of cells, Power requirement

and Total area required

7a Write Verilog code for UART and verify the

functionality using Test bench

Synthesis the design by setting area and time

constraints Tabulate the Area, Power and Delay

7b for the Synthesized netlist and Identify Critical

path

8a Write Verilog code for 32 bit ALU and verify

the functionality using Test bench

8b Synthesis the design by setting area and time

constraints Tabulate the Area, Power and Delay

for the Synthesized netlist and Identify Critical

path

9 Latch and Flip-Flop

Synthesize the design and compare the synthesis

report (D, SR. JK)

10 Internal Assessment

Total Marks

You might also like

- GE8261 - ElectronicsDocument3 pagesGE8261 - ElectronicsSenthil Ilangovan50% (2)

- 18csl37-Ade Lab ManualDocument41 pages18csl37-Ade Lab ManualEragon ShadeSlayerNo ratings yet

- FVofDiffOpAmp WPDocument51 pagesFVofDiffOpAmp WPmarius260No ratings yet

- VLSI Lab ManualDocument41 pagesVLSI Lab ManualDyavegowda PNo ratings yet

- Vlsi Lab Manual (18ecl77) - 2022-23Document226 pagesVlsi Lab Manual (18ecl77) - 2022-23Prajwal KoppaNo ratings yet

- EC8361 - ADCLab Manual PDFDocument105 pagesEC8361 - ADCLab Manual PDFeshwari2000100% (1)

- B.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Document3 pagesB.E. Electronics and Communication Engineering: VLSI LAB (0:0:3) 1.5Amit ShetNo ratings yet

- VLSI LabDocument4 pagesVLSI Labnithyamohan82No ratings yet

- Ec8311 Experiment QuestionsDocument2 pagesEc8311 Experiment QuestionsBalamurugan SMNo ratings yet

- VLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Document148 pagesVLSI LAB MANUAL (18ECL77) - Analog dt14-01-2022Aamish PriyamNo ratings yet

- 637862647808605476ece 18ecl77 E1s1 PPTDocument37 pages637862647808605476ece 18ecl77 E1s1 PPTSiddu UmaraniNo ratings yet

- ECE - List of ExperimentsDocument15 pagesECE - List of ExperimentsRAMESHNo ratings yet

- Rajkiya Engineering College Kannauj: Electronic Circuit Design (REC 752)Document10 pagesRajkiya Engineering College Kannauj: Electronic Circuit Design (REC 752)Manjeet SinghNo ratings yet

- Electronics Laboratory: A Lab Manual OnDocument102 pagesElectronics Laboratory: A Lab Manual OnRevathipathiNo ratings yet

- Ee8661 1Document2 pagesEe8661 1YokeshNo ratings yet

- Comm - Lab Manual-Final 31.05.23Document58 pagesComm - Lab Manual-Final 31.05.23atifarmaan72No ratings yet

- Gopi 1 EC Lab ManualDocument102 pagesGopi 1 EC Lab ManualGopinath B L NaiduNo ratings yet

- Analog Circuits Lab Manual: Atria Institute of TechnologyDocument60 pagesAnalog Circuits Lab Manual: Atria Institute of TechnologyTháHäKâduvàyîLzNo ratings yet

- Edc Lab-1 Manual-2Document91 pagesEdc Lab-1 Manual-2Ashish SharmaNo ratings yet

- Analog Circuits Lab manual18ECL48Document29 pagesAnalog Circuits Lab manual18ECL48Dintle PhofuNo ratings yet

- Aim/Apparatus Required/procedure Circuit /tabulation Calculation &result Viva-Voce Recor D Total 30 30 20 10 10 100Document2 pagesAim/Apparatus Required/procedure Circuit /tabulation Calculation &result Viva-Voce Recor D Total 30 30 20 10 10 100Jeyakumar VenugopalNo ratings yet

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document3 pagesAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalNo ratings yet

- Analog & Digital Student Lab ManualDocument150 pagesAnalog & Digital Student Lab ManualMaheshwaran Mahi100% (1)

- ECD Lab NEC 752Document17 pagesECD Lab NEC 752pcjoshi02No ratings yet

- Adsd ManualDocument69 pagesAdsd Manualsce21cs133No ratings yet

- Ade Record eDocument75 pagesAde Record eSai PrateikNo ratings yet

- Ap4111 Esd - Record (1) (1) 1Document80 pagesAp4111 Esd - Record (1) (1) 1inivetha1998No ratings yet

- Analog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and EngineeringDocument61 pagesAnalog and Digital Electronics Lab Manual (17CSL37) : Department of Computer Science and Engineeringvadla77No ratings yet

- Advance Communication Lab - 2020Document45 pagesAdvance Communication Lab - 2020AdityaNo ratings yet

- Mtech July 2018 1st Sem0001Document13 pagesMtech July 2018 1st Sem0001Isaac SabuNo ratings yet

- ECD Lab EEC 752Document17 pagesECD Lab EEC 752juhi99360% (5)

- Lecroy Sparq Cascade Microtech S-Parameter Measurements Rev1Document60 pagesLecroy Sparq Cascade Microtech S-Parameter Measurements Rev1Duncan LauNo ratings yet

- Design of Fully Differential Operational Amplifier With High Gain, Large Bandwidth and Large Dynamic RangeDocument93 pagesDesign of Fully Differential Operational Amplifier With High Gain, Large Bandwidth and Large Dynamic RangeAhmed EdrisNo ratings yet

- Ec1305 Analog and Digital Circuits LaboratoryDocument2 pagesEc1305 Analog and Digital Circuits LaboratoryMohamed Abdul RahimNo ratings yet

- List of ExpntDocument23 pagesList of ExpntddNo ratings yet

- 3rd Sem List of PracticalsDocument5 pages3rd Sem List of Practicalsanil rautelaNo ratings yet

- Aim/Apparatus Required/procedure Circuit /tabulation Calculation &result Viva-Voce Recor D Total 30 30 20 10 10 100Document2 pagesAim/Apparatus Required/procedure Circuit /tabulation Calculation &result Viva-Voce Recor D Total 30 30 20 10 10 100Jeyakumar VenugopalNo ratings yet

- Ee 6511-2016 Lab QuestionsDocument5 pagesEe 6511-2016 Lab QuestionsVenkatesan Sundaram0% (2)

- Be8261/be8261 2.2Document4 pagesBe8261/be8261 2.2Karthikeyan KrishnasamyNo ratings yet

- ECD Lab NEC 752Document17 pagesECD Lab NEC 752Ravindra Kumar0% (1)

- A Two-Tone Test Method For Continuous-Time Adaptive EqualizersDocument7 pagesA Two-Tone Test Method For Continuous-Time Adaptive EqualizersNidhi GuptaNo ratings yet

- Experiment 6 Oscilloscope Laboratory Practical Et 3O4B: Figure L. Block Diagram of TypicaloscilloscopeDocument5 pagesExperiment 6 Oscilloscope Laboratory Practical Et 3O4B: Figure L. Block Diagram of TypicaloscilloscopeMuhammad ZikryNo ratings yet

- Aim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Document2 pagesAim/Principle/Apparatus Required/procedure Tabulation/Circuit/ Program/Drawing Calculation & Results Viva-Voce Record Total 25 30 25 10 10 100Jeyakumar VenugopalNo ratings yet

- Lab Manual CNDocument83 pagesLab Manual CNrenugasri100% (2)

- Wireless CommunicationDocument3 pagesWireless CommunicationPRASANNA KUMAR BNo ratings yet

- Analog and Digital Electronics Lab Manual PDFDocument109 pagesAnalog and Digital Electronics Lab Manual PDFShaun ThomasNo ratings yet

- Jnanavikas Institute of Technology: Mr. Shubas S.RDocument74 pagesJnanavikas Institute of Technology: Mr. Shubas S.RAbhishek nNo ratings yet

- ADC Lab Manual 10EC67Document73 pagesADC Lab Manual 10EC67Shikha PrasadNo ratings yet

- Electronics Device Manual (NEC-354) : Department of Electronics & Communication EngineeringDocument58 pagesElectronics Device Manual (NEC-354) : Department of Electronics & Communication EngineeringE-Biz NetworkNo ratings yet

- Ec II Lab Manual (2013 2014)Document85 pagesEc II Lab Manual (2013 2014)surendhar1987No ratings yet

- Scan Path DesignDocument54 pagesScan Path DesignaguohaqdoNo ratings yet

- 2022-23 - A0481206 - DC LabDocument165 pages2022-23 - A0481206 - DC Labphilipju461No ratings yet

- C & S Lab Ques SetDocument6 pagesC & S Lab Ques SetbloomeceNo ratings yet

- D C Lab ManualDocument76 pagesD C Lab ManualHanzo HenshiNo ratings yet

- Controllability and ObservabilityDocument15 pagesControllability and ObservabilityaashishscribdNo ratings yet

- LP Ec6311Document5 pagesLP Ec6311Iniya IlakkiaNo ratings yet

- Wideband RF Technologies and Antennas in Microwave FrequenciesFrom EverandWideband RF Technologies and Antennas in Microwave FrequenciesNo ratings yet

- Software Radio: Sampling Rate Selection, Design and SynchronizationFrom EverandSoftware Radio: Sampling Rate Selection, Design and SynchronizationNo ratings yet

- Untitled SpreadsheetDocument3 pagesUntitled Spreadsheetneelambikas.20.beecNo ratings yet

- Assignment 1Document2 pagesAssignment 1neelambikas.20.beecNo ratings yet

- Taylo's Series MethodDocument13 pagesTaylo's Series Methodneelambikas.20.beecNo ratings yet

- Modified Euler's MethodDocument11 pagesModified Euler's Methodneelambikas.20.beecNo ratings yet

- A-Level Answer Sheet - 01 Computer ArchitectureDocument9 pagesA-Level Answer Sheet - 01 Computer ArchitectureMugerwa CharlesNo ratings yet

- Course Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignDocument2 pagesCourse Name Digital Logic Design Year/Semester II B. Tech/I Sem L T P C Regulation Year 2021-2022 3 0 0 3 Digital Logic DesignRameshchandra K ECENo ratings yet

- Micro OperationsDocument47 pagesMicro OperationsHema SivaNo ratings yet

- Chapter 1 Part1 PDFDocument49 pagesChapter 1 Part1 PDFtesfayebbNo ratings yet

- W9 ConfigDocument37 pagesW9 Configahsanliaqat426No ratings yet

- Introduction To 68HC11 MICROCONTROLLERDocument72 pagesIntroduction To 68HC11 MICROCONTROLLERNarasimha Murthy Yayavaram100% (3)

- 161 DivdrDocument1 page161 DivdrRadmila LugonjicNo ratings yet

- STM 8 S 003 F 3Document104 pagesSTM 8 S 003 F 3Vũ AnhNo ratings yet

- EE 460R - Introduction To VLSIDocument3 pagesEE 460R - Introduction To VLSItrashdnpNo ratings yet

- 15A04802 Low Power VLSI Circuits & SystemsDocument1 page15A04802 Low Power VLSI Circuits & SystemsMALLAVARAPU NARASAREDDYNo ratings yet

- EE230Project Muhammad&ChadDocument56 pagesEE230Project Muhammad&ChadTrần Tấn ĐạiNo ratings yet

- Comparch PDFDocument84 pagesComparch PDFSushil KumarNo ratings yet

- Combinational Circuits LDICDocument129 pagesCombinational Circuits LDIChemanth ramireddyNo ratings yet

- Micro MCQ Unit 4,5Document20 pagesMicro MCQ Unit 4,5Abhijit KumarNo ratings yet

- Digital Logic DesignsDocument1 pageDigital Logic DesignsKevin Haworth100% (3)

- DE Module 03Document20 pagesDE Module 03Rishabh TiwariNo ratings yet

- Circuit Design With VHDL: Tutorial Quartus 14 and The "Danjel" BoardDocument22 pagesCircuit Design With VHDL: Tutorial Quartus 14 and The "Danjel" BoardawsdNo ratings yet

- Latch Vs Flip FlopDocument2 pagesLatch Vs Flip Flop3nadhs100% (1)

- VLSIDocument139 pagesVLSIJay SonawaneNo ratings yet

- Micro - 51 Eb (User)Document298 pagesMicro - 51 Eb (User)maskply100% (1)

- Complete Vlsi NotesDocument160 pagesComplete Vlsi NotesTarun SinghalNo ratings yet

- Um0044 User Manual: Flashlink Jtag Programming Cable For PSD and UpsdDocument15 pagesUm0044 User Manual: Flashlink Jtag Programming Cable For PSD and UpsdshadowrideNo ratings yet

- A Brief History of Computer ArchitectureDocument12 pagesA Brief History of Computer ArchitectureMary Josette Baco EbajoNo ratings yet

- Micro Processor Vs MicrocontrollerDocument2 pagesMicro Processor Vs MicrocontrollerMisge ChekoleNo ratings yet

- Fetch Decode Execute Reset CycleDocument36 pagesFetch Decode Execute Reset CycleAbhishek Belnekar0% (1)

- Different Types of Integrated CircuitsDocument4 pagesDifferent Types of Integrated Circuitsashvini patilNo ratings yet

- Chapter 12Document107 pagesChapter 12Gautham AnebajaganeNo ratings yet

- Lab 02 Gate Level ModelingDocument10 pagesLab 02 Gate Level Modelingrizwan900No ratings yet

- 6800Document11 pages6800Nikola PetrovićNo ratings yet

- Fees Structures VLSI InstitutesDocument15 pagesFees Structures VLSI Institutesmustha keemNo ratings yet