Professional Documents

Culture Documents

SiC 3.3kV 44A

SiC 3.3kV 44A

Uploaded by

magnottonCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SiC 3.3kV 44A

SiC 3.3kV 44A

Uploaded by

magnottonCopyright:

Available Formats

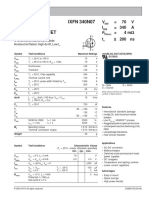

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Silicon Carbide MOSFET VDS = 3300 V

N-Channel Enhancement Mode RDS(ON)(Typ.) = 50 mΩ

ID (TC = 100°C) = 44 A

Features Package

• Softer RDS(ON) v/s Temperature Dependency D

• LoRing™ - Electromagnetically Optimized Design

G

• Smaller RG(INT) and Lower QG G

• Low Device Capacitances (COSS, CRSS) RoHS

N

• Industry-Leading UIL & Short-Circuit Robustness KS

I

S

• Robust Body Diode with Low VF and Low QRR D = Drain

• Normally Off-Stable Temperature up to 175°C

R

G = Gate

• Optimized Package with Separate Driver Source Pin TO-247-4 S = Source REACH

E

KS = Kelvin Source

E

Advantages Applications

N E

• Compatible with Commercial Gate Drivers • Traction

I L

• Low Conduction Losses at all Temperatures • Solar String Inverters

• Reduced Ringing • EV- Fast Chargers

G P

• Faster and More Efficient Switching • Pulsed Power

• Lesser Switching Spikes and Lower Losses • Switched Mode Power Supply

N M

• Better Power Density and System Efficiency • Energy Storage

• Ease of Paralleling without Thermal Runaway • Solid State Transformers

E SA

• Superior Robustness and System Reliability • Solid State Circuit Breakers

Absolute Maximum Ratings (At TC = 25°C Unless Otherwise Stated)

Parameter Symbol Conditions Values Unit Note

Drain-Source Voltage VDS(max) VGS = 0 V, ID = 100 µA 3300 V

Gate-Source Voltage (Dynamic) VGS(max) -10 / +25 V

Gate-Source Voltage (Static) VGS(op) Recommended Operation -5 / +20 V

TC = 25°C, VGS = -5 / +20 V 63

Continuous Forward Current ID TC = 100°C, VGS = -5 / +20 V 44 A Fig. 15

TC = 135°C, VGS = -5 / +20 V 32

Pulsed Drain Current ID(pulse) tP ≤ 3µs, D ≤ 1%, VGS = 20 V, Note 1 235 A Fig. 14

Power Dissipation PD Tc = 25°C 536 W Fig. 16

Non-Repetitive Avalanche Energy EAS L = 11.2 mH, IAS = 20.0 A 2250 mJ

Operating and Storage Temperature Tj , Tstg -55 to 175 °C

Thermal/Package Characteristics

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

Thermal Resistance, Junction - Case RthJC 0.21 0.28 °C/W Fig. 13

Weight WT 6.2 g

Mounting Torque TM Screws to Heatsink 1.1 Nm

Note 1: Pulse Width tP Limited by Tj(max)

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 1 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

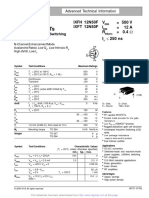

Electrical Characteristics (At TC = 25°C Unless Otherwise Stated)

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

Drain-Source Breakdown Voltage VDSS VGS = 0 V, ID = 100 µA 3300 V

Zero Gate Voltage Drain Current IDSS VDS = 3300 V, VGS = 0 V 1 µA

VDS = 0 V, VGS = 25 V 100

Gate Source Leakage Current IGSS nA

VDS = 0 V, VGS = -10 V -100

G

VDS = VGS, ID = 10.0 mA 2.5 3.50

Gate Threshold Voltage VGS(th) V Fig. 9

VDS = VGS, ID = 10.0 mA, Tj = 175°C 2.40

N

VDS = 10 V, ID = 40 A 15.3

Transconductance gfs S Fig. 4

I

VDS = 10 V, ID = 40 A, Tj = 175°C 16.4

VGS = 20 V, ID = 40 A 50 65

R

Drain-Source On-State Resistance RDS(ON) mΩ Fig. 5-8

VGS = 20 V, ID = 40 A, Tj = 175°C 105

Input Capacitance Ciss 7301

E

Output Capacitance Coss 130 pF Fig. 11

E

Reverse Transfer Capacitance Crss 12.3

E

Coss Stored Energy Eoss 84 µJ Fig. 12

VDS = 1000 V, VGS = 0 V

N

Coss Stored Charge Qoss 254 nC

L

f = 1 MHz, VAC = 25mV

I

Effective Output Capacitance (Energy

Co(er) 168

Related)

G P

pF Note 2

Effective Output Capacitance (Time

Co(tr) 254

Related)

N M

Gate-Source Charge Qgs VDS = 1000 V, VGS = -5 / +20 V 120

Gate-Drain Charge Qgd ID = 40 A 100 nC Fig. 10

E SA

Total Gate Charge Qg Per IEC607478-4 340

Internal Gate Resistance RG(int) f = 1 MHz, VAC = 25 mV 1.2 Ω

Turn-On Switching Energy

EOn 1222

(Body Diode) Tj = 25°C, VGS = -5/+20V, RG(ext) = 3 Ω, L =

µJ Fig. 22,26

Turn-Off Switching Energy 60.0 µH, ID = 50 A, VDD = 1700 V

EOff 533

(Body Diode)

Turn-On Delay Time td(on) 74

Rise Time tr VDD = 1700 V, VGS = -5/+20V 37

RG(ext) = 3 Ω, L = 60.0 µH, ID = 50 A ns Fig. 24

Turn-Off Delay Time td(off) Timing relative to VDS, Inductive load 32

Fall Time tf 18

*The chip technology was characterized up to 200 V/ns. The measured dV/dt was limited by measurement test setup and package.

Note 2: Co(er), a lumped capacitance that gives same stored energy as C OSS while V DS is rising from 0 to 1000V.

Co(tr), a lumped capacitance that gives same charging times as COSS while V DS is rising from 0 to 1000V.

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 2 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Reverse Diode Characteristics

Values

Parameter Symbol Conditions Unit Note

Min. Typ. Max.

VGS = -5 V, ISD = 20 A 4.1

Diode Forward Voltage VSD V Fig. 17-18

VGS = -5 V, ISD = 20 A, Tj = 175°C 3.5

Continuous Diode Forward Current IS VGS = -5 V, Tc = 100°C 49 A

G

Diode Pulse Current IS(pulse) VGS = -5 V, Note 1 196 A

Reverse Recovery Time trr 154 ns

VGS = -5 V, ISD = 50 A, VR = 1700 V

N

Reverse Recovery Charge Qrr 740 nC

dif/dt = 500 A/µs, Tj = 25°C

I

Peak Reverse Recovery Current Irrm 17 A

Reverse Recovery Time trr 204 ns

R

VGS = -5 V, ISD = 50 A, VR = 1700 V

Reverse Recovery Charge Qrr 2840 nC

dif/dt = 500 A/µs, Tj = 175°C

E

Peak Reverse Recovery Current Irrm 38 A

N E E

G I PL

N

E SA M

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 3 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

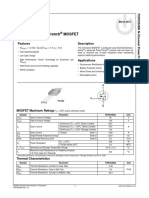

Figure 1: Output Characteristics (Tj = 25°C) Figure 2: Output Characteristics (Tj = 175°C)

N G

R I

E E

I N L E

N G M P

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

E SA

Figure 3: Output Characteristics (VGS = 20 V) Figure 4: Transfer Characteristics (VDS = 10 V)

ID = f(VDS, T);

j tP = 250 µs ID = f(VGS, T);

j tP = 100 µs

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 4 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 5: On-State Resistance v/s Temperature Figure 6: On-State Resistance v/s Drain Current

N G

R I

E E

I N L E

N G M P

RDS(ON) = f(T,j VGS); tP = 250 µs; ID = 40 A RDS(ON) = f(T,I

j D); tP = 250 µs; VGS = 20 V

E SA

Figure 7: Normalized On-State Resistance v/s Temperature Figure 8: On-State Resistance v/s Gate Voltage

RDS(ON) = f(T);

j tP = 250 µs; ID = 40 A; VGS = 20 V RDS(ON) = f(T,V

j GS); tP = 250 µs; I D = 40 A

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 5 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 9: Threshold Voltage Characteristics Figure 10: Gate Charge Characteristics

N G

R I

E E

I N L E

N G

VGS(th) = f(T);

M P

j VDS = VGS; ID = 10.0 mA ID = 40 A; VDS = 1000 V; Tc = 25°C

E SA

Figure 11: Capacitance v/s Drain-Source Voltage Figure 12: Output Capacitor Stored Energy

f = 1 MHz; VAC = 25mV Eoss = f(VDS)

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 6 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 13: Transient Thermal Impedance Figure 14: Safe Operating Area (Tc = 25°C)

N G

R I

E E

I N L E

N G M P

Zth,jc = f(tP,D); D = tP/T ID = f(VDS, tP); Tj ≤ 175°C; D = 0

E SA

Figure 15: Current De-rating Curve Figure 16: Power De-rating Curve

ID = f(TC); Tj ≤ 175°C PD = f(TC); Tj ≤ 175°C

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 7 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 17: Body Diode Characteristics (Tj = 25°C) Figure 18: Body Diode Characteristics (Tj = 175°C)

N G

R I

E E

I N L E

N G M P

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

E SA

Figure 19: Third Quadrant Characteristics (Tj = 25°C) Figure 20: Third Quadrant Characteristics (Tj = 175°C)

ID = f(VDS, VGS); tP = 250 µs ID = f(VDS, VGS); tP = 250 µs

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 8 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 21: Inductive Switching Energy v/s Drain Current Figure 22: Inductive Switching Energy v/s Drain Current

(VDD = 1500V) (VDD = 1700V)

N G

R I

E E

I N L E

N G M P

Tj = 25°C; VGS = -5/+20V; RG(ext) = 3 Ω; L = 60.0µH Tj = 25°C; VGS = -5/+20V; RG(ext) = 3 Ω; L = 60.0µH

E SA

Figure 23: Inductive Switching Energy v/s RG(ext) Figure 24: Switching Time v/s RG(ext)

(VDD = 1700V) (VDD = 1700V)

Tj = 25°C; VGS = -5/+20V; IDS = 50 A; L = 60.0µH Tj = 25°C; VGS = -5/+20V; IDS = 50 A; L = 60.0µH

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 9 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Figure 25: Inductive Switching Energy v/s Temperature Figure 26: dV/dt v/s RG(ext)

(VDD = 1700V) (VDD = 1700V)

N G

R I

E E

I N L E

N G M P

Tj = 25°C; VGS = -5/+20V; RG(ext) = 3 Ω; IDS = 50 A; L = 60.0µH Tj = 25°C; VGS = -5/+20V; IDS = 50 A; L = 60.0µH

E SA

Figure 27: High Current IV

ID = f(VDS); tP ≤ 3 µs; VGS = 20 V

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 10 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

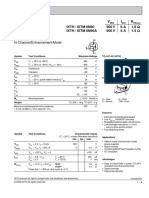

Gate Charge Circuit Gate Charge Waveform

VDS

G

VGS

Gate Voltage (VGS)

N

D.U.T RLoad

R I

E

ID VDD

IG(cont)

N E E

I L

QGS QGD

G P

Gate Charge (QG)

Switching Time Circuit

N

E SA M Switching Time Waveform

90%

Same device as the D.U.T.

LLoad

-5 V VGS 10%

VDS

10% 10%

VDS

VGS

VDD

D.U.T.

RG

90% 90%

ID td(on) td(off)

tr tf

ton toff

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 11 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Switching Energy Circuit Switching Energy Waveform

EON = ∫ ID x VDS x dt EOFF = ∫ ID x VDS x dt

Same device as the D.U.T.

LLoad

-5 V Irr

G

VDS

I N

VDS

VGS

VDD

R

D.U.T.

RG

E E ID

I N L E IDS

N G M P

E SA

Reverse Recovery Circuit Reverse Recovery Waveform

D.U.T.

LLoad IF

-5 V

trr

IF

0 Level

VGS 90%

VDD

Same device

as the D.U.T. dIrr/dt in 10%

RG Irr

to 90% range

10%

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 12 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Package Dimensions

TO-247-4 Package Outline

0.62(15.75) 0.19(4.83)

0.516(13.10)

0.635(16.13) 0.205(5.21)

0.557(14.15)

0.5(12.7)

0.216(5.49) 0.487(12.38)

G

0.236(6.0) 0.075(1.91)

0.25(6.35) 0.529(13.43)

0.085(2.16)

0.037(0.95)

0.049(1.25)

N

0.237(6.04)

I

0.248(6.30)

0.145(3.68)

0.2(5.10)

R

0.64(16.25)

0.695(17.65)

Ø 0.138(3.51)

E

0.118(3.0) Ø 0.144(3.65)

0.917(23.30)

0.929(23.60)

E

Ø 0.283(7.18) REF

E

0.093(2.35)

0.104(2.65)

I N PL 0.09(2.29)

G

0.1(2.54)

0.156(3.97)

0.172(4.37)

N

0.681(17.31)

M

0.701(17.82)

E SA

0.042(1.07)

0.052(1.33)

0.1(2.54) BSC

0.2 (5.08) BSC

0.021(0.55)

0.027(0.68)

0.042(1.07)

0.063(1.60)

0.094(2.39)

0.116(2.94)

Recommended Solder Pad Layout Package View

Case(D)

Ø 0.088(2.24)

Ø 0.067(1.7)

0.1(2.54)

G

0.1(2.54) D

0.2(5.08)

S KS

NOTE

1. CONTROLLED DIMENSION IS INCH. DIMENSION IN BRACKET IS MILLIMETER.

2. DIMENSIONS DO NOT INCLUDE END FLASH, MOLD FLASH, MATERIAL PROTRUSIONS.

3. THE SOURCE AND KELVIN-SOURCE PINS ARE NOT INTERCHANGABLE. THEIR EXCHANGE MIGHT LEAD TO MALFUNCTION.

Rev 21/May Latest Version at: www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K.pdf Page 13 of 14

G2R50MT33K TM

3300 V 50 mΩ SiC MOSFET

Compliance

RoHS Compliance

The levels of RoHS restricted materials in this product are below the maximum concentration values (also referred to as the threshold

limits) permitted for such substances, or are used in an exempted application, in accordance with EU Directive 2011/65/EC (RoHS 2), as

adopted by EU member states on January 2, 2013 and amended on March 31, 2015 by EU Directive 2015/863. RoHS Declarations for this

product can be obtained from your GeneSiC representative.

REACH Compliance

G

REACH substances of high concern (SVHCs) information is available for this product. Since the European Chemical Agency (ECHA) has

published notice of their intent to frequently revise the SVHC listing for the foreseeable future, please contact a GeneSiC representative to

N

insure you get the most up-to-date REACH SVHC Declaration. REACH banned substance information (REACH Article 67) is also available

I

upon request.

Disclaimer

E R

GeneSiC Semiconductor, Inc. reserves right to make changes to the product specifications and data in this document without notice.

E

GeneSiC disclaims all and any warranty and liability arising out of use or application of any product. No license, express or implied to any

E

intellectual property rights is granted by this document.

I N L

Unless otherwise expressly indicated, GeneSiC products are not designed, tested or authorized for use in life-saving, medical, aircraft

navigation, communication, air traffic control and weapons systems, nor in applications where their failure may result in death, personal

G P

injury and/or property damage.

N M

Related Links

E SA

• SPICE Models: https://www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K_SPICE.zip

• PLECS Models: https://www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K_PLECS.zip

• CAD Models: https://www.genesicsemi.com/sic-mosfet/G2R50MT33K/G2R50MT33K_3D.zip

• Gate Driver Reference: https://www.genesicsemi.com/technical-support

• Evaluation Boards: https://www.genesicsemi.com/technical-support

• Reliability: https://www.genesicsemi.com/reliability

• Compliance: https://www.genesicsemi.com/compliance

• Quality Manual: https://www.genesicsemi.com/quality

Revision History

• Rev 21/May: Updated switching time and switching energy data

• Supersedes: Rev 21/Jan

www.genesicsemi.com/sic-mosfet/

Rev 21/May Published by GeneSiC Semiconductor, Inc.

Copyright© 2021 GeneSiC Semiconductor Inc. 43670 Trade Center Place Suite 155, Dulles, VA 20166; USA

All Rights Reserved. Page 14 of 14

Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

GeneSiC Semiconductor:

G2R50MT33K

You might also like

- Phy OR-GATE ProjectDocument9 pagesPhy OR-GATE ProjectAwesom Ask50% (2)

- Mosfet Power Transistor 64a 1200VDS G3R20MT12N-2449153Document15 pagesMosfet Power Transistor 64a 1200VDS G3R20MT12N-2449153Ramón MartinezNo ratings yet

- G3R20MT17KDocument14 pagesG3R20MT17KPalmNo ratings yet

- Littelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371Document7 pagesLittelfuse Discrete MOSFETs N-Channel HiPerFETs IX-1856371basheer almetwakelNo ratings yet

- Hiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)Document3 pagesHiperfet Power Mosfets Isoplus247 Ixfr 70N15: (Electrically Isolated Backside)William moreNo ratings yet

- HCS65R320SDocument7 pagesHCS65R320SnareshNo ratings yet

- Silicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement ModeDocument10 pagesSilicon Carbide Power MOSFET C3M MOSFET Technology: N-Channel Enhancement Modealllim88No ratings yet

- N-Channel 650V (D-S) Power MOSFET: Features Product SummaryDocument10 pagesN-Channel 650V (D-S) Power MOSFET: Features Product SummaryDenis KilianNo ratings yet

- GP50B60PD1 InternationalRectifierDocument11 pagesGP50B60PD1 InternationalRectifierStelvio QuizolaNo ratings yet

- IRGP50B60PD1PBFDocument11 pagesIRGP50B60PD1PBFenriquevazquez27No ratings yet

- Datasheet 3Document8 pagesDatasheet 3RAMESH JUNJUNo ratings yet

- Infineon IRFP4229 DataSheet v01 - 01 ENDocument9 pagesInfineon IRFP4229 DataSheet v01 - 01 ENRoni Div MasterphpNo ratings yet

- Mosfet 4242Document8 pagesMosfet 4242cruz yorisNo ratings yet

- IRFB4227PBF Infineon Datasheet 9782845Document3 pagesIRFB4227PBF Infineon Datasheet 9782845IvanNo ratings yet

- Infineon IRGP50B60PD1 DataSheet v01 - 00 ENDocument10 pagesInfineon IRGP50B60PD1 DataSheet v01 - 00 ENalllim88No ratings yet

- Normally - OFF Silicon Carbide Super Junction Transistor: V 650 V I 4 A R 415 MDocument5 pagesNormally - OFF Silicon Carbide Super Junction Transistor: V 650 V I 4 A R 415 McrackintheshatNo ratings yet

- 65N06 Series: N-Channel Power MOSFET (63A, 55volts) DescriptionDocument8 pages65N06 Series: N-Channel Power MOSFET (63A, 55volts) DescriptionRamon Cuba LopezNo ratings yet

- Hy1707p HooyiDocument10 pagesHy1707p Hooyimarcos crNo ratings yet

- SM 8009 NSFDocument10 pagesSM 8009 NSFnaifn0955No ratings yet

- Irfp4227pbf PDFDocument8 pagesIrfp4227pbf PDFTyron DsouzaNo ratings yet

- DTN10N90SJ/DTP10N90SJ/DTP10N90FSJ: Features Product SummaryDocument10 pagesDTN10N90SJ/DTP10N90SJ/DTP10N90FSJ: Features Product SummaryHumberto AguilarNo ratings yet

- Hiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FDocument2 pagesHiperrf Power Mosfets: Ixfh 12N50F Ixft 12N50FdtramirNo ratings yet

- APM2558NU: Pin Description FeaturesDocument10 pagesAPM2558NU: Pin Description FeaturesLuciano LucasNo ratings yet

- Irgp50b60pdpdf 231209 190134Document11 pagesIrgp50b60pdpdf 231209 190134Denilson BonifacioNo ratings yet

- Irgp 35 B 60 PDDocument11 pagesIrgp 35 B 60 PDflywheel2006No ratings yet

- Pin Description Features: N-Channel Enhancement Mode MosfetDocument10 pagesPin Description Features: N-Channel Enhancement Mode MosfetBrahim SalahNo ratings yet

- Ixfh 12N100FDocument2 pagesIxfh 12N100FAnonymous lQyR2IWNo ratings yet

- Irf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: FeaturesDocument12 pagesIrf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: FeaturesVasja OlijarnykNo ratings yet

- S2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETDocument8 pagesS2PF380N65R: N-Channel 650V Enhancement Mode Power MOSFETMaikel Borges IglesiasNo ratings yet

- FDP025N06Document9 pagesFDP025N06bravo.bravoNo ratings yet

- Irgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument11 pagesIrgp4063Dpbf: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodesebaNo ratings yet

- Irlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetDocument13 pagesIrlz44Z Irlz44Zs Irlz44Zl: Automotive MosfetrickiaqpNo ratings yet

- HX50N06 Heatsink Planar N-Channel Power MOSFETDocument6 pagesHX50N06 Heatsink Planar N-Channel Power MOSFETDaniel OrtizNo ratings yet

- cs7n65f A9tdyDocument10 pagescs7n65f A9tdyRogeriomgoNo ratings yet

- APM1105NU SinopowerDocument11 pagesAPM1105NU SinopowerYoelNo ratings yet

- IRF3205ZDocument13 pagesIRF3205Zdaniel_yonutz07No ratings yet

- DatasheetDocument10 pagesDatasheetAbush GezuNo ratings yet

- SM 7506 NFPDocument11 pagesSM 7506 NFPgustavo toroNo ratings yet

- Ap4na1r4cmt ADocument6 pagesAp4na1r4cmt AMar GaoNo ratings yet

- Irf 840aDocument9 pagesIrf 840aPareNo ratings yet

- Irlr3705Zpbf Irlu3705Zpbf: FeaturesDocument11 pagesIrlr3705Zpbf Irlu3705Zpbf: FeaturesGanNo ratings yet

- Infineon IRL3705N DS v01 - 02 ENDocument9 pagesInfineon IRL3705N DS v01 - 02 ENFrancisco Mendoza BalderasNo ratings yet

- Irgp 4066 DPBFDocument11 pagesIrgp 4066 DPBFbahmanNo ratings yet

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionkalanghoNo ratings yet

- IRG7PSH73K10PBFDocument9 pagesIRG7PSH73K10PBFRaduNo ratings yet

- Ap4n2r1mt V1Document6 pagesAp4n2r1mt V1Mar GaoNo ratings yet

- APM2518NU AnpecElectronicsCoroprationDocument10 pagesAPM2518NU AnpecElectronicsCoroprationpapainoelmorreuNo ratings yet

- Irf3805Pbf Irf3805Spbf Irf3805Lpbf: FeaturesDocument14 pagesIrf3805Pbf Irf3805Spbf Irf3805Lpbf: Featurescarmel asentistaNo ratings yet

- UF3C065040K3S Data SheetDocument11 pagesUF3C065040K3S Data Sheetsultaniwahid240No ratings yet

- Hiperfet Power Mosfets Q-Class Ixfn 27N80Q V 800 V I 27 A 320 MDocument2 pagesHiperfet Power Mosfets Q-Class Ixfn 27N80Q V 800 V I 27 A 320 MJosephSyNo ratings yet

- Irf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: Automotive MosfetDocument13 pagesIrf3205Zpbf Irf3205Zspbf Irf3205Zlpbf: Automotive MosfetAurelian IordacheNo ratings yet

- Apm6006nfpc TugDocument11 pagesApm6006nfpc Tugx6ricardo6xNo ratings yet

- Irgp50B60Pdpbf: Warp2 Series Igbt With Ultrafast Soft Recovery DiodeDocument11 pagesIrgp50B60Pdpbf: Warp2 Series Igbt With Ultrafast Soft Recovery Diodepablo carrizoNo ratings yet

- 75V, 80A Heatsink Planar N-Channel Power Mosfets: PB Free Plating ProductDocument5 pages75V, 80A Heatsink Planar N-Channel Power Mosfets: PB Free Plating ProductARESJAVIERNo ratings yet

- Infineon IRFS4229 DataSheet v01 - 01 ENDocument10 pagesInfineon IRFS4229 DataSheet v01 - 01 ENRAMESH JUNJUNo ratings yet

- PDF04N65LDocument5 pagesPDF04N65LOtaku SlayerNo ratings yet

- Standard Power MOSFET: N-Channel Enhancement ModeDocument5 pagesStandard Power MOSFET: N-Channel Enhancement ModetvsamsungjpNo ratings yet

- IRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeDocument12 pagesIRGIB10B60KD1: Insulated Gate Bipolar Transistor With Ultrafast Soft Recovery DiodeSmain BendeddoucheNo ratings yet

- AP65SL190AI AdvancedPowerElectronicsDocument6 pagesAP65SL190AI AdvancedPowerElectronicsAkhmad Isnaeni RamdaniNo ratings yet

- Photo DiodeDocument40 pagesPhoto DiodeMadhu46d0% (1)

- Advanced Power Electronics Corp.: DescriptionDocument5 pagesAdvanced Power Electronics Corp.: DescriptionVladimir DoyminNo ratings yet

- QTY Reference My Reference Value Type Information CTM Qty Model# Digikey P/N Each CTM Note Manufacture RDocument1 pageQTY Reference My Reference Value Type Information CTM Qty Model# Digikey P/N Each CTM Note Manufacture RFreddy CamposNo ratings yet

- Module 3, Lecture 3 FOCDocument9 pagesModule 3, Lecture 3 FOCSanmukh KaurNo ratings yet

- Rif 1404Document7 pagesRif 1404Nelson Naval CabingasNo ratings yet

- K3596 01L FujiElectricDocument4 pagesK3596 01L FujiElectricLAN JR HOUSENo ratings yet

- WWW - Iranswitching.Ir: Ac/Dc Switch Mode Power Supply Design GuideDocument1 pageWWW - Iranswitching.Ir: Ac/Dc Switch Mode Power Supply Design GuidedraNo ratings yet

- PSpice ExperimentDocument7 pagesPSpice ExperimentMustapha BeziouiNo ratings yet

- K3918 - Mosfet Datasheet PDFDocument8 pagesK3918 - Mosfet Datasheet PDFGleison PrateadoNo ratings yet

- LS TTL CharacteristicDocument6 pagesLS TTL CharacteristicArturo72No ratings yet

- What Is A Diac-TriacDocument26 pagesWhat Is A Diac-TriacChristian Dave Tamparong100% (1)

- Chapter 2-Field-Effect Transistor (FET)Document37 pagesChapter 2-Field-Effect Transistor (FET)LucasNo ratings yet

- Selected Design Topics: Logic and Computer Design FundamentalsDocument15 pagesSelected Design Topics: Logic and Computer Design FundamentalsYawar Abbas KhanNo ratings yet

- QuestionsDocument2 pagesQuestionsNishant PanchalNo ratings yet

- Exploded View & Part ListDocument10 pagesExploded View & Part ListliberthNo ratings yet

- Power TransistorDocument37 pagesPower Transistorsaikarthick023No ratings yet

- Static Random-Access MemoryDocument6 pagesStatic Random-Access MemoryFRANCESCO222No ratings yet

- Book Reviews: Hot Carrier Design Considerations For MOS Devices and CircuitsDocument1 pageBook Reviews: Hot Carrier Design Considerations For MOS Devices and Circuits9949409548No ratings yet

- Amit EDKCON2022Document6 pagesAmit EDKCON2022Sonam RewariNo ratings yet

- Buk555 100aDocument8 pagesBuk555 100aDiego AliasNo ratings yet

- ST 2 N 3904Document6 pagesST 2 N 3904buzzrdNo ratings yet

- Tabe Lade Transistor EsDocument61 pagesTabe Lade Transistor EsFabrizio LutianeNo ratings yet

- Nanomaterials: Lecture 2: LithographyDocument15 pagesNanomaterials: Lecture 2: Lithographyvdaditya1000No ratings yet

- Technology Roadmap For 22nm and BeyondDocument4 pagesTechnology Roadmap For 22nm and BeyondpranavkumarbNo ratings yet

- Chapter 6: - MOSFET OperationDocument11 pagesChapter 6: - MOSFET OperationAtul YadavNo ratings yet

- 5 Unit - 5 Field Effect Transistors: Review QuestionsDocument16 pages5 Unit - 5 Field Effect Transistors: Review Questionsashley correa100% (1)

- Compression of Electronic DevicesDocument7 pagesCompression of Electronic DevicesSuvam SahuNo ratings yet

- BJT FabricationDocument26 pagesBJT Fabricationabhinavbhatnagar0% (1)

- IC Technology 3D 3D 3DDocument208 pagesIC Technology 3D 3D 3D姜義修No ratings yet