Professional Documents

Culture Documents

u19ecv16 Fvlsi Cad Syllabus

u19ecv16 Fvlsi Cad Syllabus

Uploaded by

Ramesh Mallai0 ratings0% found this document useful (0 votes)

2 views2 pagesu19ecv16 Fvlsi Cad Syllabus

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentu19ecv16 Fvlsi Cad Syllabus

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

2 views2 pagesu19ecv16 Fvlsi Cad Syllabus

u19ecv16 Fvlsi Cad Syllabus

Uploaded by

Ramesh Mallaiu19ecv16 Fvlsi Cad Syllabus

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 2

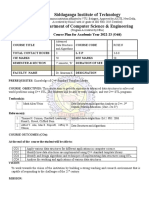

VIVEKANANDHA COLLEGE OF ENGINEERING FOR WOMEN

(Autonomous Institution, Affiliated to Anna University ,Chennai)

Elayampalayam, Tiruchengode – 637 205

Programme B.E. Programme Code 103 Regulation 2019

ELECTRONICS AND COMMUNICATION Semester

Department

ENGINEERING

Periods Per Week Credit Maximum Marks

Course Code Course Name

L T P C CA ESE Total

U19ECV16 Foundations of VLSI 3 0 0 3 40 60 100

CAD

The main objective of the course is

To provide an introduction to the fundamentals of Computer-Aided Design tools

for the modeling, design, analysis, test, and verification of digital Very Large Scale

Integration (VLSI) systems.

Course

To understand the advanced techniques for solving computer-aided design

Objective

problems for a wide range of design styles.

To Analysis different types of floor planning, placement and routing algorithms.

To learn the two level logic synthesis and binary decision diagrams.

To learn different Scheduling Algorithms

At the end of the course, the student should be able to Knowledge Level

CO1:Establish comprehensive understanding of the various

phases of CAD for digital electronic systems, from digital logic K3

simulation to physical design, including test and verification

Course CO2: Analyze the physical design process of VLSI design flow K4

Outcome CO3:Demonstrate knowledge of computational and optimization

K5

algorithms and tools applicable to solving CAD related problems.

CO4: Establish capability for CAD tool development and K3

enhancement.

CO5: Explore the hardware modeling and high level

K2

transformation

Pre-requisites

CO / PO Mapping CO/PSO

(3/2/1 indicates strength of correlation) 3-Strong, 2 – Medium, 1– Weak Mapping

Cos Programme Outcomes (Pos) PSOs

PO 1 PO 2 PO 3 PO 4 PO 5 PO 6 PO 7 PO 8 PO 9 PO PO PO PSO PSO PSO

10 11 12 1 2 3

CO 1 3 3 2 3 2

CO 2 3 3 2 3 2 2 2

CO 3 3 3 2 3 2 2 3 2

CO 4 3 3 2 2 2 3 2

CO 5 3 2 2 2 2 3

Course Assessment Methods

Direct

1. Continuous Assessment Test I, II & III

2. Assignment and Seminar

3. End-Semester examinations

Indirect

1. Course – end survey

Content of the syllabus

Unit – I VLSI DESIGN METHODOLOGIES Periods 9

168

Signature of BOS Chairman ECE

Introduction to VLSI Design methodologies – Review of Data structures and algorithms –Review of VLSI

Design automation tools – Algorithmic Graph Theory and Computational Complexity – Tractable and

Intractable problems – general purpose methods for combinatorial optimization.

Unit – II DESIGN RULES Periods 9

Layout Compaction – Design rules – problem formulation – algorithms for constraint graph compaction –

placement and partitioning – Circuit representation – Placement algorithms – partitioning.

Unit – III FLOOR PLANNING Periods 9

Floor planning concepts – shape functions and Floor plan sizing – Types of local Routing problems – Area

routing – channel routing – global routing – algorithms for global routing.

Unit – IV SIMULATION Periods 9

Simulation – Gate-level Modeling and simulation – Switch-level Modeling and simulation- Combinational

Logic Synthesis – Binary Decision Diagrams – Two Level Logic Synthesis.

Unit – V MODELLING AND SYNTHESIS Periods 9

High level Synthesis – Hardware models – Internal representation – Allocation –assignment and scheduling –

Simple scheduling algorithm – Assignment problem – High level transformations.

Total Periods 45

TEXT BOOK

1. S.H. Gerez, ―Algorithms for VLSI Design Automation‖, John Wiley & Sons,2019

References

1. N.A. Sherwani, ―Algorithms for VLSI Physical Design Automation‖, Kluwer Academic

Publishers, 2002.

E-Resources

E1 https://nptel.ac.in/courses/108102042/CO-ORDINATED BY : IIT DELHI

E2 https://nptel.ac.in/courses/106102062/ CO-ORDINATED BY : IIT DELHI

https://drive.google.com/file/d/0BzoKWH8M1BoTVnBham5ENGZCUE0/view?usp=sharing&res

E3

ourcekey=0-fap9ekmWbZ0tZKnlXamzUg

169

Signature of BOS Chairman ECE

You might also like

- Creating A Company Culture For Security Design DocumentDocument5 pagesCreating A Company Culture For Security Design DocumentKazu Kato100% (1)

- Artificial Intelligence With Python (Machine Learning Foundations, Methodologies, and Applications) (Teik Toe Teoh, Zheng Rong)Document334 pagesArtificial Intelligence With Python (Machine Learning Foundations, Methodologies, and Applications) (Teik Toe Teoh, Zheng Rong)Benyaiich Said80% (5)

- Introduction To Computing Systems:: From Bits and Gates To C and BeyondDocument15 pagesIntroduction To Computing Systems:: From Bits and Gates To C and BeyondNirmal GuptaNo ratings yet

- Parallel ComputingDocument2 pagesParallel ComputingRamesh MallaiNo ratings yet

- Cad CamDocument3 pagesCad CamKannan SreenivasanNo ratings yet

- Me Vlsi Sem IiDocument12 pagesMe Vlsi Sem IiRockymoorthiNo ratings yet

- Syllabus BCADocument243 pagesSyllabus BCAAkshay mukundNo ratings yet

- Unit1 COADocument135 pagesUnit1 COAlostNo ratings yet

- Batch - 2 - Os Lab Front Page - Take PrintDocument9 pagesBatch - 2 - Os Lab Front Page - Take PrintMohamed ShowqathNo ratings yet

- DBMS LabDocument58 pagesDBMS Labmahedi.hassanNo ratings yet

- CST202 - Ktu QbankDocument12 pagesCST202 - Ktu QbankYaseen 777No ratings yet

- VLSI LabDocument103 pagesVLSI Labutso boseNo ratings yet

- Data visualization syllabus for final yearsDocument2 pagesData visualization syllabus for final yearsSenthil KumarNo ratings yet

- Department of Computer Science & Engineering: Course FileDocument11 pagesDepartment of Computer Science & Engineering: Course FilePathivadaSantoshNaiduNo ratings yet

- Machine LearningDocument2 pagesMachine LearningRamesh MallaiNo ratings yet

- Mtech-Syllabus-Data Science - Sem2Document18 pagesMtech-Syllabus-Data Science - Sem2reshmaitagiNo ratings yet

- CSEN3001 SyllabusDocument2 pagesCSEN3001 SyllabusAjitesh SinghNo ratings yet

- Database Management SystemDocument4 pagesDatabase Management SystemVaishak ShettyNo ratings yet

- CAPDCSEM011T_ Software Engineering Methodology (1)Document2 pagesCAPDCSEM011T_ Software Engineering Methodology (1)ayush8109120869No ratings yet

- MCA - II SEMESTER Syllabus and Bridge CourseDocument33 pagesMCA - II SEMESTER Syllabus and Bridge Coursevishalsinghsoft62No ratings yet

- Updated - DSDV - BEC302 - LAB MANUAL123Document54 pagesUpdated - DSDV - BEC302 - LAB MANUAL123Harish G CNo ratings yet

- C# and .NET Programming SysDocument12 pagesC# and .NET Programming SysrjoshittaNo ratings yet

- Comprehensive Examination SyllabusDocument3 pagesComprehensive Examination SyllabusDr. I Priya Stella MaryNo ratings yet

- ADS Lecture Plan 2022 23 ODDDocument6 pagesADS Lecture Plan 2022 23 ODD1SI20CS116 - Sunil Kumar B ANo ratings yet

- Computer OrganisationDocument12 pagesComputer OrganisationSachuNo ratings yet

- COMPUTER-NETWORKS-CourseFile 28 11 2022Document10 pagesCOMPUTER-NETWORKS-CourseFile 28 11 2022pvssivaprasadcseNo ratings yet

- B.tech Cse VTR Uge2021 de SyllabusDocument4 pagesB.tech Cse VTR Uge2021 de SyllabusBOLLIGARLA MOHAN SAI AKASH,CSE2021 Vel Tech, ChennaiNo ratings yet

- QP ArchDocument1 pageQP ArchsubhamNo ratings yet

- BCA NEP Core SyllabusDocument54 pagesBCA NEP Core SyllabusJanesh AtreyNo ratings yet

- Unit 1Document241 pagesUnit 1jatinsingh150815No ratings yet

- 3/2/1: High/Medium/LowDocument8 pages3/2/1: High/Medium/Lowaman singhNo ratings yet

- Ec8552-Cao Unit 5Document72 pagesEc8552-Cao Unit 5Anonymous c75J3yX33No ratings yet

- HPC Revised SyllabusDocument4 pagesHPC Revised SyllabusPratiksha BhapkarNo ratings yet

- I A 1 QP Software Engineering - 22CSE141 3rd Sem Exam On 10 Oct 2023Document2 pagesI A 1 QP Software Engineering - 22CSE141 3rd Sem Exam On 10 Oct 2023MK JAYANTHI KANNANNo ratings yet

- COA Lab ManualDocument41 pagesCOA Lab ManualRakoon Dog100% (3)

- D17A - BDA - (Autonomous Header) Index - 23-24Document4 pagesD17A - BDA - (Autonomous Header) Index - 23-24GautiiiNo ratings yet

- Vlsi Lab Maual 20-21 FinalizedDocument89 pagesVlsi Lab Maual 20-21 FinalizedBharath Raj SNo ratings yet

- SOFTWARE ENGINEERING QB - NewDocument6 pagesSOFTWARE ENGINEERING QB - NewKarthik RamNo ratings yet

- MCA Syllabus - 1st Sem PDFDocument32 pagesMCA Syllabus - 1st Sem PDFshatabdi mukherjeeNo ratings yet

- Computer Science and Engineering S7 & S8Document11 pagesComputer Science and Engineering S7 & S8wastebasketNo ratings yet

- CompilerDesign - UNIT 3 CDDocument67 pagesCompilerDesign - UNIT 3 CDADUSUMALLI LAKSHMI PRIYANo ratings yet

- 21ec503 Vlsi Design Unit 1Document110 pages21ec503 Vlsi Design Unit 1santhoshiniNo ratings yet

- Amar2021 - Course Handout SOFTWARE ENGINEERINGDocument7 pagesAmar2021 - Course Handout SOFTWARE ENGINEERINGamaraimlNo ratings yet

- Course File Content - Cloud ComputingDocument29 pagesCourse File Content - Cloud Computingurvashi chaudharyNo ratings yet

- Unit1 COADocument135 pagesUnit1 COASam SamNo ratings yet

- RDBMS SyllDocument5 pagesRDBMS SyllJennifer AngelNo ratings yet

- Compiler Design SyllabusDocument3 pagesCompiler Design SyllabusPrince AatifNo ratings yet

- CSE - TY - Final - Syllabus 30 - 8 - 23Document62 pagesCSE - TY - Final - Syllabus 30 - 8 - 23Rudhhi ShahNo ratings yet

- 21CSL35-OOPS LAB - Lab Manual 21CSL35-OOPS LAB - Lab ManualDocument88 pages21CSL35-OOPS LAB - Lab Manual 21CSL35-OOPS LAB - Lab ManualKavi ShettyNo ratings yet

- Unit2 - COA Shikha SinghDocument106 pagesUnit2 - COA Shikha SinghSam SamNo ratings yet

- CD Course DeliveryDocument10 pagesCD Course DeliverySuganthiNo ratings yet

- PYTHON PROGRAMMING-CourseFile 05 09 2022Document11 pagesPYTHON PROGRAMMING-CourseFile 05 09 2022pvssivaprasadcseNo ratings yet

- Unit 3 - Cloud Computing - Digital Course MaterialDocument88 pagesUnit 3 - Cloud Computing - Digital Course MaterialDhiviya BharathiNo ratings yet

- Information Technology s7 & s8Document317 pagesInformation Technology s7 & s8AKHIL HAKKIMNo ratings yet

- Structural DynamicsDocument2 pagesStructural Dynamicsmythilispd_355305156No ratings yet

- CourseOutcomes FLAT (2021-22)Document2 pagesCourseOutcomes FLAT (2021-22)nandanNo ratings yet

- B.Tech Third Year Syllabus - EMBEDDED SYSTEMSDocument6 pagesB.Tech Third Year Syllabus - EMBEDDED SYSTEMSMAHESWARY SREENATH ECNo ratings yet

- SOFTCOMPUTINGDocument2 pagesSOFTCOMPUTINGRamesh MallaiNo ratings yet

- Open Electives Cse SyllabusDocument27 pagesOpen Electives Cse Syllabusyamini seshakalaNo ratings yet

- LDCA Unit5Document124 pagesLDCA Unit5jatinsingh150815No ratings yet

- Ooad Cat2Document1 pageOoad Cat2KALPANA CNo ratings yet

- IT Curriculum - SEM4Document13 pagesIT Curriculum - SEM4vidihac283No ratings yet

- Signature of Bos Chairman 67Document2 pagesSignature of Bos Chairman 67Ramesh MallaiNo ratings yet

- U19EC416 DSP Lab SyllabusDocument2 pagesU19EC416 DSP Lab SyllabusRamesh MallaiNo ratings yet

- Parallel ComputingDocument2 pagesParallel ComputingRamesh MallaiNo ratings yet

- Fingerprint Identification Method For SecureDocument5 pagesFingerprint Identification Method For SecureRamesh MallaiNo ratings yet

- Colour Face Recognition A Novel Recognition MethodDocument5 pagesColour Face Recognition A Novel Recognition MethodRamesh MallaiNo ratings yet

- An Efficient Detection of Glaucoma andDocument6 pagesAn Efficient Detection of Glaucoma andRamesh MallaiNo ratings yet

- Continuous Time Signals Part II Fourier TransformDocument14 pagesContinuous Time Signals Part II Fourier TransformRamesh MallaiNo ratings yet

- 1000 Digital Signal Processing MCQsDocument405 pages1000 Digital Signal Processing MCQskibrom atsbha42% (12)

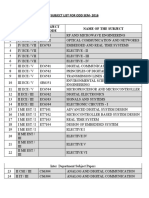

- Subject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectDocument3 pagesSubject List For Odd Sem-2016 Class/ SEM Subject Code Name of The SubjectRamesh MallaiNo ratings yet

- Odd Sem Subject ListDocument2 pagesOdd Sem Subject ListRamesh MallaiNo ratings yet

- Gate Question - ECEDocument8 pagesGate Question - ECERamesh MallaiNo ratings yet

- Vivekanandha: Institute of Engineering and Technology For WomenDocument1 pageVivekanandha: Institute of Engineering and Technology For WomenRamesh MallaiNo ratings yet

- Ge6757 TQM SyllabusDocument2 pagesGe6757 TQM SyllabusRamesh MallaiNo ratings yet

- VVC SyllabusDocument1 pageVVC SyllabusRamesh MallaiNo ratings yet

- 1) Two Vectors A, B Are Orthogonal IfDocument9 pages1) Two Vectors A, B Are Orthogonal IfRamesh MallaiNo ratings yet

- DSP Question BankDocument44 pagesDSP Question BankRamesh Mallai0% (1)

- ZeptoBit Isolated USB-UART Adapter - DatasheetDocument8 pagesZeptoBit Isolated USB-UART Adapter - DatasheetGonzaloNo ratings yet

- Hotel Management SystemDocument11 pagesHotel Management SystemFARYAL FATIMANo ratings yet

- Abstraction, Refinement and Proof For Probabilistic Systems - 2005 - Annabelle McIver - Carroll MorganDocument395 pagesAbstraction, Refinement and Proof For Probabilistic Systems - 2005 - Annabelle McIver - Carroll MorganJESUS ELVIS CASTAÑEDA CASTILLONo ratings yet

- SPSS Data Entry Network ServerDocument2 pagesSPSS Data Entry Network ServerKato StratocasterNo ratings yet

- Thirteenth Air Navigation Conference: Working PaperDocument4 pagesThirteenth Air Navigation Conference: Working PaperWILLIANNo ratings yet

- Free Download Management System Project R Free Download Management System Project RDocument10 pagesFree Download Management System Project R Free Download Management System Project RFLEXCODEC TECHNo ratings yet

- ARMAX Model Definitions: General-Linear Polynomial Model Autoregressive With Exogenous TermsDocument3 pagesARMAX Model Definitions: General-Linear Polynomial Model Autoregressive With Exogenous TermsAaruniNo ratings yet

- Noise Level Estimation Using SVDDocument7 pagesNoise Level Estimation Using SVDVineeth KumarNo ratings yet

- List of Computer Units: Description Inventory Item NoDocument5 pagesList of Computer Units: Description Inventory Item NoYNNA DERAYNo ratings yet

- Overview: Chengdu Ebyte Electronic Technology Co, LTD E32-433T30D User ManualDocument2 pagesOverview: Chengdu Ebyte Electronic Technology Co, LTD E32-433T30D User ManualSergey SevruginNo ratings yet

- Vol. No. 3,: N DFT ATDocument10 pagesVol. No. 3,: N DFT ATAllama HasanNo ratings yet

- CNC 8037 Ordering HandbookDocument6 pagesCNC 8037 Ordering Handbookgabrielsilva2042No ratings yet

- Wavion DataSheet WFOutdoorDocument4 pagesWavion DataSheet WFOutdoorKenneth DennisonNo ratings yet

- Feature Extraction Identifying Condition Indicators With Matlab PDFDocument23 pagesFeature Extraction Identifying Condition Indicators With Matlab PDFKaran DoshiNo ratings yet

- Datasheet of iDS 7216HQHI M1 - FA - V4.71.140 - 20230621Document6 pagesDatasheet of iDS 7216HQHI M1 - FA - V4.71.140 - 20230621QuickTech MDQNo ratings yet

- The Specifications of TFP290N08Document1 pageThe Specifications of TFP290N08SuryaKelanaNo ratings yet

- Sre .SRSDocument16 pagesSre .SRSniamh alyNo ratings yet

- q3 Computer 10Document8 pagesq3 Computer 10Jocidelle LubricoNo ratings yet

- Age and Gender Detection Using Python: Mohd Rafey, GurubasavaDocument5 pagesAge and Gender Detection Using Python: Mohd Rafey, GurubasavaVijay LakshmiNo ratings yet

- Maths (Lectures 1 & 2 The Foundations Logic and Proofs)Document51 pagesMaths (Lectures 1 & 2 The Foundations Logic and Proofs)Bhuvanesh Kakarla AP21110010593No ratings yet

- Lecture 2Document69 pagesLecture 2zomukozaNo ratings yet

- Java 8 Virtual Training - 01st - 03rd February 2023Document10 pagesJava 8 Virtual Training - 01st - 03rd February 2023K JAGADISHNo ratings yet

- SSRDocument0 pagesSSRRadsreadsNo ratings yet

- 1st Year Computer Science Chapter WiseDocument12 pages1st Year Computer Science Chapter WiseasifalimsmNo ratings yet

- Empower 2 21 CFR 11 Compliance WorksheetDocument14 pagesEmpower 2 21 CFR 11 Compliance Worksheetjeet100% (1)

- Network Security ModelDocument5 pagesNetwork Security ModelMr VamsiNo ratings yet

- Fire Detection Major Project ReportDocument33 pagesFire Detection Major Project Reportvanishri moger100% (1)