Professional Documents

Culture Documents

5. 제조공법-3

5. 제조공법-3

Uploaded by

vaviye9091Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

5. 제조공법-3

5. 제조공법-3

Uploaded by

vaviye9091Copyright:

Available Formats

Post Exposure Bake

• Deep UV Exposure Bake

– Temperature Uniformity

– PEB Delay

• Conventional I-Line PEB

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Amine Contamination of DUV Resist

leading to “T-top” Formation

Region of Neutralized

unexposed photoresist

photoresist Resist T-topping

}

H+ PAG H+

PAG

H+ PAG H+

PAG Development

H+

PAG H+

PAG

H+ H+

PAG

H+ PAG H+

Acid-catalyzed

reaction of

exposed resist

(post PEB)

Semiconductor Manufacturing Technology Figure 15.1 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Reduction of Standing Wave Effect due to PEB

Standing Unexposed Exposed

waves photoresist photoresist

PAC PAC PAC PAC PAC

PAC PAC PAC

PAC

PAC PAC

PAC PAC

PAC PAC PAC

PAC PAC

PAC PAC PAC

PAC PAC

PAC

PAC PAC

PAC PAC PAC PAC PAC

PAC PAC PAC

PAC

PAC PAC PAC

PAC PAC

(a) Exposure to UV light (b) Striations in resist

PAC PAC

PAC

PAC

PAC

PAC PAC

PAC

PAC

PAC PAC

PAC PAC

PAC PAC

PAC PAC

(c) PEB causes PAC diffusion (d) Result of PEB

Semiconductor Manufacturing Technology Figure 15.2 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Develop

• Negative Resist

• Positive Resist

• Development Methods

• Resist Development Parameters

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

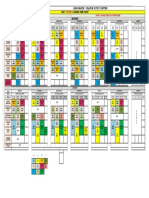

Photoresist Development Problems

Resist Substrate

X X Ö X

Under Incomplete Correct Severe

develop develop develop overdevelop

Semiconductor Manufacturing Technology Figure 15.3 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Negative Resist Crosslinking

UV

Exposed resist

Crosslinks

Unexposed resist

Semiconductor Manufacturing Technology Figure 15.4 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Development of Positive Resist

Resist exposed to light

dissolves in the Unexposed

develop chemical. positive resist

Crosslinked

resist

Semiconductor Manufacturing Technology Figure 15.5 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Development Methods

• Continuous Spray Development

• Puddle Development

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

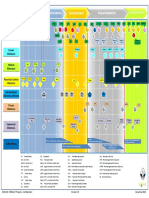

Resist Development with Continuous Spray

Spray

Vapor Resist Develop- Edge-bead

Load Station Prime Coat Rinse Removal Transfer Station

Wafer Transfer System

Vacuum chuck

To vacuum

pump Spindle

connected to

spin motor

Soft Cool Cool Hard

Bake Plate Plate Bake

(a) Wafer track system (b) Developer spray dispenser

Semiconductor Manufacturing Technology Figure 15.6 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Puddle Resist Development

Puddle

formation Developer

dispenser

(a) Puddle dispense (b) Spin-off excess developer

(c) DI H2O rinse (d) Spin dry

Semiconductor Manufacturing Technology Figure 15.7 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Resist Development Parameters

• Developer Temperature

• Developer Time

• Developer Volume

• Normality

• Rinse

• Exhaust Flow

• Wafer Chuck

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Hard Bake

• Characteristics of Hard Bake:

– Post-Development Exposure

– Evaporates Residual Solvent in Photoresist

– Hardens the Resist

– Improves Resist-to-Wafer Adhesion

– Prepares Resist for Subsequent Processing

– Higher Temperature than Soft Bake, but not

to Point Where Resist Softens and Flows

• Resist Hardening with Deep UV

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Softened Resist Flow at High Temperature

Photoresist

Semiconductor Manufacturing Technology Figure 15.8 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Develop Inspect

• Post-Develop Inspection to Find Defects

• Find Defects before Etching or Implanting

• Prevents Scrap

• Characterizes the Photo Process by

Providing Feedback Regarding Quality of

the Lithography Process

• Develop Inspect Rework Flow

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Automated Inspection Tool for Develop Inspect

Photograph courtesy of Advanced Micro Devices, Leica Auto Inspection station

Semiconductor Manufacturing Technology Photo 15.1 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

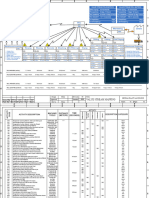

Develop Inspect Rework Flow

UV light

Resist Mask

HMDS

1. Vapor prime 2. Spin coat 3. Soft bake 4. Align and expose 5. Post-exposure bake

O2

Rejected wafers

Plasma

Strip and clean 8. Develop inspect 7. Hard bake 6. Develop

Rework

Ion implant Passed wafers Etch

Semiconductor Manufacturing Technology Figure 15.9 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Advanced Lithography

• Next Generation Lithography

– Extreme UV (EUV)

– SCALPEL

– Ion Projection Lithography (IPL)

– X-Ray

• Advanced Resist Processing

– Development Trends of Photoresist and

Lithography

– DESIRE Process

Semiconductor Manufacturing Technology © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Photolithography Improvements

1. Reduction in wavelength of the UV light source.

2. Increase in numerical aperture.

3. Chemically amplified DUV resists

4. Resolution enhancement techniques (e.g., phase-shift

masks and optical proximity correction).

5. Wafer planarization (chemical mechanical

planarization, or CMP) to reduce surface topography.

6. Advances in photolithography equipment (e.g., stepper

and step-and-scan).

Semiconductor Manufacturing Technology Table 15.2 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Concept for Extreme Ultraviolet Lithography

Step-and-scan 4×

High power reflection reticle Multilayer

laser coated mirrors

EUV

¼ image

of reticle

Plasma

Target Step-and-scan

material wafer stage

Vacuum chamber

Redrawn from International SEMATECH's Next Generation Lithography Workshop Brochure

Semiconductor Manufacturing Technology Figure 15.10 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Concept of SCALPEL

Electron beam

Step-and-scan

reticle stage

Electrostatic

lens system

(4:1 reduction)

Step-and-scan

wafer stage

Vacuum chamber

Redrawn from International SEMATECH's Next Generation Lithography Workshop Brochure

Semiconductor Manufacturing Technology Figure 15.11 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Ion Projection Lithography

Ion source

Ion beam

Mask

Electrostatic

lens system

(4:1 reduction)

Reference

plate

Step-and-scan

wafer stage

Vacuum chamber

Redrawn from International SEMATECH's Next Generation Lithography Workshop Brochure

Semiconductor Manufacturing Technology Figure 15.12 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

X-ray Spectrum

Hard X-rays Soft X-rays UV Spectrum

EUV DUV MUV

0.1 nm 1 nm 10 nm 100 nm

Synchrotron Excimer laser Hg

source lamp

Semiconductor Manufacturing Technology Figure 15.13 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Concept of X-ray Photomask

Gold plated chrome

Silicon wafer pattern X-ray absorbers

Glass frame Window etched into

lower membrane

Membrane

Scanning X-rays are directed toward a

production wafer through a photomask

similar to this one.

Redrawn from C. Y. Chang and S. M. Sze, ULSI Technology, edited by

C. Y. Chang and S. M. Sze (New York: McGraw-Hill 1996) p.314

Semiconductor Manufacturing Technology Figure 15.14 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

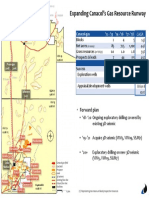

Development Trends of Photoresist and Lithography

Negative photoresist 1970s 10 mm Contact Printer

1.2 mm Scanning Aligner

Positive photoresist

(DNQ-Novolak) 1980s

1 mm G-line Stepper

0.40 mm I-line Stepper

PSM, OAI

Chemical amplification 1990s 0.35 mm

DUV Stepper

0.18 mm DUV Step and Scan

EUV Step and Scan

Advanced photoresist 2000s 0. 13 mm

top surface imaging SCALPEL

2010 0. 1 mm IPL, X-ray

Semiconductor Manufacturing Technology Figure 15.15 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

Top Surface Imaging

UV

Exposed resist Exposed Crosslinked

Unexposed

resist

(a) Normal exposure process (b) Post exposure bake

O2 plasma

develop

HMDS Silylated

exposed resist

Si Si

(c) Vapor phase silyation (d) Final developed pattern

Semiconductor Manufacturing Technology Figure 15.16 © 2001 by Prentice Hall

by Michael Quirk and Julian Serda

You might also like

- Standard Barangay Health Station (BHS)Document11 pagesStandard Barangay Health Station (BHS)rolandtrojas100% (6)

- Plaquette V3P-2 enDocument2 pagesPlaquette V3P-2 enAdrian Iacob83% (6)

- Chapter 1Document14 pagesChapter 1Manish JaiswalNo ratings yet

- 19 Oct 24 OctDocument1 page19 Oct 24 OctIshhdNo ratings yet

- Jadwal Libur Lebaran 2023Document2 pagesJadwal Libur Lebaran 2023Setiawan HatmajiNo ratings yet

- Dicrepancy ReportDocument2 pagesDicrepancy Reportirishimurali2No ratings yet

- YCCP TT-19-09-2022 - To 25-09-2022Document1 pageYCCP TT-19-09-2022 - To 25-09-2022Kk donNo ratings yet

- Stecring Colom (r)Document12 pagesStecring Colom (r)HikmahNo ratings yet

- Accounting Technician Cpac Naf 18 014Document2 pagesAccounting Technician Cpac Naf 18 014Stefania PopaNo ratings yet

- Patients Requiring Oac ACS CCS: PCI Cabg MTA PCI Cabg MTADocument1 pagePatients Requiring Oac ACS CCS: PCI Cabg MTA PCI Cabg MTAnanuka dvalishviliNo ratings yet

- Coaching OverviewDocument92 pagesCoaching OverviewRamaKrishna ANo ratings yet

- Mapping of Shipment 2Document15 pagesMapping of Shipment 2jef1234321No ratings yet

- Kves29m61 PDFDocument142 pagesKves29m61 PDFAditya AdityaNo ratings yet

- As Built-Pool Fitting ConfigurationDocument1 pageAs Built-Pool Fitting ConfigurationJomari Chris BeronNo ratings yet

- TT Advanced 16-23 MayDocument1 pageTT Advanced 16-23 MayspartanicprathamNo ratings yet

- DataDocument4 pagesDataArif AbrahimNo ratings yet

- Vidyavardhini'S College of Engineering & Technology Instrumentation Engineering Time Table For The Year 2022-2023 (Odd)Document1 pageVidyavardhini'S College of Engineering & Technology Instrumentation Engineering Time Table For The Year 2022-2023 (Odd)dikshant SolankiNo ratings yet

- Map Natural Gas ProspectiveDocument1 pageMap Natural Gas ProspectiveDelfinOviedoNo ratings yet

- TT Xii 02-09 JanDocument2 pagesTT Xii 02-09 JangodayushshrivastavaNo ratings yet

- Daily Agri Report 27 Nov 2018 by Epic ResearchDocument6 pagesDaily Agri Report 27 Nov 2018 by Epic Researchepicresearch392No ratings yet

- T650 - Engineering Science N4 Memo April 2020Document12 pagesT650 - Engineering Science N4 Memo April 2020lilspectrex24No ratings yet

- Bus Bar Testing FormatDocument27 pagesBus Bar Testing FormatAkshaya kumar mohantyNo ratings yet

- Seat PlanDocument6 pagesSeat PlanElpidio R QuirinoNo ratings yet

- Value Stream Mapping TemplateDocument1 pageValue Stream Mapping TemplateramosaquinogyNo ratings yet

- Estatus Pruebas Hermeticidad de Ventanas 2022-03-16Document5 pagesEstatus Pruebas Hermeticidad de Ventanas 2022-03-16Paula VidalNo ratings yet

- Jadual Audit Internal 1 TahunDocument2 pagesJadual Audit Internal 1 TahunFerdy MorezaNo ratings yet

- 02 Nov 07 NovDocument1 page02 Nov 07 NovIshhdNo ratings yet

- TV B Gone KitDocument61 pagesTV B Gone KitChris KladisNo ratings yet

- 2017 WFP - CentersDocument93 pages2017 WFP - CentersFrank DagohoyNo ratings yet

- Energy Performence in Textile ProcessDocument73 pagesEnergy Performence in Textile ProcessarjmandqayyumNo ratings yet

- MCBMC Cascades: Consumables & Chemicals Inventory 24-May-22Document1 pageMCBMC Cascades: Consumables & Chemicals Inventory 24-May-22Engineering DepartmentNo ratings yet

- Remineralizing Agents: Remineralizatio N Action Buffering ActionDocument1 pageRemineralizing Agents: Remineralizatio N Action Buffering ActionSanthoshi ReddyNo ratings yet

- Srujana PosterDocument1 pageSrujana PosterSanthoshi ReddyNo ratings yet

- Estatus Pruebas Hermeticidad de Ventanas 2022-03-11Document5 pagesEstatus Pruebas Hermeticidad de Ventanas 2022-03-11Paula VidalNo ratings yet

- Diagrama Centros de ManiobraDocument1 pageDiagrama Centros de Maniobrasofia hernandezNo ratings yet

- Photo Bay: Previous Process Surface Preparation PR Coating Soft Bake Alignmen T & Exposure Development PEB CleanDocument53 pagesPhoto Bay: Previous Process Surface Preparation PR Coating Soft Bake Alignmen T & Exposure Development PEB CleanMuhammad Muzammil SaleemNo ratings yet

- For Sopa Layout - 4Document1 pageFor Sopa Layout - 4ejemjunrexNo ratings yet

- Building Works at Hougang Town Daily Site Record: Activities Location Description of Works RemarksDocument1 pageBuilding Works at Hougang Town Daily Site Record: Activities Location Description of Works RemarksALFREDO JR. ARIOS CLARONo ratings yet

- Training and Certification Matrix For Projects ContractorsDocument1 pageTraining and Certification Matrix For Projects ContractorsshafieNo ratings yet

- QA/QC Requirements On FabricationDocument10 pagesQA/QC Requirements On Fabricationhash117No ratings yet

- Visio-20200814 Cross Function Flow Chart Production AlignerDocument1 pageVisio-20200814 Cross Function Flow Chart Production AlignerAkbar YudhaNo ratings yet

- PH 2 Cage Poroposal Location - Elevation ViewDocument1 pagePH 2 Cage Poroposal Location - Elevation ViewhafizulcaffleNo ratings yet

- ValueStreamMapping KASA KENDALDocument3 pagesValueStreamMapping KASA KENDALpecorepp.maesindoNo ratings yet

- Service Robot Introduction To A RestaurantDocument6 pagesService Robot Introduction To A RestaurantAmr FahmyNo ratings yet

- 04 24 2012 Mappatura Telecomando Ts6010hd Ts6513hd 9771Document8 pages04 24 2012 Mappatura Telecomando Ts6010hd Ts6513hd 9771maatNo ratings yet

- Estatus Pruebas Hermeticidad de Ventanas 2022-02-15Document5 pagesEstatus Pruebas Hermeticidad de Ventanas 2022-02-15Paula VidalNo ratings yet

- Malla CurricularDocument1 pageMalla CurricularDouglas ValenciaNo ratings yet

- Estatus Pruebas Hermeticidad de Ventanas 2022-03-15Document5 pagesEstatus Pruebas Hermeticidad de Ventanas 2022-03-15Paula VidalNo ratings yet

- Timeline 100423Document3 pagesTimeline 100423Ariandy UtamaNo ratings yet

- Iit - Ian'S Pace (Weekly Time Table) - Crash Course - 2016-17Document1 pageIit - Ian'S Pace (Weekly Time Table) - Crash Course - 2016-17Sarvesh DubeyNo ratings yet

- Right/Left Side Elevation: A B C D E F G H I J K LDocument1 pageRight/Left Side Elevation: A B C D E F G H I J K LAllan Añavisa Ostique Jr.No ratings yet

- Lookaheadnumber1 210123 134455Document1 pageLookaheadnumber1 210123 134455Jesus Reyes VeraNo ratings yet

- Summary of Approved Budget For The Contract: Department of Public Works and HighwaysDocument31 pagesSummary of Approved Budget For The Contract: Department of Public Works and HighwaysBunny HopperNo ratings yet

- LTA-43 Pre-Comm MDR (Internal Register)Document5 pagesLTA-43 Pre-Comm MDR (Internal Register)Dheeraj Chowdary DhanekulaNo ratings yet

- 貿論作業Document5 pages貿論作業ttjtjhvdh5No ratings yet

- Volte-To-Volte Call Setup v1.2cDocument1 pageVolte-To-Volte Call Setup v1.2cmcmiljareNo ratings yet

- Metaverso Program CAPEX & SUPEXDocument8 pagesMetaverso Program CAPEX & SUPEXRamon Alexander De La Cruz MartinezNo ratings yet

- Av48p775 Av56p775 Av56p785Document61 pagesAv48p775 Av56p775 Av56p785cs2swNo ratings yet

- AAXA Technologies - Pico Projector Specialists - Advanced Nano-LCoS SystemsDocument2 pagesAAXA Technologies - Pico Projector Specialists - Advanced Nano-LCoS SystemsTAREK536281No ratings yet

- Powerpoint in Back TitrationDocument29 pagesPowerpoint in Back Titrationmvmbapple100% (1)

- Facts About The MoonDocument2 pagesFacts About The Moonpatcris moncadaNo ratings yet

- Calculation-Option-1Document1 pageCalculation-Option-1JOSEPH ESCOBARNo ratings yet

- X Chemistry Notes Chapter 2 (Pages 6-10)Document5 pagesX Chemistry Notes Chapter 2 (Pages 6-10)Lekshmy BNo ratings yet

- TgaDocument27 pagesTgaprinceamitNo ratings yet

- Assignment 1 - Chapter 3 AnswerDocument9 pagesAssignment 1 - Chapter 3 AnswerHarryzam MartelNo ratings yet

- WaterDocument26 pagesWaterRahulNo ratings yet

- PHS 3601 ST Johns University Homework PDocument10 pagesPHS 3601 ST Johns University Homework PHayatfedlumohammedNo ratings yet

- Haloalkanes and HaloarenesDocument14 pagesHaloalkanes and Haloarenesshreyansh tanwarNo ratings yet

- Port Land Cement: Manufacture of Portland CementDocument24 pagesPort Land Cement: Manufacture of Portland Cementtesfalem kiros100% (1)

- Radioisotope Heater Units: National Aeronautics and Space AdministrationDocument2 pagesRadioisotope Heater Units: National Aeronautics and Space AdministrationRulemaker Studios OfficialNo ratings yet

- Co-Ordination Compound Ex-4 Solution For Vedantu TatvaDocument9 pagesCo-Ordination Compound Ex-4 Solution For Vedantu TatvaAbhinav ThapliyalNo ratings yet

- Work Plan - HW.130052.2019-12-27.Sub-Slab Depressurization System DesignDocument211 pagesWork Plan - HW.130052.2019-12-27.Sub-Slab Depressurization System Designwhite heart green mindNo ratings yet

- HIT-RE 500 V3: Safety Information For 2-Component-ProductsDocument23 pagesHIT-RE 500 V3: Safety Information For 2-Component-ProductsardhikiraNo ratings yet

- Reg. No.: Name:: Q.No. Sub. Sec. Question Description MarksDocument2 pagesReg. No.: Name:: Q.No. Sub. Sec. Question Description MarksLaxmitej ManchikantiNo ratings yet

- Formula Mass and The Mole ConceptDocument14 pagesFormula Mass and The Mole ConceptJonalyn VitalicioNo ratings yet

- Understanding Earthquake Disasters - Amita SinvhalDocument285 pagesUnderstanding Earthquake Disasters - Amita SinvhalShaikAzhar100% (1)

- Polybutadiene RubberDocument6 pagesPolybutadiene RubberAdolfo Condor Cumbrera100% (1)

- Lab Report Evt577 Wastewater TechnologyDocument17 pagesLab Report Evt577 Wastewater TechnologySITI NURAZIEMAH AZMYNo ratings yet

- M20Document54 pagesM20Mijail Pérez Miranda100% (1)

- Groundwater Contamination in MyanmarDocument17 pagesGroundwater Contamination in MyanmarHnin Wai Mar Aung100% (1)

- DT T 0004+D Datasheet TrinaTracker Vanguard 1P EN 20230508Document2 pagesDT T 0004+D Datasheet TrinaTracker Vanguard 1P EN 20230508Basma EmamNo ratings yet

- 18.J.K.mitchell&K.soga - Fundamentals of Soil BehaviourDocument505 pages18.J.K.mitchell&K.soga - Fundamentals of Soil BehaviourJose Eduardo Murillo Fernandez88% (17)

- Indian BOE Coaching Services: Gujarat BOE-2016 Paper-2 (Boiler Engg-2) SolutionDocument7 pagesIndian BOE Coaching Services: Gujarat BOE-2016 Paper-2 (Boiler Engg-2) SolutionAlok DoshiNo ratings yet

- Cholin BaseDocument5 pagesCholin Basex_aav3No ratings yet

- Physics Investigatory Project 1Document16 pagesPhysics Investigatory Project 1Tushar VermaNo ratings yet

- Introduction To EE 307Document7 pagesIntroduction To EE 307zubairawNo ratings yet

- Instu Density TestDocument6 pagesInstu Density TestDilanka S GunasinghaNo ratings yet

- SK Crude Dewaxing ProcessDocument23 pagesSK Crude Dewaxing ProcessBabji MunagalaNo ratings yet