Professional Documents

Culture Documents

std18nf03l

std18nf03l

Uploaded by

mhd.mousaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

std18nf03l

std18nf03l

Uploaded by

mhd.mousaCopyright:

Available Formats

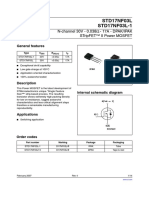

STD18NF03L

Datasheet

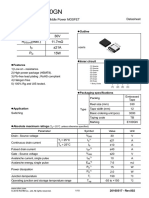

Automotive-grade N-channel 30 V, 38 mΩ typ., 17 A STripFET II Power MOSFET

in a DPAK package

Features

TAB Order code VDS RDS(on) max. ID

STD18NF03L 30 V < 50 mΩ 17 A

2 3

1

DPAK • AEC-Q101 qualified

• Exceptional dv/dt capability

D(2, TAB) • 100% avalanche tested

• Low gate charge

Applications

G(1)

• Switching applications

S(3)

Description

AM01475v1_noZen

This Power MOSFET has been developed using STMicroelectronics' unique

STripFET process, which is specifically designed to minimize input capacitance and

gate charge. This renders the device suitable for use as primary switch in advanced

high-efficiency isolated DC-DC converters for telecom and computer applications,

and applications with low gate charge driving requirements.

Product status link

STD18NF03L

Product summary

Order code STD18NF03L

Marking 18NF03L

Package DPAK

Packing Tape and reel

DS5403 - Rev 2 - April 2020 www.st.com

For further information contact your local STMicroelectronics sales office.

STD18NF03L

Electrical ratings

1 Electrical ratings

Table 1. Absolute maximum ratings

Symbol Parameter Value Unit

VDS Drain-source voltage (VGS = 0 V) 30 V

VGS Gate-source voltage ±16 V

Drain current (continuous) at TC = 25 °C 17 A

ID

Drain current (continuous) at TC = 100 °C 12 A

IDM(1) Drain current (pulsed) 68 A

PTOT Total power dissipation at TC = 25 °C 30 W

Derating Factor 0.2 W/°C

dv/dt(2). Peak diode recovery avalanche energy 7 V/ns

EAS (3)

Single pulse avalanche energy 200 mJ

Tstg Storage temperature range

-55 to 175 °C

TJ Operating junction temperature range

1. Pulse width limited by safe operating area.

2. ISD ≤ 17 A, di/dt ≤ 300 A/μs, VDD = V(BR)DSS, TJ ≤ TJ max.

3. Starting TJ = 25 °C, ID = 8.5 A, VDD = 15 V.

Table 2. Thermal data

Symbol Parameter Value Unit

Rthj-case Thermal resistance junction-case max 5.0 °C/W

Rthj-amb Thermal resistance junction-to ambient max 100 °C/W

TJ Maximum lead temperature for soldering purpose 275 °C

DS5403 - Rev 2 page 2/15

STD18NF03L

Electrical characteristics

2 Electrical characteristics

TC = 25 °C unless otherwise specified

Table 3. On-/off-states

Symbol Parameter Test conditions Min. Typ. Max. Unit

V(BR)DSS Drain-source breakdown voltage VGS = 0 V, ID = 250 μA 30 V

VGS = 0 V, VDS = max rating 1 µA

IDSS Zero gate voltage drain current

VGS = 0 V, VDS = max rating, TC = 125 °C 10 µA

IGSS Gate-body leakage current VDS = 0 V, VGS = ±16 V ±100 nA

VGS(th) Gate threshold voltage VDS = VGS, ID = 250 µA 1.0 1.5 2.2 V

VGS = 10 V, ID = 8.5 A 38 50

RDS(on) Static drain-source on-resistance mΩ

VGS = 5 V, ID = 8.5 A 45 60

Table 4. Dynamic

Symbol Parameter Test conditions Min. Typ. Max. Unit

gfs(1) Forward transconductance VDS > ID(on) x RDS(on) max., ID = 8.5A - 12 S

Ciss Input capacitance - 320 pF

Coss Output capacitance VDS = 25 V, f = 1 MHz, VGS = 0 V - 155 pF

Crss Reverse transfer capacitance - 28 pF

Qg Total gate charge VDD = 24 V, ID = 17 A - 4.8 6.5 nC

Qgs Gate-source charge RG = 4.7 Ω, VGS = 5 V - 2.25 nC

(see Figure 14. Test circuit for gate

Qgd Gate-drain charge - 1.7 nC

charge behavior)

1. Pulsed: Pulse duration = 300 μs, duty cycle 1.5%.

Table 5. Switching times

Symbol Parameter Test conditions Min. Typ. Max. Unit

td(on) Turn-on delay time VDD = 15 V, ID = 8.5 A, - 11 ns

tr Rise time RG = 4.7 Ω, VGS = 5 V - 100 ns

td(off) Turn-off delay time (see Figure 13. Test circuit for resistive - 25 ns

load switching times and

tf Fall time Figure 18. Switching time waveform) - 22 ns

DS5403 - Rev 2 page 3/15

STD18NF03L

Electrical characteristics

Table 6. Source-drain diode

Symbol Parameter Test conditions Min. Typ. Max. Unit

ISD Source-drain current - 22 A

ISDM(1) Source-drain current (pulsed) - 88 A

VSD(2) Forward on voltage ISD = 17 A, VGS = 0 V - 1.5 V

trr Reverse recovery time ISD = 17 A, di/dt = 100 A/µs, - 28 ns

Qrr Reverse recovery charge VDD = 15 V, TJ = 150 °C - 18 nC

(see Figure 15. Test circuit for inductive

IRRM Reverse recovery current - 1.3 A

load switching and diode recovery times)

1. Pulse width limited by safe operating area.

2. Pulsed: pulse duration = 300 µs, duty cycle 1.5%.

DS5403 - Rev 2 page 4/15

STD18NF03L

Electrical characteristics (curves)

2.1 Electrical characteristics (curves)

Figure 1. Safe operating area Figure 2. Thermal impedance

Figure 3. Output characteristics Figure 4. Transfer characteristics

Figure 5. Transconductance Figure 6. Static drain-source on resistance

DS5403 - Rev 2 page 5/15

STD18NF03L

Electrical characteristics (curves)

Figure 7. Gate charge vs. gate-source voltage Figure 8. Capacitance variations

Qg (nC)

Figure 9. Normalized gate threshold voltage vs

Figure 10. Normalized on resistance vs temperature

temperature

Figure 11. Source-drain diode forward characteristics Figure 12. Normalized breakdown voltage vs temperature

DS5403 - Rev 2 page 6/15

STD18NF03L

Test circuits

3 Test circuits

Figure 13. Test circuit for resistive load switching times Figure 14. Test circuit for gate charge behavior

VDD

12 V 47 kΩ

1 kΩ

100 nF

RL

2200 3.3

+ μF μF VDD

VD IG= CONST

VGS 100 Ω D.U.T.

VGS

RG D.U.T. pulse width +

2.7 kΩ

2200 VG

pulse width μF

47 kΩ

1 kΩ

AM01468v1 AM01469v1

Figure 15. Test circuit for inductive load switching and

Figure 16. Unclamped inductive load test circuit

diode recovery times

A A A L

D VD

fast 100 µH

G D.U.T. diode 2200 3.3

S B 3.3 1000 + µF µF VDD

B B

25 Ω D

µF + µF VDD ID

G D.U.T.

+ RG S

Vi D.U.T.

_

pulse width

AM01471v1

AM01470v1

Figure 18. Switching time waveform

Figure 17. Unclamped inductive waveform

ton toff

V(BR)DSS

td(on) tr td(off) tf

VD

90% 90%

IDM

10% VDS 10%

ID 0

VDD VDD VGS 90%

0 10%

AM01472v1

AM01473v1

DS5403 - Rev 2 page 7/15

STD18NF03L

Package information

4 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages,

depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product

status are available at: www.st.com. ECOPACK is an ST trademark.

4.1 DPAK (TO-252) type A package information

Figure 19. DPAK (TO-252) type A package outline

0068772_A_27

DS5403 - Rev 2 page 8/15

STD18NF03L

DPAK (TO-252) type A package information

Table 7. DPAK (TO-252) type A mechanical data

mm

Dim.

Min. Typ. Max.

A 2.20 2.40

A1 0.90 1.10

A2 0.03 0.23

b 0.64 0.90

b4 5.20 5.40

c 0.45 0.60

c2 0.48 0.60

D 6.00 6.20

D1 4.95 5.10 5.25

E 6.40 6.60

E1 4.60 4.70 4.80

e 2.159 2.286 2.413

e1 4.445 4.572 4.699

H 9.35 10.10

L 1.00 1.50

(L1) 2.60 2.80 3.00

L2 0.65 0.80 0.95

L4 0.60 1.00

R 0.20

V2 0° 8°

DS5403 - Rev 2 page 9/15

STD18NF03L

DPAK (TO-252) type A package information

Figure 20. DPAK (TO-252) type A recommended footprint (dimensions are in mm)

FP_0068772_27

DS5403 - Rev 2 page 10/15

STD18NF03L

DPAK (TO-252) packing information

4.2 DPAK (TO-252) packing information

Figure 21. DPAK (TO-252) tape outline

10 pitches cumulative

tolerance on tape +/- 0.2 mm

Top cover P0 D P2

T tape

E

F

K0 W

B1 B0

For machine ref. only A0 P1 D1

including draft and

radii concentric around B0

User direction of feed

Bending radius

User direction of feed

AM08852v1

DS5403 - Rev 2 page 11/15

STD18NF03L

DPAK (TO-252) packing information

Figure 22. DPAK (TO-252) reel outline

40mm min.

access hole

at slot location

B

D C

N

A

Tape slot G measured

in core for at hub

Full radius tape start

2.5mm min.width

AM06038v1

Table 8. DPAK (TO-252) tape and reel mechanical data

Tape Reel

mm mm

Dim. Dim.

Min. Max. Min. Max.

A0 6.8 7 A 330

B0 10.4 10.6 B 1.5

B1 12.1 C 12.8 13.2

D 1.5 1.6 D 20.2

D1 1.5 G 16.4 18.4

E 1.65 1.85 N 50

F 7.4 7.6 T 22.4

K0 2.55 2.75

P0 3.9 4.1 Base qty. 2500

P1 7.9 8.1 Bulk qty. 2500

P2 1.9 2.1

R 40

T 0.25 0.35

W 15.7 16.3

DS5403 - Rev 2 page 12/15

STD18NF03L

Revision history

Table 9. Document revision history

Date Version Changes

27-Jul-2007 1 First release.

Updated Title, Internal schematic, Features and Device summary in cover page.

29-Apr-2020 2

Minor text changes.

DS5403 - Rev 2 page 13/15

STD18NF03L

Contents

Contents

1 Electrical ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2 Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2.1 Electrical characteristics (curves) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

3 Test circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

4 Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

4.1 DPAK (TO-252) type A package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4.2 DPAK (TO-252) packing information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

DS5403 - Rev 2 page 14/15

STD18NF03L

IMPORTANT NOTICE – PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

Purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service

names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics – All rights reserved

DS5403 - Rev 2 page 15/15

You might also like

- STD 17 NF 25Document15 pagesSTD 17 NF 25Sinon Amv'sNo ratings yet

- N-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp PackageDocument12 pagesN-Channel 600 V, 0.255 Ω Typ., 13 A Mdmesh M2 Power Mosfet In A To-220Fp PackageErasmo Franco SNo ratings yet

- Stn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 PackageDocument12 pagesStn3Nf06L: N-Channel 60 V, 0.07 Ω Typ., 4 A Stripfet™ Ii Power Mosfet In A Sot-223 Packageramesh sahukhalNo ratings yet

- 20N60M2EP Mark STP20N60M2-EP 600V 13A FETDocument14 pages20N60M2EP Mark STP20N60M2-EP 600V 13A FETRuslanNo ratings yet

- Stmicroelectronics - SGST S A0007382382 1 1681241Document18 pagesStmicroelectronics - SGST S A0007382382 1 1681241MatNo ratings yet

- STF 3 NK 80 ZDocument12 pagesSTF 3 NK 80 ZGheorghe DavidNo ratings yet

- STF 13 NM 60 NDocument12 pagesSTF 13 NM 60 Nrafaelmattos2015No ratings yet

- stl66dn3llh5Document15 pagesstl66dn3llh5mhd.mousaNo ratings yet

- STF 13 NM 60 NDDocument12 pagesSTF 13 NM 60 NDlejojoel321No ratings yet

- Stp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageDocument12 pagesStp130N6F7: N-Channel 60 V, 4.2 Mω Typ., 80 A Stripfet™ F7 Power Mosfet In A To-220 PackageOsmir MonteiroNo ratings yet

- stq1nk80zr ApDocument16 pagesstq1nk80zr ApPaun LiviuNo ratings yet

- STD17NF03L STD17NF03L-1: N-Channel 30V - 0.038 - 17A - Dpak/Ipak Stripfet™ Ii Power MosfetDocument14 pagesSTD17NF03L STD17NF03L-1: N-Channel 30V - 0.038 - 17A - Dpak/Ipak Stripfet™ Ii Power MosfetSudais AkbarNo ratings yet

- N-Channel 650 V, 95 Mω Typ., 24 A Mdmesh™ M5 Power Mosfet In D²Pak PackageDocument17 pagesN-Channel 650 V, 95 Mω Typ., 24 A Mdmesh™ M5 Power Mosfet In D²Pak PackageErkanNo ratings yet

- N-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackageDocument12 pagesN-Channel 650 V, 0.60 Ω Typ., 7 A Mdmesh M2 Power Mosfet In A To-220Fp PackagejefjronNo ratings yet

- N-Channel 525 V, 1.25 Ω Typ., 4.4 A, Ultrafastmesh™ Power Mosfet In A Dpak PackageDocument17 pagesN-Channel 525 V, 1.25 Ω Typ., 4.4 A, Ultrafastmesh™ Power Mosfet In A Dpak PackageSmarttech ParobeNo ratings yet

- Stl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageDocument16 pagesStl36Dn6F7: Dual N-Channel 60 V, 23 Mω Typ., 33 A Stripfet™ F7 Power Mosfet In A Powerflat™ 5X6 Double Island PackageKunal sawantNo ratings yet

- Data SheetDocument7 pagesData SheetAstronSatNo ratings yet

- Std6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageDocument18 pagesStd6N52K3: N-Channel 525 V, 1 Ω Typ., 6.5 A Mdmesh™ K3 Power Mosfet In Dpak PackageErkanNo ratings yet

- D50N03LDocument16 pagesD50N03LO'PrimeNo ratings yet

- 8N65 PDFDocument8 pages8N65 PDFJose Luis CanterosNo ratings yet

- STP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETDocument12 pagesSTP62NS04Z: N-Channel Clamped 12.5 M, 62 A, TO-220 Fully Protected MESH OVERLAY™ Power MOSFETmartinNo ratings yet

- 30n06L InterfaceDocument8 pages30n06L Interfacepre freedaNo ratings yet

- 60N3L STMicroelectronics Elenota - PLDocument15 pages60N3L STMicroelectronics Elenota - PLNana CianchettaNo ratings yet

- STB 8 NM 60 DDocument13 pagesSTB 8 NM 60 DErkanNo ratings yet

- 3N80Document6 pages3N80hectorsevillaNo ratings yet

- STL40DN3LLH5Document15 pagesSTL40DN3LLH5angel uriel silvaNo ratings yet

- Stp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetDocument12 pagesStp40Nf10L: N-Channel 100V - 0.028 - 40A To-220 Low Gate Charge Stripfet™ Power MosfetKhairi SaidNo ratings yet

- Stn1Nk60Zl: N-Channel 600 V, 10.4 Ω Typ., 0.44 A Supermesh™ Power Mosfet In A Sot-223 PackageDocument12 pagesStn1Nk60Zl: N-Channel 600 V, 10.4 Ω Typ., 0.44 A Supermesh™ Power Mosfet In A Sot-223 PackageMarcos SilvaNo ratings yet

- STD3N62K3, STF3N62K3, Stu3n62k3Document27 pagesSTD3N62K3, STF3N62K3, Stu3n62k3David Alberto Lotero AlvarezNo ratings yet

- 9N80 UnisonicTechnologiesDocument6 pages9N80 UnisonicTechnologiesJlavieraNo ratings yet

- 8 N 80Document5 pages8 N 80pravin jadavNo ratings yet

- STR 2 P 3 LLH 6Document12 pagesSTR 2 P 3 LLH 6GERMANNo ratings yet

- STP80NF12Document12 pagesSTP80NF12vanuzalopeslopes1No ratings yet

- F10NK50Z STMicroelectronicsDocument13 pagesF10NK50Z STMicroelectronicsCandraBuanaNo ratings yet

- Rq3e100gntb RohmDocument13 pagesRq3e100gntb RohmWalter Martin Paz HolguinNo ratings yet

- STD 95 P 3 LLH 6 AgDocument16 pagesSTD 95 P 3 LLH 6 AgjkircsiNo ratings yet

- 30N06 DatasheetDocument8 pages30N06 DatasheetsongdashengNo ratings yet

- rcx220n25 eDocument15 pagesrcx220n25 eDarlan Vasconcelos CanezNo ratings yet

- Rohm S A0001611900 1-2561600Document14 pagesRohm S A0001611900 1-2561600RamonAngelNo ratings yet

- dm00128985 1798131Document13 pagesdm00128985 1798131Konstantin ИстинныйNo ratings yet

- 06n03Document8 pages06n03buba.kastorsNo ratings yet

- Data SheetDocument8 pagesData SheetSuyash SuyashNo ratings yet

- L30Esdxxxc3-2: Dual Esd Protection DiodesDocument5 pagesL30Esdxxxc3-2: Dual Esd Protection Diodeseisovic8No ratings yet

- 4NF20L STMicroelectronics PDFDocument12 pages4NF20L STMicroelectronics PDFTiago eletrônicaNo ratings yet

- 15 N 03 LDocument8 pages15 N 03 LJose M PeresNo ratings yet

- RDD023N50: 500V 5.4 2A V R (Max.) I PDocument16 pagesRDD023N50: 500V 5.4 2A V R (Max.) I PClareth Antonio Rodriguez LopezNo ratings yet

- Media 3323329Document6 pagesMedia 3323329Daniel MesiNo ratings yet

- STB12NM50T4, STP12NM50, STP12NM50FPDocument20 pagesSTB12NM50T4, STP12NM50, STP12NM50FPinformagicNo ratings yet

- STB 120 N 4 LF 6Document18 pagesSTB 120 N 4 LF 6Manuel QuirozNo ratings yet

- MDF9N50F MagnaChipDocument6 pagesMDF9N50F MagnaChipchokNo ratings yet

- Stw48Nm60N: N-Channel 600 V, 0.055 Ω Typ., 44 A Mdmesh™ Ii Power Mosfet In A To-247 PackageDocument13 pagesStw48Nm60N: N-Channel 600 V, 0.055 Ω Typ., 44 A Mdmesh™ Ii Power Mosfet In A To-247 PackageАлексей АндрияшNo ratings yet

- TPC 8122Document7 pagesTPC 8122Mafia BetawiNo ratings yet

- Unisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetDocument6 pagesUnisonic Technologies Co., LTD: 15A, 600V N-CHANNEL Power MosfetCode Main ProjectNo ratings yet

- Stp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetDocument7 pagesStp80Pf55: P-Channel 55V - 0.016 - 80A To-220 Stripfet Ii Power MosfetRadoslav RadoslavovNo ratings yet

- P-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataDocument10 pagesP-Channel Enhancement-Mode Silicon Gate: Semiconductor Technical DataAnonymous nQ4z7PNo ratings yet

- WPM 2341Document9 pagesWPM 2341veronicaNo ratings yet

- Stb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetDocument14 pagesStb35Nf10 Stp35Nf10: N-Channel 100V - 0.030 - 40A - D Pak/To-220 Low Gate Charge Stripfet™ Ii Power MosfetRichardNo ratings yet

- 12N50 PDFDocument6 pages12N50 PDFhectorsevillaNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Stotz - Air-Probes-And-RingsDocument8 pagesStotz - Air-Probes-And-Ringszeybek_144649143No ratings yet

- E7a JCB 3D DS Full Scan OcrDocument187 pagesE7a JCB 3D DS Full Scan OcrChirag BansalNo ratings yet

- Communication Systems and Technology: Engr Izhar HussainDocument14 pagesCommunication Systems and Technology: Engr Izhar HussainUmesh OadNo ratings yet

- EDC Lab Manual (Exp - 5)Document8 pagesEDC Lab Manual (Exp - 5)Osama AsgharNo ratings yet

- Jump To Navigationjump To Search: EuroplugDocument5 pagesJump To Navigationjump To Search: EuroplugqwertyNo ratings yet

- Gas Insulated SubstationDocument84 pagesGas Insulated SubstationRajmohan96% (25)

- AS324 Diodes PDFDocument14 pagesAS324 Diodes PDFPredrag NemcicNo ratings yet

- Silicon NPN Power Transistors: Savantic Semiconductor Product SpecificationDocument5 pagesSilicon NPN Power Transistors: Savantic Semiconductor Product Specificationangel bastidasNo ratings yet

- AVR B Brush Service Engineer Report 1Document18 pagesAVR B Brush Service Engineer Report 1Whr AdamNo ratings yet

- Sorting Ascending and DescendingDocument2 pagesSorting Ascending and DescendingBEN G.YNo ratings yet

- TC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateDocument8 pagesTC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateAmirNo ratings yet

- High Current 100amps and WireHarness TestDocument83 pagesHigh Current 100amps and WireHarness TestMuraliraj SanjeevNo ratings yet

- Section B Activity - 1Document7 pagesSection B Activity - 1Harsh ShahNo ratings yet

- Normas Eléctricas para VIADocument16 pagesNormas Eléctricas para VIAAntónio AlmeidaNo ratings yet

- DM7400Document4 pagesDM7400Diego PlNo ratings yet

- JVC Av-28eh1sug Chassis cp830Document33 pagesJVC Av-28eh1sug Chassis cp830Paun Rusalin LucianNo ratings yet

- Ece2034 Flexible-Electronics-And-Sensors TH 1.0 55 Ece2034 PDFDocument2 pagesEce2034 Flexible-Electronics-And-Sensors TH 1.0 55 Ece2034 PDFRithyshNo ratings yet

- RT 201 KrauseDocument45 pagesRT 201 Krausemallik789No ratings yet

- Fertilite IVF ClinicsDocument3 pagesFertilite IVF ClinicsXavier Med Pvt. LtdNo ratings yet

- Ficha Técnica Nimac 6-GFM-150G 12V 150ADocument2 pagesFicha Técnica Nimac 6-GFM-150G 12V 150AUlisesGómezNo ratings yet

- Hand SolderingDocument11 pagesHand SolderingMadiha ChNo ratings yet

- Student - PE Lab 23-24 SEE Exam Time TableDocument3 pagesStudent - PE Lab 23-24 SEE Exam Time TableacchuonsocialmediaNo ratings yet

- Electronics and Communication EngineeringDocument8 pagesElectronics and Communication Engineeringshamnadhm371No ratings yet

- SubMonitor ManualDocument20 pagesSubMonitor ManualAdrian CantaragiuNo ratings yet

- Mobile Charger Circuit Diagram, 100-220V AC - Circuits DIYDocument13 pagesMobile Charger Circuit Diagram, 100-220V AC - Circuits DIYSheshmal ShingneNo ratings yet

- Azimuth Steueung - EngDocument13 pagesAzimuth Steueung - EnglacothNo ratings yet

- 2019 National Level - Judging Criteria Live Coding Challenge With Reromicro (Secondary)Document12 pages2019 National Level - Judging Criteria Live Coding Challenge With Reromicro (Secondary)in lavaNo ratings yet

- LMP8646 Precision Current Limiter: Features Key SpecificationsDocument28 pagesLMP8646 Precision Current Limiter: Features Key SpecificationsHoàng Phú NguyễnNo ratings yet

- Antminer APW3 Power Supply Repair GuideDocument17 pagesAntminer APW3 Power Supply Repair GuidesalmodantasNo ratings yet

- Led Voltage/Current Ratings TableDocument2 pagesLed Voltage/Current Ratings TableSzSz RaccoonVandererNo ratings yet