Professional Documents

Culture Documents

digital-vlsi-design-faults

digital-vlsi-design-faults

Uploaded by

rajendra kulkarniCopyright:

Available Formats

You might also like

- Protection System Design For SubstationDocument35 pagesProtection System Design For SubstationTimon Tim100% (1)

- Sample and Hold CircuitsDocument16 pagesSample and Hold CircuitsPraveen AndrewNo ratings yet

- ASIC Interview Question & Answer - ASIC GateDocument7 pagesASIC Interview Question & Answer - ASIC Gateprodip7No ratings yet

- Ncit Project Proposal 6th SemDocument14 pagesNcit Project Proposal 6th SemSanjay Adhikari100% (1)

- UNIT III-Digital System DesignDocument13 pagesUNIT III-Digital System DesignNarasimha Murthy YayavaramNo ratings yet

- Ch3.Fault ModelingDocument47 pagesCh3.Fault ModelingMuhammad RizwanNo ratings yet

- Chap4 Lect04 Defects FaultsDocument18 pagesChap4 Lect04 Defects Faultsdigi1988No ratings yet

- Bridging FaultsDocument3 pagesBridging FaultsBha RathNo ratings yet

- Nandha Engineering College (Autonomous) E-AssignmentDocument6 pagesNandha Engineering College (Autonomous) E-Assignmentmonishabe23No ratings yet

- TestDocument38 pagesTestRAHA TUDUNo ratings yet

- 5.g 62 - Iddq VERSUS VM TESTING - A COMPARATIVE STUDYDocument6 pages5.g 62 - Iddq VERSUS VM TESTING - A COMPARATIVE STUDYVančo LitovskiNo ratings yet

- A Review of Methodologies For Testing and Locating Faults in Integrated CircuitsDocument3 pagesA Review of Methodologies For Testing and Locating Faults in Integrated CircuitsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- DFT - Fault Models - Semicon ShortsDocument5 pagesDFT - Fault Models - Semicon ShortsSai Uttej MandalaNo ratings yet

- Quiz_VLSI_DesignDocument7 pagesQuiz_VLSI_DesignSASANKNo ratings yet

- On Chip VariationDocument4 pagesOn Chip VariationsarvoscribNo ratings yet

- Fault Types and Models: Pathak Anushri Roll No.:208Document4 pagesFault Types and Models: Pathak Anushri Roll No.:208Dissen_cNo ratings yet

- Unit 5Document41 pagesUnit 5sparsh kaudinyaNo ratings yet

- Fault Isolation in Distributed Generation ConnectedDocument24 pagesFault Isolation in Distributed Generation ConnectedQais AlsafasfehNo ratings yet

- 8B-4 MOS TransistorDocument4 pages8B-4 MOS TransistorkammohNo ratings yet

- 16-Article Text-89-1-10-20191202Document11 pages16-Article Text-89-1-10-20191202okonkwo innocentNo ratings yet

- EC6601 VLSI Design Model QBDocument44 pagesEC6601 VLSI Design Model QBxperiaashNo ratings yet

- 04 - Logic and Fault ModelingDocument6 pages04 - Logic and Fault ModelingBasineni VenkatNo ratings yet

- Unit - 2: Asic Library Design O Delay EstimationDocument43 pagesUnit - 2: Asic Library Design O Delay EstimationhrrameshhrNo ratings yet

- Cmos Latch UpDocument3 pagesCmos Latch UpSiddharth SabharwalNo ratings yet

- SOC Unit 1 Part2Document24 pagesSOC Unit 1 Part2Karthick NpNo ratings yet

- Mod 4Document33 pagesMod 4Adi MohantyNo ratings yet

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsDocument31 pages15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- Vlsi Final Notes Unit4Document21 pagesVlsi Final Notes Unit4RohitParjapatNo ratings yet

- Course Design: Short Circuit Faults Based On MatlabDocument22 pagesCourse Design: Short Circuit Faults Based On MatlabMd mehadi HasanNo ratings yet

- Faisal2005 PDFDocument8 pagesFaisal2005 PDFAhas AlqNo ratings yet

- TelegramDocument20 pagesTelegramVani telluriNo ratings yet

- Antenna Ratio Definition For Vlsi Circuits Plasma Etch DamageDocument5 pagesAntenna Ratio Definition For Vlsi Circuits Plasma Etch DamageShin Tsz JianNo ratings yet

- Слободенюк доповільDocument10 pagesСлободенюк доповільko7tyaNo ratings yet

- Types of Faults Incables: Open Circuit FaultDocument4 pagesTypes of Faults Incables: Open Circuit FaultRajNo ratings yet

- Untitled 1Document62 pagesUntitled 1Roshan RajuNo ratings yet

- Staggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectDocument6 pagesStaggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectApikShafieeNo ratings yet

- Crosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueDocument10 pagesCrosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueRohit SinghNo ratings yet

- Design For Testability: N.Pitcheswara Rao Assistant Professor ECE DepartmentDocument47 pagesDesign For Testability: N.Pitcheswara Rao Assistant Professor ECE DepartmentRaoNo ratings yet

- Static 1 HazardDocument3 pagesStatic 1 HazardAchiket SinghNo ratings yet

- Novel Algorithm For Estimating The Distance of Open-Conductor Faults in HV Transmission Lines (2012) PDFDocument7 pagesNovel Algorithm For Estimating The Distance of Open-Conductor Faults in HV Transmission Lines (2012) PDFDanielAlejandroRamosQueroNo ratings yet

- Pitfalls and Fallacies: T DD T DDDocument1 pagePitfalls and Fallacies: T DD T DDCarlos SaavedraNo ratings yet

- TTL and CMOS FamiliesDocument7 pagesTTL and CMOS FamiliesFabian AvilaNo ratings yet

- CIGRE-129 Detection, Location, and Classification of Downed Conductors in Series-Compensated Transmission Lines PDFDocument8 pagesCIGRE-129 Detection, Location, and Classification of Downed Conductors in Series-Compensated Transmission Lines PDFEleazar Sierra EspinozaNo ratings yet

- Return Loss Prediction For Cascaded SystemsDocument9 pagesReturn Loss Prediction For Cascaded SystemsHoàng Minh ThịnhNo ratings yet

- Crosstalk:: Antenna Crosstalk and Reliability ChecksDocument13 pagesCrosstalk:: Antenna Crosstalk and Reliability Checkssharath_mbNo ratings yet

- Circuit FamiliesDocument26 pagesCircuit FamiliesSudh Desi ContentsNo ratings yet

- PP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsDocument6 pagesPP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsEditorijset IjsetNo ratings yet

- Ec2354/Vlsi Design Unit 1 - Cmos TechnologyDocument10 pagesEc2354/Vlsi Design Unit 1 - Cmos TechnologyPranav sharmaNo ratings yet

- Oscillators: 4.6 Troubleshooting Tips For Oscillator CircuitsDocument5 pagesOscillators: 4.6 Troubleshooting Tips For Oscillator CircuitsElla Mae AbayNo ratings yet

- Transactions Briefs: Testable Designs of Multiple Precharged Domino CircuitsDocument5 pagesTransactions Briefs: Testable Designs of Multiple Precharged Domino CircuitsSudhakar SpartanNo ratings yet

- Fast and Easily Implementable Detection CircuitsDocument9 pagesFast and Easily Implementable Detection CircuitsPablo Henrique Seibert JahnoNo ratings yet

- Next Generation VLSI CircuitsDocument5 pagesNext Generation VLSI CircuitssudhaaishNo ratings yet

- 55W - 14601 - 0 TDR Z MeasurementsDocument16 pages55W - 14601 - 0 TDR Z MeasurementsgiaonkNo ratings yet

- Relaying Short LinesDocument16 pagesRelaying Short LinesrogeriojuruaiaNo ratings yet

- Ee6301 DLC Eee Iiist Au Unit IVDocument15 pagesEe6301 DLC Eee Iiist Au Unit IVNiharica SohalNo ratings yet

- L02 FaultModelingDocument15 pagesL02 FaultModelingAmit RohillaNo ratings yet

- DLC Exp5 Student Manual-RevisedDocument6 pagesDLC Exp5 Student Manual-RevisedPial Hassan ChowdhuryNo ratings yet

- Unit 3 CMOS Inverter SwitchingDocument12 pagesUnit 3 CMOS Inverter SwitchingHarsh kumarNo ratings yet

- Hybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsDocument10 pagesHybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsLakshya KhandelwalNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- RSHH Qam13 Module 01 PDFDocument16 pagesRSHH Qam13 Module 01 PDFSteven PurnomoNo ratings yet

- 1st PUC Computer Lab Manual-2023Document69 pages1st PUC Computer Lab Manual-2023rishabh.rukmangadhaNo ratings yet

- MGT201 Term Project Fall 2020Document8 pagesMGT201 Term Project Fall 2020Tasnim ArpitaNo ratings yet

- Web-Based Blood Donation Management System Using QR Code and Sms Notification For Red Cross Batangas OfficeDocument37 pagesWeb-Based Blood Donation Management System Using QR Code and Sms Notification For Red Cross Batangas OfficefredNo ratings yet

- Setting Up OpenVPN GUI On Windows With Autologin - Network 2.0Document4 pagesSetting Up OpenVPN GUI On Windows With Autologin - Network 2.0jufore vokuNo ratings yet

- Notes Taken During 3 July APQP PPAP ClassDocument2 pagesNotes Taken During 3 July APQP PPAP Classrosemarie tolentinoNo ratings yet

- JDK TroubleshootingDocument19 pagesJDK TroubleshootingLuminita - Stefania SimionNo ratings yet

- Instagram Marketing PDFDocument72 pagesInstagram Marketing PDFneeloufershaik100% (1)

- RDL-3000 Troubleshooting Technology Guide: Terago Networks - RF TechnologyDocument17 pagesRDL-3000 Troubleshooting Technology Guide: Terago Networks - RF Technologyalex BecerraNo ratings yet

- Chinese Wall Security Model Buzulan and TeleghinDocument13 pagesChinese Wall Security Model Buzulan and TeleghinLoryQa LoryNo ratings yet

- Genaro Network Frequently Asked Questions: Part I: Genaro Concept, Technology and Ecosystem Related QuestionsDocument12 pagesGenaro Network Frequently Asked Questions: Part I: Genaro Concept, Technology and Ecosystem Related QuestionsRobert GenaroNo ratings yet

- Creating A Data Collection Form With Epicollect5Document11 pagesCreating A Data Collection Form With Epicollect5WirNo ratings yet

- Customer Segmentation Using Unsupervised Learning On Daily Energy Load ProfilesDocument7 pagesCustomer Segmentation Using Unsupervised Learning On Daily Energy Load ProfilesPablo OrricoNo ratings yet

- Cs501 Midterm Solved Mcqs by JunaidDocument20 pagesCs501 Midterm Solved Mcqs by JunaidTuba AkmalNo ratings yet

- Final Project ReportDocument48 pagesFinal Project ReportfazalabbasNo ratings yet

- Aindump2go - Az 305.PDF - Download.2022 Oct 08.by - Steven.81q.vceDocument24 pagesAindump2go - Az 305.PDF - Download.2022 Oct 08.by - Steven.81q.vceHakan NigraNo ratings yet

- ComicStripTemplatePagesforCreativeAssignments 2 PDFDocument34 pagesComicStripTemplatePagesforCreativeAssignments 2 PDFVanessa BarolakNo ratings yet

- Guidance On Skill Training AssessmentDocument7 pagesGuidance On Skill Training Assessmentanup kumarNo ratings yet

- HBL Payments - User Manual For Payment V1Document32 pagesHBL Payments - User Manual For Payment V1Nasir R AyubNo ratings yet

- Cse III Computer Organization (15cs34) SolutionDocument50 pagesCse III Computer Organization (15cs34) Solutiontalha telsangNo ratings yet

- Apple MacBook 2.1Document8 pagesApple MacBook 2.1Robert AndrejašNo ratings yet

- Manual Aparat de Etichetare Dymo Letratag 100h Dy19757 3047Document20 pagesManual Aparat de Etichetare Dymo Letratag 100h Dy19757 3047victorator767No ratings yet

- Super Mario Bros. - Main ThemeDocument2 pagesSuper Mario Bros. - Main ThemeannaNo ratings yet

- Geography - AE - AEE - Civil Engineering Handwritten Notes (CivilEnggForAll - Com) PDFDocument220 pagesGeography - AE - AEE - Civil Engineering Handwritten Notes (CivilEnggForAll - Com) PDFMANJUNo ratings yet

- Md. Raihan Habib: ObjectiveDocument2 pagesMd. Raihan Habib: ObjectiveNaiem AbdullahNo ratings yet

- Efam Construction LTD Training, Juba South Sudan, Hai Tarawa Residential Area., PH: 0928002457/0916002457 E-MailDocument2 pagesEfam Construction LTD Training, Juba South Sudan, Hai Tarawa Residential Area., PH: 0928002457/0916002457 E-MailLaki ENNo ratings yet

- BS (Information Technology) / BS (Software Engineering) : Bcsf16m526@pucit - Edu.pkDocument4 pagesBS (Information Technology) / BS (Software Engineering) : Bcsf16m526@pucit - Edu.pkaskbsjhvdjdNo ratings yet

- PL-300: Microsoft Power BI Data AnalystDocument5 pagesPL-300: Microsoft Power BI Data AnalystharisomanathNo ratings yet

- JC35DN enDocument11 pagesJC35DN enMohamed WahdanNo ratings yet

digital-vlsi-design-faults

digital-vlsi-design-faults

Uploaded by

rajendra kulkarniCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

digital-vlsi-design-faults

digital-vlsi-design-faults

Uploaded by

rajendra kulkarniCopyright:

Available Formats

lOMoARcPSD|19850482

Digital VLSI design- faults

Digital Vlsi Design (Delhi Technological University)

Scan to open on Studocu

Studocu is not sponsored or endorsed by any college or university

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

FAULTS AT LOGIC CIRCUITS

A failure is said to have occurred in a logic circuit or system if it deviates from its specified

behaviour. A fault, on the other hand, refers to a physical defect in a circuit. For example, a

short between two signal lines in the circuit or a break in a signal line is a physical defect. An

error is usually the manifestation of a fault in the circuit; thus, a fault may change the value

of a signal in a circuit from 0 (correct) to 1 (erroneous) or vice versa. However, a fault does

not always cause an error; in that case, the fault is considered to be latent.

A fault is characterized by its nature, value, extent, and duration. The nature of a fault can be

classified as logical or nonlogical. A logical fault causes the logic value at a point in a circuit

to become opposite to the specified value. Nonlogical faults include the rest of the faults such

as the malfunction of the clock signal, power failure, etc. The value of a logical fault at a

point in the circuit indicates whether the fault creates fixed or varying erroneous logical

values. The extent of a fault specifies whether the effect of the fault is localized or

distributed. A local fault affects only a single variable, whereas a distributed fault affects

more than one. A logical fault, for example, is a local fault, whereas the malfunction of the

clock is a distributed fault. The duration of a fault refers to whether the fault is permanent or

temporary.

1. Stuck-At Fault

The most common model used for logical faults is the single stuck-at fault. It assumes that a

fault in a logic gate result in one of its inputs or the output is fixed at either a logic 0 (stuck-

at-0) or at logic 1 (stuck-at-1). Stuck-at-0 and stuck-at-l faults are often abbreviated to s-a-0

and s-a-1, respectively.

Let us assume that in Fig.1 the A input of the NAND gate is s-a-1.

Figure 1: 2-input NAND gate

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

The NAND gate perceives the A input as a logic 1 irrespective of the logic value placed on

the input. For example, the output of the NAND gate is 0 for the input pattern A=0 and B=1,

when input A is s-a-1 in. In the absence of the fault, the output will be 1. Thus, AB=01 can be

considered as the test for the A input s-a-l, since there is a difference between the output of

the fault-free and faulty gate.

The single stuck-at fault model is often referred to as the classical fault model and offers a

good representation for the most common types of defects [e.g., shorts and opens in

complementary metal oxide semiconductor (CMOS) technology]. Fig. 2 illustrates the CMOS

realization of the two-input NAND.

Figure 2: CMOS realization of 2-input NAND

The number 1 in the figure indicates an open, whereas the numbers 2 and 3 identify the short

between the output node and the ground and the short between the output node and the VDD,

respectively. A short in a CMOS result if not enough metal is removed by the

photolithography, whereas over-removal of metal results in an open circuit. Fault 1 in Fig. 2

will disconnect input A from the gate of transistors T1 and T3. It has been shown that in such

a situation one transistor may conduct and the other remain nonconducting. Thus, the fault

can be represented by a stuck at value of A; if A is s-a-0, T1 will be ON and T3 OFF, and if A

is s-a-l, T1 will be OFF and T3 ON. Fault 2 forces the output node to be shorted to VDD, that

is, the fault can be considered as an s-a-l fault. Similarly, fault 3 forces the output node to be

s-a-0.

The stuck-at model is also used to represent multiple faults in circuits. In a multiple stuck-at

fault, it is assumed that more than one signal line in the circuit is stuck at logic 1 or logic 0; in

other words, a group of stuck-at faults exist in the circuit at the same time. A variation of the

multiple faults is the unidirectional fault. A multiple fault is unidirectional if all of its

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

constituent faults are either s-a-0 or s-a-l but not both simultaneously. The stuck-at model has

gained wide acceptance in the past mainly because of its relative success with small scale

integration. However, it is not very effective in accounting for all faults in present day very

large scale integrated (VLSI), circuits which mainly uses CMOS technology. Faults in CMOS

circuits do not necessarily produce logical faults that can be described as stuck-at faults. For

example, in Fig. 2, faults 3 and 4 create stuck-on transistors faults..

2. Bridging faults

Bridging faults form an important class of permanent faults that cannot be modelled as stuck-

at faults. A bridging fault is said to have occurred when two or more signal lines in a circuit

are accidentally connected together. Earlier study of bridging faults concentrated only on the

shorting of signal lines in gate-level circuits. It was shown that the shorting of lines resulted

in wired logic at the connection. Bridging faults at the gate level has been classified into two

types: input bridging and feedback bridging. An input bridging fault corresponds to the

shorting of a certain number of primary input lines. A feedback bridging fault results if there

is a short between an output and input line. A feedback bridging fault may cause a circuit to

oscillate, or it may convert it into a sequential circuit. Bridging faults in a transistor-level

circuit may occur between the terminals of a transistor or between two or more signal lines.

Fig. 3 shows the CMOS logic realization of the Boolean function:

Figure 3: CMOS implementation of function Z

A short between two lines, as indicated by the dotted line in the diagram will change the

function of the circuit.

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

The effect of bridging among the terminals of transistors is technology-dependent. For

example, in CMOS circuits, such faults manifest as either stuck-at or stuck-open faults,

depending on the physical location and the value of the bridging resistance.

3. Delay faults

As mentioned previously, not all manufacturing defects in VLSI circuits can be represented

by the stuck-at fault model. The size of a defect determines whether the defect will affect the

logic function of a circuit. Smaller defects, which are likely to cause partial open or short in a

circuit, have a higher probability of occurrence due to the statistical variations in the

manufacturing process. These defects result in the failure of a circuit to meet its timing

specifications without any alteration of the logic function of the circuit. A small defect may

delay the transition of a signal on a line either from 0 to 1, or vice versa. This type of

malfunction is modelled by a delay fault. Two types of delay faults have been proposed in

literature: gate delay fault and path delay fault. Gate delay faults have been used to model

defects that cause the actual propagation delay of a faulty gate to exceed its specified worst-

case value. For example, if the specified worst case propagation delay of a gate is x units and

the actual delay is x+∆x units, then the gate is said to have a delay fault of size ∆x. The main

deficiency of the gate delay fault model is that it can only be used to model isolated defects,

not distributed defects, for example, several small delay defects. The path delay fault model

can be used to model isolated as well as distributed defects. In this model, a fault is assumed

to have occurred if the propagation delay along a path in the circuit under test exceeds the

specified limit.

4. Stuck-On and Stuck-Open faults

A stuck-on transistor fault implies the permanent closing of the path between the source and

the drain of the transistor. Although the stuck-on transistor, in practice, behaves in a similar

way as a stuck-closed transistor, there is a subtle difference. A stuck-on transistor has the

same drain-source resistance as the on resistance of a fault-free transistor, whereas a stuck-

closed transistor exhibits a drain-source resistance that is significantly lower than the normal

on-resistance. In other words, in the case of stuck-closed transistor, the short between the

drain and the source is almost perfect, and this is not true for a stuck-on transistor. A

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

transistor stuck-on (stuck-closed) fault may be modelled as a bridging fault from the source to

the drain of a transistor. A stuck-open transistor implies the permanent opening of the

connection between the source and the drain of a transistor. The drain-source resistance of a

stuck-open transistor is significantly higher than the off-resistance of a nonfaulty transistor. If

the drain-source resistance of a faulty transistor is approximately equal to that of a fault-free

transistor, then the transistor is considered to be stuck-off. For all practical purposes,

transistor stuck-off and stuck-open faults are functionally equivalent.

Figure 4: CMOS implementation of 2-input NOR gate

A stuck-open transistor fault like a feedback bridging fault can turn a combinational circuit

into a sequential circuit. Fig. 4 shows a two-input CMOS NOR gate. A stuck-open fault

causes the output to be connected neither to GND nor to VDD. If, for example, transistor T2

is open-circuited, then for input AB=00, the pull-up circuit will not be active and there will be

no change in the output voltage. In fact, the output retains its previous logic state; however,

the length of time the state is retained is determined by the leakage current at the output node.

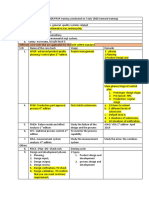

Table 1: Truth table of CMOS implementation of 2-input NOR gate with and without stuck-open fault

A B Z Z(As-op) Z(Bs-op) Z(VDD s-op)

0 0 1 1 1 Zt

0 1 0 0 Zt 0

1 0 0 Zt 0 0

1 1 0 0 0 0

Table 1 shows the truth table for the two-input CMOS NOR gate. The fault-free output is

shown in column Z; the three columns to the right represent the outputs in presence of the

three stuck-open (s-op) faults. The first, As-op, is caused by any input, drain, or source

missing connection to the pull-down FET T3. The second, Bs-op, is caused by any input,

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

drain, or source missing connection to the pull-down FET T4. The third, VDDs-op, is caused

by an open anywhere in the series, p-channel pull-up connection to VDD. The symbol Zt is

used to indicate that the output state retains the previous logic value.

5. Temporary faults

As stated earlier, an error is a manifestation of a fault. A temporary fault can result in an

intermittent or a transient error. Transient errors are the major source of failures in VLSI

chips. They are nonrecurring and are not repairable because there is no physical damage to

the hardware. Very deep submicron technology has enabled the packing of millions of

transistors on a VLSI chip by reducing the transistor dimensions. However, the reduction of

transistor sizes also reduces their noise margins. As a result, they become more vulnerable to

noise, cross-talk, etc., which in turn result in transient errors. In addition, small transistors are

affected by terrestrial radiation and suffer temporary malfunction, thereby increasing the rate

of transient errors. Intermittent faults are recurring faults that reappear on a regular basis.

Such faults can occur due to loosen connections, partially defective components, or poor

designs. Intermittent faults occurring due to deteriorating or aging components may

eventually become permanent. Some intermittent faults also occur due to environmental

conditions such as temperature, humidity, vibration, etc. The likelihood of such intermittent

faults depends on how well the system is protected from its physical environment through

shielding, filtering, cooling, etc. An intermittent fault in a circuit causes a malfunction of the

circuit only if it is active; if it is inactive, the circuit operates correctly. A circuit is said to be

in a fault active state if a fault present in the circuit is active, and it is said to be in the fault-

not-active state if a fault is present but inactive. Because intermittent faults are random, they

can be modelled only by using probabilistic methods.

6. Other types of faults

Assertion Fault: An assertion expresses a property of a high-level function in the form:

“antecedent consequent,” where antecedent and consequent can be simple predicates like

“line L takes symbolic value v” or conjunctions of simple predicates. An assertion fault

means that the corresponding property is not “true” for some input of the system. This fault

model has been used for generating tests for a microprocessor.

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

Behavioural Faults: When the behaviour of an electronic system is described in computer-

readable form, it is generally written in a programming language (such as C) or some other

hardware description language that resembles a programming language. At the behavioural

level, also referred to as functional or high level, the variables or operations are not

necessarily electrical, but correspond to the specific application domain. Behavioural faults

refer to incorrect execution of the language constructs used in the description. Examples of

behavioural faults are assertion faults, branch faults, and instruction faults. At the behavioural

level, software test metrics, such as statement coverage and branch coverage, and an

additional toggle coverage, are also used although these do not conform to any specific fault

model.

Branch Fault: This fault is modelled at the behavioural level where the circuit function is

described in a programming language. A branch fault affects a branch statement and causes it

to branch to an incorrect destination.

Cross-point Fault: These faults are modelled in programmable logic arrays (PLA.) In the

layout of a PLA, input and output variable lines are laid out perpendicular to the product-

lines. Crossing signal lines either form specific types of connections or remain unconnected

at cross-points, depending on the function implemented. There are two types of cross-point

faults. A missing cross-point means a missing connection at a crossing where a connection

was intended. An extra cross-point means a faulty connection at a crossing where no

connection was intended. Based on their influence on the logic function of the PLA, the

cross-point faults are further classified as shrinkage, growth, appearance, and disappearance

faults. Also see PLA faults.

Hyperactive Fault: A hyperactive fault causes a large number of signals in the circuit to

differ from their correct values. The fault thus produces very high fault related activity in the

circuit. If not readily detected, fault simulators usually remove hyperactive faults for later

consideration to save CPU time and memory.

Initialization Fault: Circuits with memory elements (e.g., flip-flops) are designed so that

they can be initialized by applying suitable input signals. Faults that interfere with such an

initialization procedure are called initialization faults. A typical example of such a fault is the

clock line of a flip-flop being stuck in the inactive state. Initialization faults are sometimes

detected as potentially detectable faults.

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

lOMoARcPSD|19850482

Logical Faults: These faults affect the state of logic signals. Normally, the state may be

modelled as {0, 1, X (unknown), Z (high impedance)}, and a fault can transform the correct

value to any other value. Several types of faults can be modelled at the logic level. However,

the term logical faults often imply stuck-at faults.

Memory Faults: Faults modelled in memory blocks are single cell stuck-at-[0, l] faults,

pattern sensitive faults, cell coupling faults, and single stuck-at faults in the address decoder

logic.

Non-classical Fault: Although a non-classical fault, in general, refers to a fault other than a

stuck-at fault, the term has been used for the stuck-open and stuck-short faults of MOS

technologies.

Oscillation Fault: These faults cause oscillating signals in the faulty circuit when the fault-

free circuit remains stable. Such a condition can occur due to certain single stuck-at faults in

sequential circuits that contain combinational feedback. Oscillations can also occur in a

purely combinational circuit if a bridging fault produces feedback. Oscillation faults are also

referred to as star-faults.

Parametric Fault: Such a fault changes the values of electrical parameters of active or

passive devices from their nominal or expected values. Examples are the threshold voltage of

a transistor (active device) and values of resistors and capacitors (passive devices.)

Downloaded by Dr Praveen Reddy (reddysirlogin@gmail.com)

You might also like

- Protection System Design For SubstationDocument35 pagesProtection System Design For SubstationTimon Tim100% (1)

- Sample and Hold CircuitsDocument16 pagesSample and Hold CircuitsPraveen AndrewNo ratings yet

- ASIC Interview Question & Answer - ASIC GateDocument7 pagesASIC Interview Question & Answer - ASIC Gateprodip7No ratings yet

- Ncit Project Proposal 6th SemDocument14 pagesNcit Project Proposal 6th SemSanjay Adhikari100% (1)

- UNIT III-Digital System DesignDocument13 pagesUNIT III-Digital System DesignNarasimha Murthy YayavaramNo ratings yet

- Ch3.Fault ModelingDocument47 pagesCh3.Fault ModelingMuhammad RizwanNo ratings yet

- Chap4 Lect04 Defects FaultsDocument18 pagesChap4 Lect04 Defects Faultsdigi1988No ratings yet

- Bridging FaultsDocument3 pagesBridging FaultsBha RathNo ratings yet

- Nandha Engineering College (Autonomous) E-AssignmentDocument6 pagesNandha Engineering College (Autonomous) E-Assignmentmonishabe23No ratings yet

- TestDocument38 pagesTestRAHA TUDUNo ratings yet

- 5.g 62 - Iddq VERSUS VM TESTING - A COMPARATIVE STUDYDocument6 pages5.g 62 - Iddq VERSUS VM TESTING - A COMPARATIVE STUDYVančo LitovskiNo ratings yet

- A Review of Methodologies For Testing and Locating Faults in Integrated CircuitsDocument3 pagesA Review of Methodologies For Testing and Locating Faults in Integrated CircuitsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- DFT - Fault Models - Semicon ShortsDocument5 pagesDFT - Fault Models - Semicon ShortsSai Uttej MandalaNo ratings yet

- Quiz_VLSI_DesignDocument7 pagesQuiz_VLSI_DesignSASANKNo ratings yet

- On Chip VariationDocument4 pagesOn Chip VariationsarvoscribNo ratings yet

- Fault Types and Models: Pathak Anushri Roll No.:208Document4 pagesFault Types and Models: Pathak Anushri Roll No.:208Dissen_cNo ratings yet

- Unit 5Document41 pagesUnit 5sparsh kaudinyaNo ratings yet

- Fault Isolation in Distributed Generation ConnectedDocument24 pagesFault Isolation in Distributed Generation ConnectedQais AlsafasfehNo ratings yet

- 8B-4 MOS TransistorDocument4 pages8B-4 MOS TransistorkammohNo ratings yet

- 16-Article Text-89-1-10-20191202Document11 pages16-Article Text-89-1-10-20191202okonkwo innocentNo ratings yet

- EC6601 VLSI Design Model QBDocument44 pagesEC6601 VLSI Design Model QBxperiaashNo ratings yet

- 04 - Logic and Fault ModelingDocument6 pages04 - Logic and Fault ModelingBasineni VenkatNo ratings yet

- Unit - 2: Asic Library Design O Delay EstimationDocument43 pagesUnit - 2: Asic Library Design O Delay EstimationhrrameshhrNo ratings yet

- Cmos Latch UpDocument3 pagesCmos Latch UpSiddharth SabharwalNo ratings yet

- SOC Unit 1 Part2Document24 pagesSOC Unit 1 Part2Karthick NpNo ratings yet

- Mod 4Document33 pagesMod 4Adi MohantyNo ratings yet

- 15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsDocument31 pages15A04802-Low Power VLSI Circuits & Systems - Two Marks Q&A-5 UnitsPallavi Ch71% (7)

- Vlsi Final Notes Unit4Document21 pagesVlsi Final Notes Unit4RohitParjapatNo ratings yet

- Course Design: Short Circuit Faults Based On MatlabDocument22 pagesCourse Design: Short Circuit Faults Based On MatlabMd mehadi HasanNo ratings yet

- Faisal2005 PDFDocument8 pagesFaisal2005 PDFAhas AlqNo ratings yet

- TelegramDocument20 pagesTelegramVani telluriNo ratings yet

- Antenna Ratio Definition For Vlsi Circuits Plasma Etch DamageDocument5 pagesAntenna Ratio Definition For Vlsi Circuits Plasma Etch DamageShin Tsz JianNo ratings yet

- Слободенюк доповільDocument10 pagesСлободенюк доповільko7tyaNo ratings yet

- Types of Faults Incables: Open Circuit FaultDocument4 pagesTypes of Faults Incables: Open Circuit FaultRajNo ratings yet

- Untitled 1Document62 pagesUntitled 1Roshan RajuNo ratings yet

- Staggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectDocument6 pagesStaggered Latch Bus A Reliable Offset Switched Architecture For Long On-Chip InterconnectApikShafieeNo ratings yet

- Crosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueDocument10 pagesCrosstalk & Power Reduction in On Chip-VLSI Interconnect by Using Bus Encoding TechniqueRohit SinghNo ratings yet

- Design For Testability: N.Pitcheswara Rao Assistant Professor ECE DepartmentDocument47 pagesDesign For Testability: N.Pitcheswara Rao Assistant Professor ECE DepartmentRaoNo ratings yet

- Static 1 HazardDocument3 pagesStatic 1 HazardAchiket SinghNo ratings yet

- Novel Algorithm For Estimating The Distance of Open-Conductor Faults in HV Transmission Lines (2012) PDFDocument7 pagesNovel Algorithm For Estimating The Distance of Open-Conductor Faults in HV Transmission Lines (2012) PDFDanielAlejandroRamosQueroNo ratings yet

- Pitfalls and Fallacies: T DD T DDDocument1 pagePitfalls and Fallacies: T DD T DDCarlos SaavedraNo ratings yet

- TTL and CMOS FamiliesDocument7 pagesTTL and CMOS FamiliesFabian AvilaNo ratings yet

- CIGRE-129 Detection, Location, and Classification of Downed Conductors in Series-Compensated Transmission Lines PDFDocument8 pagesCIGRE-129 Detection, Location, and Classification of Downed Conductors in Series-Compensated Transmission Lines PDFEleazar Sierra EspinozaNo ratings yet

- Return Loss Prediction For Cascaded SystemsDocument9 pagesReturn Loss Prediction For Cascaded SystemsHoàng Minh ThịnhNo ratings yet

- Crosstalk:: Antenna Crosstalk and Reliability ChecksDocument13 pagesCrosstalk:: Antenna Crosstalk and Reliability Checkssharath_mbNo ratings yet

- Circuit FamiliesDocument26 pagesCircuit FamiliesSudh Desi ContentsNo ratings yet

- PP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsDocument6 pagesPP 59-64 Superiority of Current Mode Over Voltage Mode InterconnectsEditorijset IjsetNo ratings yet

- Ec2354/Vlsi Design Unit 1 - Cmos TechnologyDocument10 pagesEc2354/Vlsi Design Unit 1 - Cmos TechnologyPranav sharmaNo ratings yet

- Oscillators: 4.6 Troubleshooting Tips For Oscillator CircuitsDocument5 pagesOscillators: 4.6 Troubleshooting Tips For Oscillator CircuitsElla Mae AbayNo ratings yet

- Transactions Briefs: Testable Designs of Multiple Precharged Domino CircuitsDocument5 pagesTransactions Briefs: Testable Designs of Multiple Precharged Domino CircuitsSudhakar SpartanNo ratings yet

- Fast and Easily Implementable Detection CircuitsDocument9 pagesFast and Easily Implementable Detection CircuitsPablo Henrique Seibert JahnoNo ratings yet

- Next Generation VLSI CircuitsDocument5 pagesNext Generation VLSI CircuitssudhaaishNo ratings yet

- 55W - 14601 - 0 TDR Z MeasurementsDocument16 pages55W - 14601 - 0 TDR Z MeasurementsgiaonkNo ratings yet

- Relaying Short LinesDocument16 pagesRelaying Short LinesrogeriojuruaiaNo ratings yet

- Ee6301 DLC Eee Iiist Au Unit IVDocument15 pagesEe6301 DLC Eee Iiist Au Unit IVNiharica SohalNo ratings yet

- L02 FaultModelingDocument15 pagesL02 FaultModelingAmit RohillaNo ratings yet

- DLC Exp5 Student Manual-RevisedDocument6 pagesDLC Exp5 Student Manual-RevisedPial Hassan ChowdhuryNo ratings yet

- Unit 3 CMOS Inverter SwitchingDocument12 pagesUnit 3 CMOS Inverter SwitchingHarsh kumarNo ratings yet

- Hybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsDocument10 pagesHybrid Passive-Overcurrent Relay For Detection of Faults in Low-Voltage DC GridsLakshya KhandelwalNo ratings yet

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsFrom EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- RSHH Qam13 Module 01 PDFDocument16 pagesRSHH Qam13 Module 01 PDFSteven PurnomoNo ratings yet

- 1st PUC Computer Lab Manual-2023Document69 pages1st PUC Computer Lab Manual-2023rishabh.rukmangadhaNo ratings yet

- MGT201 Term Project Fall 2020Document8 pagesMGT201 Term Project Fall 2020Tasnim ArpitaNo ratings yet

- Web-Based Blood Donation Management System Using QR Code and Sms Notification For Red Cross Batangas OfficeDocument37 pagesWeb-Based Blood Donation Management System Using QR Code and Sms Notification For Red Cross Batangas OfficefredNo ratings yet

- Setting Up OpenVPN GUI On Windows With Autologin - Network 2.0Document4 pagesSetting Up OpenVPN GUI On Windows With Autologin - Network 2.0jufore vokuNo ratings yet

- Notes Taken During 3 July APQP PPAP ClassDocument2 pagesNotes Taken During 3 July APQP PPAP Classrosemarie tolentinoNo ratings yet

- JDK TroubleshootingDocument19 pagesJDK TroubleshootingLuminita - Stefania SimionNo ratings yet

- Instagram Marketing PDFDocument72 pagesInstagram Marketing PDFneeloufershaik100% (1)

- RDL-3000 Troubleshooting Technology Guide: Terago Networks - RF TechnologyDocument17 pagesRDL-3000 Troubleshooting Technology Guide: Terago Networks - RF Technologyalex BecerraNo ratings yet

- Chinese Wall Security Model Buzulan and TeleghinDocument13 pagesChinese Wall Security Model Buzulan and TeleghinLoryQa LoryNo ratings yet

- Genaro Network Frequently Asked Questions: Part I: Genaro Concept, Technology and Ecosystem Related QuestionsDocument12 pagesGenaro Network Frequently Asked Questions: Part I: Genaro Concept, Technology and Ecosystem Related QuestionsRobert GenaroNo ratings yet

- Creating A Data Collection Form With Epicollect5Document11 pagesCreating A Data Collection Form With Epicollect5WirNo ratings yet

- Customer Segmentation Using Unsupervised Learning On Daily Energy Load ProfilesDocument7 pagesCustomer Segmentation Using Unsupervised Learning On Daily Energy Load ProfilesPablo OrricoNo ratings yet

- Cs501 Midterm Solved Mcqs by JunaidDocument20 pagesCs501 Midterm Solved Mcqs by JunaidTuba AkmalNo ratings yet

- Final Project ReportDocument48 pagesFinal Project ReportfazalabbasNo ratings yet

- Aindump2go - Az 305.PDF - Download.2022 Oct 08.by - Steven.81q.vceDocument24 pagesAindump2go - Az 305.PDF - Download.2022 Oct 08.by - Steven.81q.vceHakan NigraNo ratings yet

- ComicStripTemplatePagesforCreativeAssignments 2 PDFDocument34 pagesComicStripTemplatePagesforCreativeAssignments 2 PDFVanessa BarolakNo ratings yet

- Guidance On Skill Training AssessmentDocument7 pagesGuidance On Skill Training Assessmentanup kumarNo ratings yet

- HBL Payments - User Manual For Payment V1Document32 pagesHBL Payments - User Manual For Payment V1Nasir R AyubNo ratings yet

- Cse III Computer Organization (15cs34) SolutionDocument50 pagesCse III Computer Organization (15cs34) Solutiontalha telsangNo ratings yet

- Apple MacBook 2.1Document8 pagesApple MacBook 2.1Robert AndrejašNo ratings yet

- Manual Aparat de Etichetare Dymo Letratag 100h Dy19757 3047Document20 pagesManual Aparat de Etichetare Dymo Letratag 100h Dy19757 3047victorator767No ratings yet

- Super Mario Bros. - Main ThemeDocument2 pagesSuper Mario Bros. - Main ThemeannaNo ratings yet

- Geography - AE - AEE - Civil Engineering Handwritten Notes (CivilEnggForAll - Com) PDFDocument220 pagesGeography - AE - AEE - Civil Engineering Handwritten Notes (CivilEnggForAll - Com) PDFMANJUNo ratings yet

- Md. Raihan Habib: ObjectiveDocument2 pagesMd. Raihan Habib: ObjectiveNaiem AbdullahNo ratings yet

- Efam Construction LTD Training, Juba South Sudan, Hai Tarawa Residential Area., PH: 0928002457/0916002457 E-MailDocument2 pagesEfam Construction LTD Training, Juba South Sudan, Hai Tarawa Residential Area., PH: 0928002457/0916002457 E-MailLaki ENNo ratings yet

- BS (Information Technology) / BS (Software Engineering) : Bcsf16m526@pucit - Edu.pkDocument4 pagesBS (Information Technology) / BS (Software Engineering) : Bcsf16m526@pucit - Edu.pkaskbsjhvdjdNo ratings yet

- PL-300: Microsoft Power BI Data AnalystDocument5 pagesPL-300: Microsoft Power BI Data AnalystharisomanathNo ratings yet

- JC35DN enDocument11 pagesJC35DN enMohamed WahdanNo ratings yet