Professional Documents

Culture Documents

Analog Design Journal

Analog Design Journal

Uploaded by

Oscar SuarezCopyright:

Available Formats

You might also like

- Analog IC Design With Low-Dropout RegulatorsDocument373 pagesAnalog IC Design With Low-Dropout RegulatorsHoang le Huy67% (3)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Project Report Speed Control of Induction MotorDocument47 pagesProject Report Speed Control of Induction Motorsrajaprojects0% (1)

- Exercise 4 Iron Tower Lighting ControlDocument6 pagesExercise 4 Iron Tower Lighting ControlJude Philip MaglasangNo ratings yet

- Simulation of Buck Boost ConverterDocument4 pagesSimulation of Buck Boost Converterganeshkurapati_15512No ratings yet

- Delomatic 3, SCM-1, Synchronising-Measuring Module 4921240056 UKDocument3 pagesDelomatic 3, SCM-1, Synchronising-Measuring Module 4921240056 UKВупсень ПупсеньNo ratings yet

- Uses DBX 146221Document8 pagesUses DBX 146221shirtquittersNo ratings yet

- Buie UpgradeDocument4 pagesBuie UpgradeNatasaBugaian100% (1)

- Direct Digital Synthesis Controlled Pure Sine Wave InverterDocument17 pagesDirect Digital Synthesis Controlled Pure Sine Wave InverterNabil MohammadNo ratings yet

- Design of Digital Controller For Switch Mode Power Supply: Presented by Santwana Kumari SO/CDocument25 pagesDesign of Digital Controller For Switch Mode Power Supply: Presented by Santwana Kumari SO/CShuaib Ahmad KhanNo ratings yet

- Sisngle Phase RectifierDocument5 pagesSisngle Phase RectifiermücahitNo ratings yet

- 500-kHz Half-Bridge DC-DC ConverterDocument17 pages500-kHz Half-Bridge DC-DC Converteratkxyz777100% (1)

- Zenith ZTG Transfer Switch: Spec SheetDocument15 pagesZenith ZTG Transfer Switch: Spec SheetDomenico SarcinaNo ratings yet

- Speed Control of DC Motor Using PDocument22 pagesSpeed Control of DC Motor Using PAnanth Sai YadavNo ratings yet

- Signal ProcessingDocument47 pagesSignal ProcessingAthira rcNo ratings yet

- AND8273/D Design of A 100 W Active Clamp Forward DC DC Converter For Telecom Systems Using The NCP1562Document20 pagesAND8273/D Design of A 100 W Active Clamp Forward DC DC Converter For Telecom Systems Using The NCP1562Elie IlokoNo ratings yet

- Dual Active BrdigeDocument20 pagesDual Active Brdigeayush sharmaNo ratings yet

- Multilevel InverterDocument74 pagesMultilevel InverterRaghu Selvaraj100% (4)

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- Digital Power-Conversion For The Analog EngineerDocument12 pagesDigital Power-Conversion For The Analog EngineerfjwoemcuNo ratings yet

- MPPT - Maximum Power Point TrackingDocument9 pagesMPPT - Maximum Power Point TrackingSanjeev ReddyNo ratings yet

- A Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterDocument6 pagesA Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterKPCYP COHODNo ratings yet

- MAX9979Document60 pagesMAX9979justcatchmenowNo ratings yet

- LNK605 DatasheetDocument18 pagesLNK605 DatasheetdgujarathiNo ratings yet

- Closed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLABDocument9 pagesClosed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLAB7031 GauravNo ratings yet

- Transformer protection systemDocument57 pagesTransformer protection systemAnkit RajNo ratings yet

- Slyt 718Document5 pagesSlyt 718wartchev39No ratings yet

- MegaMoto Plus Motor Control Shield For ArduinoDocument13 pagesMegaMoto Plus Motor Control Shield For ArduinosiogNo ratings yet

- An Open-Loop Stepper Motor Driver Based On FPGADocument5 pagesAn Open-Loop Stepper Motor Driver Based On FPGADivya JamesNo ratings yet

- Controller Design For Buck Converter Step-by-Step Approach: Swapna ManurkarDocument3 pagesController Design For Buck Converter Step-by-Step Approach: Swapna ManurkarJessica RossNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Gate Driver Circuit For Three Phase InverterDocument13 pagesGate Driver Circuit For Three Phase InverterMarc TcheukabaNo ratings yet

- EI5007W2Document17 pagesEI5007W2PyiAungNo ratings yet

- LM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsDocument10 pagesLM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsBejoy ThomasNo ratings yet

- Chapter No.:-01 Introuuction: Pulse-Width Modulation (PWM), Modulation (PDM)Document63 pagesChapter No.:-01 Introuuction: Pulse-Width Modulation (PWM), Modulation (PDM)Pooja BanNo ratings yet

- Adc 0808Document6 pagesAdc 0808GokulThalaNo ratings yet

- Design and Implementation of Parallel Connected DC-DC Buck ConvertersDocument6 pagesDesign and Implementation of Parallel Connected DC-DC Buck ConvertersColzi ChenNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Arduino Driving Power Mosfet uRiZsEVG6kDocument11 pagesArduino Driving Power Mosfet uRiZsEVG6kahas viyanaNo ratings yet

- University of Engineering & Technology LahoreDocument43 pagesUniversity of Engineering & Technology LahoreKantesh KumarNo ratings yet

- Analog To Digital ConvertDocument20 pagesAnalog To Digital ConvertluxiaofengNo ratings yet

- ADIC ExperimentsDocument41 pagesADIC ExperimentsTushar PatilNo ratings yet

- Chapter One Controlling The Operation of Wind-Solar Hybrid Power System Using Arduino-Based Hybrid MPPT ControllerDocument48 pagesChapter One Controlling The Operation of Wind-Solar Hybrid Power System Using Arduino-Based Hybrid MPPT ControllerOdebunmi NathanielNo ratings yet

- Training Curriculum: TIA Portal Module 009Document27 pagesTraining Curriculum: TIA Portal Module 009Hải Nguyễn KhắcNo ratings yet

- VE Transfer Switch-Pdf-EnDocument9 pagesVE Transfer Switch-Pdf-EnAnte MilanovićNo ratings yet

- 1999apr08 Icd PD Tac2Document11 pages1999apr08 Icd PD Tac2King GervinhoNo ratings yet

- LSC Presentation: Topic:-Dual Slope A/D ConvertorDocument8 pagesLSC Presentation: Topic:-Dual Slope A/D ConvertorSatyakam JhaNo ratings yet

- Diy Boost CalcDocument6 pagesDiy Boost Calckutu32No ratings yet

- Design Report Pss20Document46 pagesDesign Report Pss20Jaciel LMNo ratings yet

- A Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDDocument9 pagesA Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDAndrés ToroNo ratings yet

- Microchip CLC DescriptionDocument12 pagesMicrochip CLC DescriptionKamlesh YadavNo ratings yet

- Unit 2 - NewDocument61 pagesUnit 2 - NewMonster AmanNo ratings yet

- ELC Brosure Eng 08Document10 pagesELC Brosure Eng 08RunhydroNo ratings yet

- Dem 60 CDocument3 pagesDem 60 Cmohannad87No ratings yet

- AMPS - 2x - 2M2.3BWD3 3L V850 MV34.5Document38 pagesAMPS - 2x - 2M2.3BWD3 3L V850 MV34.5Josue Crespo GonzalezNo ratings yet

- Synchronization PanelDocument31 pagesSynchronization PanelHariom ChaurasiyaNo ratings yet

- 004 Pwm-OcxiDocument7 pages004 Pwm-OcxiNeodymeNo ratings yet

- Power Factor Correction AC-DC ConverterDocument5 pagesPower Factor Correction AC-DC Convertermatadamahesh1No ratings yet

- ABSTRACT: The Transformer Is A Static Device, Which ConvertsDocument15 pagesABSTRACT: The Transformer Is A Static Device, Which Convertsindhu kaviNo ratings yet

- PW2 MCDDocument5 pagesPW2 MCDUlul AzmiNo ratings yet

- Automatic Static Transfer SwitchDocument2 pagesAutomatic Static Transfer Switchanoop13No ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Ruso 6Document1 pageRuso 6Oscar SuarezNo ratings yet

- Ruso 2Document1 pageRuso 2Oscar SuarezNo ratings yet

- Ruso 4Document1 pageRuso 4Oscar SuarezNo ratings yet

- Ruso 3Document1 pageRuso 3Oscar SuarezNo ratings yet

- UNDP PV BookletDocument20 pagesUNDP PV BookletZeina RammalNo ratings yet

- ARM-A Mandatory PrimerDocument4 pagesARM-A Mandatory PrimervigneshwaranjNo ratings yet

- Vista RG750-V2 - Englisch ManualDocument9 pagesVista RG750-V2 - Englisch Manualsorsricerche100% (1)

- Micro ControllerDocument41 pagesMicro ControllerSaravana RajaNo ratings yet

- Ade NotesDocument128 pagesAde NotesKiranmai KonduruNo ratings yet

- FM 24-11 Tactical Satellite CommunicationsDocument90 pagesFM 24-11 Tactical Satellite CommunicationsMark CheneyNo ratings yet

- Operating Instructions Specification Hiperface Motor Feedback Protocol Neutral IM0064865Document79 pagesOperating Instructions Specification Hiperface Motor Feedback Protocol Neutral IM0064865Mohammad MorassaeiNo ratings yet

- Chemistry Project For Class 12 Topic: Saturated Solution: Measuring SolubilityDocument13 pagesChemistry Project For Class 12 Topic: Saturated Solution: Measuring SolubilityNishith Naik100% (1)

- 06 639Document28 pages06 639erve17No ratings yet

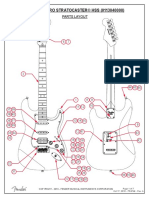

- Fender Am Pro Stratocaster HSS Manual y PartesDocument7 pagesFender Am Pro Stratocaster HSS Manual y PartesMario Orlando NerioNo ratings yet

- Relay MY2NDocument16 pagesRelay MY2NSofyan AndikaNo ratings yet

- JNTUK Computer Organization Nov 2015 Question PaperDocument4 pagesJNTUK Computer Organization Nov 2015 Question PaperTSRKNo ratings yet

- Dist RelayDocument6 pagesDist RelaymakroumNo ratings yet

- Chap04 (12 21 06) PDFDocument66 pagesChap04 (12 21 06) PDFHassan FarssiNo ratings yet

- MainDocument2,929 pagesMainanon_172022236No ratings yet

- 5200236-00A - Salwico AC-IR-3Fq - Addressable-Conventional IR Flame DetectorDocument4 pages5200236-00A - Salwico AC-IR-3Fq - Addressable-Conventional IR Flame DetectorcembozNo ratings yet

- Power Semiconductors and Power Supplies PDFDocument132 pagesPower Semiconductors and Power Supplies PDFtranhuutuongNo ratings yet

- Chinna Resume1Document3 pagesChinna Resume1saisurenNo ratings yet

- Unidirectional LED Based Solar Light (TorchDocument6 pagesUnidirectional LED Based Solar Light (TorchDeepak PrmNo ratings yet

- Name: Vinit J Faria Roll No. 157 STD: S.Y.J.C. (Science) Div: II Elphinstone CollegeDocument9 pagesName: Vinit J Faria Roll No. 157 STD: S.Y.J.C. (Science) Div: II Elphinstone CollegeNikit FariaNo ratings yet

- ALIA Manual AVF7000Document26 pagesALIA Manual AVF7000Abid HameedNo ratings yet

- Service Manual: VCR 5300 VCR 4300 VCR 2300Document110 pagesService Manual: VCR 5300 VCR 4300 VCR 2300wid9981No ratings yet

- Atmega168pa Au AtmelDocument419 pagesAtmega168pa Au AtmelDeibis Francisco Paredes HurtadoNo ratings yet

- Nx301a 1Document2 pagesNx301a 1AhmadAfiqNo ratings yet

- KX-FP207FX-S KX-FP218FX-S: Compact Plain Paper Fax (With Digital Answering System)Document232 pagesKX-FP207FX-S KX-FP218FX-S: Compact Plain Paper Fax (With Digital Answering System)ValeriiNo ratings yet

- What Is A Lecher AntennaDocument4 pagesWhat Is A Lecher AntennaPt AkaashNo ratings yet

- PAW3805EK-CJV2 Brief-V1.3 27062017Document1 pagePAW3805EK-CJV2 Brief-V1.3 27062017rreglosNo ratings yet

Analog Design Journal

Analog Design Journal

Uploaded by

Oscar SuarezCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Analog Design Journal

Analog Design Journal

Uploaded by

Oscar SuarezCopyright:

Available Formats

Analog Design Journal Power

How to parallel two DC/DC converters with

digital controllers

By Bosheng Sun, Application Engineer, High Voltage

Ian Bower, Firmware Engineer, High Voltage

Introduction converter with the higher voltage will provide most of

In high-power applications or N+1 redundant power the current to the load. This will cause two side effects.

systems, two or more power converters are connected in First, the converter with the high output current suffers

parallel to provide power to the load, thus increasing the high stress and thus reduced reliability. Second, over-

amount of current available. current protection may be triggered and shut down the

However, parallel operation is not as simple as just converter.

connecting the outputs together; it brings new challenges. • Simultaneous startup: If a heavy load is already

A properly operating parallel system should meet these applied during startup and one converter starts up ear-

criteria: lier than the other, it has to provide all of the load cur-

• Interleaving: Interleaving means that the switching rent. Overcurrent protection may be triggered and shut

frequency of the second power converter should be down the converter, causing startup to fail.

phase-shifted relative to the first converter in order to Not every controller has integrated these functions,

evenly space the power pulses. Proper interleaving especially digital controllers. On the other hand, digital

reduces the voltage ripple of the combined converters, controllers dominate systems where parallel operation is

resulting in potential output-capacitance reduction and mandatory. Although most digital controllers have a

cost savings. Different topologies require different synchronize pin and some digital controllers even have a

degrees of shift. For two buck converters, the phase current-sharing pin, they won’t do proper interleaving and

should shift by 180 degrees. For two full-bridge convert- current sharing if the pins are simply connected together.

ers, because the frequency of output pulses is twice the Because of component tolerance, they will most likely not

switching frequency, a phase shift of 90 degrees is start up simultaneously either.

appropriate. It is important to define and implement a proper parallel-

• Current sharing: Due to the component tolerance, the operation algorithm. This article uses two UCD3138-

output voltages of the power converters will not be controlled, phase-shift full-bridge DC/DC converters to

exactly the same. A slight difference in output voltage implement these functions. Figure 1 shows the hardware

will cause a huge difference in output current; thus the connections.

Figure 1. Parallel operation of two phase-shift

full-bridge DC/DC converters

Phase-Shift Full Bridge

+ (Master) +

VOUT

–

VIN DPWM0A

UCD3138 PWM0

GPIO

– Load

+

DC

–

Phase-Shift Full Bridge

+ (Slave) +

VOUT

–

VIN GPIO

UCD3138 TCAP

– SYNC

Texas Instruments 1 ADJ 3Q 2018

Analog Design Journal Power

Interleaving • The master should keep sending SYNC and PWM0

Like most digital controllers, the UCD3138 has a SYNC pin signals even if it shuts down due to fault protection.

that can synchronize pulse-width modulation (PWM) • During normal operation, the master continues sending

outputs to an external signal. One power converter, desig- out the PWM0 signal; the slave continues measuring this

nated as the master, can generate a synchronize signal signal and adjusting its switching frequency to match

(DPWM0A in this example) that equals its switching the master. This way, the slave will track the master’s

frequency but is phase-shifted 90 degrees. Connecting this switching frequency as temperature and clock frequen-

signal to the SYNC pin of the other power converter cies change.

(designated as slave) and configuring the slave to synchro- Figures 2 and 3 show test results. Figure 2 is the fixed-

nize to it will shift the slave’s switching frequency by leg PWM waveform after interleaving. Note that the

90 degrees. master and slave channels are phase-shifted by 90 degrees.

However, there’s a problem: because of component Figure 3 is the output voltage before the output inductor.

tolerances, no two controllers have exactly the same inter- Its frequency is twice the switching frequency and the

nal clock frequency. Moreover, the clock frequency master and slave signals are well interleaved. The inductor-

changes with temperature; even if the two clock frequen- current pulses are 180 degrees out of phase.

cies are close at room temperature, they can be different

when the temperature changes. If the master and slave

clock frequencies are significantly different, forcing them Figure 2. Master and slave PWM signals

to synchronize may cause PWM pulse stretching or

missing pulses, resulting in power-stage damage.

Therefore, the first thing to do is to match the switching

frequencies. To do that, the slave converter needs to know Master PWM

the master’s switching frequency. One option is to (2 V/div)

measure the frequency of the SYNC signal because it

matches the master’s switching frequency. However, the

SYNC signal is high frequency and the capture function of

the UCD3138 has limited resolution. The frequency

measurement may not be accurate enough.

For a more accurate measurement, let the master

converter generate another PWM signal (PWM0 in this Slave PWM

(2 V/div)

example) with a much lower frequency and send this

signal to the timer-capture (TCAP) pin of the slave Time (4 µs/div)

converter. The slave converter captures this signal and

determines the switching frequency of the master, and

then adjusts its switching frequency to match. Once this

Figure 3. Master and slave secondary

process is complete, it is safe to enable the synchroniza- switch-node voltage

tion function. The two converters will now be interleaved.

There is a general-purpose input/output (GPIO) signal

from slave to master in this configuration used for simulta-

neous startup, which will be discussed later.

Here are some things to note about Figure 1: Master Switch Node

(10 V/div)

• The SYNC signal is rising-edge-triggered in this example.

• The phase-shift full-bridge topology has two legs: a fixed

leg where the PWM waveform is fixed and a shifted leg

where the PWM is phase-shifted to the fixed leg. The

SYNC signal should be 90 degrees phase-delayed to the

PWM waveform of the master’s fixed leg.

• It is the slave’s fixed leg that synchronizes to this SYNC Slave Switch Node

(10 V/div)

signal.

• The slave should not turn on until it receives the first Time (2 µs/div)

SYNC signal.

• If the SYNC signal stops, the slave can shut down or

continue running at its own switching frequency,

depending on the system requirements.

Texas Instruments 2 ADJ 3Q 2018

Analog Design Journal Power

Current sharing The bigger the k, the more accurate the current sharing,

There are two popular current-sharing methods: active but the more deviation of output voltage versus load.

current sharing and passive-droop current sharing. Each Simultaneous startup

has its own pros and cons. In active current sharing, a

A power-converter startup sequence usually goes like this:

current-share bus connects the paralleled power convert-

ers. The signal on the share bus represents the average 1. Turn on VIN.

current of all modules; each power supply attempts to 2. The bias starts up and provides VCC to the controller.

adjust its output current in order to match its output 3. The controller initializes.

current with the average current. 4. The controller checks that VIN is correct and that

In this article, passive-droop current sharing is used as there are no other faults.

the example. There is no current-share bus required, so 5. The converter turns on.

droop current sharing is also called zero-wire current

sharing. Compared to active current sharing, passive- With the addition of interleaving function, the master

droop current sharing is a simple but reliable current- and slave converters have different firmware. This causes

sharing method. In this method, the power-supply the controllers to have different initialization times. Also,

circuitry measures its output current and adjusts its given the component tolerance of the two converters,

voltage either up or down. If the load current increases, even without the interleaving function, they won’t turn on

the voltage decreases linearly. simultaneously.

Figure 4 shows the characteristics of output-voltage Thus, a “handshaking” mechanism is required. A simple

versus output-current for two power converters. The extra way to achieve this is to use both the SYNC signal and the

voltage drop or “droop” is proportional to the load current. connection between a GPIO pin on both the master and

If one of the paralleled power converters tries to provide slave converters. The master does not send a SYNC signal

more current, its output will droop slightly, resulting in a until it has finished the initialization and is ready to turn

reduced current. The other converter will provide more on. Once the slave receives the SYNC signal and is ready

current to the load; thus, the power supplies will share the to turn on, it sends a “SLAVE_READY” signal back to the

output load between them. master and turns on. The master will turn on immediately

With digital-controller firmware, the implementation is once it receives this SLAVE_READY signal. This way,

easy. The firmware monitors its output current through an master and slave will turn on at the same time, as shown

analog-to-digital converter (ADC) and adjusts the voltage- in Figure 5. Now the SYNC signal is not only used as a

loop reference accordingly. Equation 1 shows how the synchronization signal but also as a handshaking signal.

voltage-loop reference is calculated: The GPIO and SYNC connections are the same as shown

in Figure 1.

Voltage-loop reference =

I Figure 5. Handshaking during startup

Nominal reference − k × IOUT - OUT_max (1)

2

where k is the slope of the curve in Figure 4. Power up

Equation 2 calculates k as:

Maximum allowed voltagedroop

( no load to full load )

k= (2) Master Initialization Slave Initialization

IOUT _ max

Figure 4. Characteristics of output-voltage Master ready

vs. output-current in droop-current sharing

Master starts

sending SYNC Slave detects SYNC

Hand

VOUT (V)

Slave ready

shaking

Nominal Voltage

Master receives Slave sends out

"SLAVE_READY" signal "SLAVE_READY" signal

0 50 100 Master turns on Slave turns on

IOUT (%)

Texas Instruments 3 ADJ 3Q 2018

Analog Design Journal Power

If the extra GPIO pin is not available, a delay in the Conclusion

master code can be added right before it starts sending High-power applications or N+1 redundant power systems

out the SYNC signal. The delay should be long enough to require two or more power converters running in parallel.

guarantee that when the slave receives the first SYNC The power supplies in a properly paralleled operating

signal, its initialization is complete and it is ready to turn system should start up simultaneously, be interleaved and

on. This way, the master does not need to wait for share the load current.

SLAVE_READY; it can turn on immediately after it starts This article presented an example of how to implement

sending the SYNC signal. The slave will turn on immedi- such functions in a digital controller that does not already

ately after it receives the first SYNC signal and both the have these capabilities built-in. Although two converters

master and slave will turn on at the same time. This were used in the example, the same concepts can be

method saves the extra GPIO pin, but at the cost of extra extended to three or more converters running in parallel.

startup delay time.

Related Web sites

Product information:

UCD3138

Texas Instruments 4 ADJ 3Q 2018

Analog Design Journal

TI Worldwide Technical Support

TI Support

Thank you for your business. Find the answer to your support need or get in

touch with our support center at

www.ti.com/support

China: http://www.ti.com.cn/guidedsupport/cn/docs/supporthome.tsp

Japan: http://www.tij.co.jp/guidedsupport/jp/docs/supporthome.tsp

Technical support forums

Search through millions of technical questions and answers at TI’s E2E™

Community (engineer-to-engineer) at

e2e.ti.com

China: http://www.deyisupport.com/

Japan: http://e2e.ti.com/group/jp/

TI Training

From technology fundamentals to advanced implementation, we offer

on-demand and live training to help bring your next-generation designs to life.

Get started now at

training.ti.com

China: http://www.ti.com.cn/general/cn/docs/gencontent.tsp?contentId=71968

Japan: https://training.ti.com/jp

Important Notice: The products and services of Texas Instruments Incorporated and its

subsidiaries described herein are sold subject to TI’s standard terms and conditions of sale.

Customers are advised to obtain the most current and complete information about TI products and

services before placing orders. TI assumes no liability for applications assistance, customer’s

applications or product designs, software performance, or infringement of patents. The publication

of information regarding any other company’s products or services does not constitute TI’s approval,

warranty or endorsement thereof.

A011617

E2E is a trademark of Texas Instruments. All

other trademarks are the property of their

respective owners.

© 2018 Texas Instruments Incorporated.

All rights reserved. SLYT748

Texas Instruments 5 ADJ 3Q 2018

IMPORTANT NOTICE FOR TI DESIGN INFORMATION AND RESOURCES

Texas Instruments Incorporated (‘TI”) technical, application or other design advice, services or information, including, but not limited to,

reference designs and materials relating to evaluation modules, (collectively, “TI Resources”) are intended to assist designers who are

developing applications that incorporate TI products; by downloading, accessing or using any particular TI Resource in any way, you

(individually or, if you are acting on behalf of a company, your company) agree to use it solely for this purpose and subject to the terms of

this Notice.

TI’s provision of TI Resources does not expand or otherwise alter TI’s applicable published warranties or warranty disclaimers for TI

products, and no additional obligations or liabilities arise from TI providing such TI Resources. TI reserves the right to make corrections,

enhancements, improvements and other changes to its TI Resources.

You understand and agree that you remain responsible for using your independent analysis, evaluation and judgment in designing your

applications and that you have full and exclusive responsibility to assure the safety of your applications and compliance of your applications

(and of all TI products used in or for your applications) with all applicable regulations, laws and other applicable requirements. You

represent that, with respect to your applications, you have all the necessary expertise to create and implement safeguards that (1)

anticipate dangerous consequences of failures, (2) monitor failures and their consequences, and (3) lessen the likelihood of failures that

might cause harm and take appropriate actions. You agree that prior to using or distributing any applications that include TI products, you

will thoroughly test such applications and the functionality of such TI products as used in such applications. TI has not conducted any

testing other than that specifically described in the published documentation for a particular TI Resource.

You are authorized to use, copy and modify any individual TI Resource only in connection with the development of applications that include

the TI product(s) identified in such TI Resource. NO OTHER LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE TO

ANY OTHER TI INTELLECTUAL PROPERTY RIGHT, AND NO LICENSE TO ANY TECHNOLOGY OR INTELLECTUAL PROPERTY

RIGHT OF TI OR ANY THIRD PARTY IS GRANTED HEREIN, including but not limited to any patent right, copyright, mask work right, or

other intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information

regarding or referencing third-party products or services does not constitute a license to use such products or services, or a warranty or

endorsement thereof. Use of TI Resources may require a license from a third party under the patents or other intellectual property of the

third party, or a license from TI under the patents or other intellectual property of TI.

TI RESOURCES ARE PROVIDED “AS IS” AND WITH ALL FAULTS. TI DISCLAIMS ALL OTHER WARRANTIES OR

REPRESENTATIONS, EXPRESS OR IMPLIED, REGARDING TI RESOURCES OR USE THEREOF, INCLUDING BUT NOT LIMITED TO

ACCURACY OR COMPLETENESS, TITLE, ANY EPIDEMIC FAILURE WARRANTY AND ANY IMPLIED WARRANTIES OF

MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF ANY THIRD PARTY INTELLECTUAL

PROPERTY RIGHTS.

TI SHALL NOT BE LIABLE FOR AND SHALL NOT DEFEND OR INDEMNIFY YOU AGAINST ANY CLAIM, INCLUDING BUT NOT

LIMITED TO ANY INFRINGEMENT CLAIM THAT RELATES TO OR IS BASED ON ANY COMBINATION OF PRODUCTS EVEN IF

DESCRIBED IN TI RESOURCES OR OTHERWISE. IN NO EVENT SHALL TI BE LIABLE FOR ANY ACTUAL, DIRECT, SPECIAL,

COLLATERAL, INDIRECT, PUNITIVE, INCIDENTAL, CONSEQUENTIAL OR EXEMPLARY DAMAGES IN CONNECTION WITH OR

ARISING OUT OF TI RESOURCES OR USE THEREOF, AND REGARDLESS OF WHETHER TI HAS BEEN ADVISED OF THE

POSSIBILITY OF SUCH DAMAGES.

You agree to fully indemnify TI and its representatives against any damages, costs, losses, and/or liabilities arising out of your non-

compliance with the terms and provisions of this Notice.

This Notice applies to TI Resources. Additional terms apply to the use and purchase of certain types of materials, TI products and services.

These include; without limitation, TI’s standard terms for semiconductor products http://www.ti.com/sc/docs/stdterms.htm), evaluation

modules, and samples (http://www.ti.com/sc/docs/sampterms.htm).

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2018, Texas Instruments Incorporated

You might also like

- Analog IC Design With Low-Dropout RegulatorsDocument373 pagesAnalog IC Design With Low-Dropout RegulatorsHoang le Huy67% (3)

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Project Report Speed Control of Induction MotorDocument47 pagesProject Report Speed Control of Induction Motorsrajaprojects0% (1)

- Exercise 4 Iron Tower Lighting ControlDocument6 pagesExercise 4 Iron Tower Lighting ControlJude Philip MaglasangNo ratings yet

- Simulation of Buck Boost ConverterDocument4 pagesSimulation of Buck Boost Converterganeshkurapati_15512No ratings yet

- Delomatic 3, SCM-1, Synchronising-Measuring Module 4921240056 UKDocument3 pagesDelomatic 3, SCM-1, Synchronising-Measuring Module 4921240056 UKВупсень ПупсеньNo ratings yet

- Uses DBX 146221Document8 pagesUses DBX 146221shirtquittersNo ratings yet

- Buie UpgradeDocument4 pagesBuie UpgradeNatasaBugaian100% (1)

- Direct Digital Synthesis Controlled Pure Sine Wave InverterDocument17 pagesDirect Digital Synthesis Controlled Pure Sine Wave InverterNabil MohammadNo ratings yet

- Design of Digital Controller For Switch Mode Power Supply: Presented by Santwana Kumari SO/CDocument25 pagesDesign of Digital Controller For Switch Mode Power Supply: Presented by Santwana Kumari SO/CShuaib Ahmad KhanNo ratings yet

- Sisngle Phase RectifierDocument5 pagesSisngle Phase RectifiermücahitNo ratings yet

- 500-kHz Half-Bridge DC-DC ConverterDocument17 pages500-kHz Half-Bridge DC-DC Converteratkxyz777100% (1)

- Zenith ZTG Transfer Switch: Spec SheetDocument15 pagesZenith ZTG Transfer Switch: Spec SheetDomenico SarcinaNo ratings yet

- Speed Control of DC Motor Using PDocument22 pagesSpeed Control of DC Motor Using PAnanth Sai YadavNo ratings yet

- Signal ProcessingDocument47 pagesSignal ProcessingAthira rcNo ratings yet

- AND8273/D Design of A 100 W Active Clamp Forward DC DC Converter For Telecom Systems Using The NCP1562Document20 pagesAND8273/D Design of A 100 W Active Clamp Forward DC DC Converter For Telecom Systems Using The NCP1562Elie IlokoNo ratings yet

- Dual Active BrdigeDocument20 pagesDual Active Brdigeayush sharmaNo ratings yet

- Multilevel InverterDocument74 pagesMultilevel InverterRaghu Selvaraj100% (4)

- Carrier Based Sinusodial PWM Scheme For The Nine Switch ConverterDocument6 pagesCarrier Based Sinusodial PWM Scheme For The Nine Switch ConverterShankar MukalNo ratings yet

- Digital Power-Conversion For The Analog EngineerDocument12 pagesDigital Power-Conversion For The Analog EngineerfjwoemcuNo ratings yet

- MPPT - Maximum Power Point TrackingDocument9 pagesMPPT - Maximum Power Point TrackingSanjeev ReddyNo ratings yet

- A Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterDocument6 pagesA Implementation of Single-Switch Nonisolated Transformerless Buck-Boost DC-DC ConverterKPCYP COHODNo ratings yet

- MAX9979Document60 pagesMAX9979justcatchmenowNo ratings yet

- LNK605 DatasheetDocument18 pagesLNK605 DatasheetdgujarathiNo ratings yet

- Closed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLABDocument9 pagesClosed Loop Buck & Boost Converter Mathematical Modeling, Analysis and Simulation Using MATLAB7031 GauravNo ratings yet

- Transformer protection systemDocument57 pagesTransformer protection systemAnkit RajNo ratings yet

- Slyt 718Document5 pagesSlyt 718wartchev39No ratings yet

- MegaMoto Plus Motor Control Shield For ArduinoDocument13 pagesMegaMoto Plus Motor Control Shield For ArduinosiogNo ratings yet

- An Open-Loop Stepper Motor Driver Based On FPGADocument5 pagesAn Open-Loop Stepper Motor Driver Based On FPGADivya JamesNo ratings yet

- Controller Design For Buck Converter Step-by-Step Approach: Swapna ManurkarDocument3 pagesController Design For Buck Converter Step-by-Step Approach: Swapna ManurkarJessica RossNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Gate Driver Circuit For Three Phase InverterDocument13 pagesGate Driver Circuit For Three Phase InverterMarc TcheukabaNo ratings yet

- EI5007W2Document17 pagesEI5007W2PyiAungNo ratings yet

- LM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsDocument10 pagesLM25005, LM25010: Buck Regulator Topologies For Wide Input/Output Voltage DifferentialsBejoy ThomasNo ratings yet

- Chapter No.:-01 Introuuction: Pulse-Width Modulation (PWM), Modulation (PDM)Document63 pagesChapter No.:-01 Introuuction: Pulse-Width Modulation (PWM), Modulation (PDM)Pooja BanNo ratings yet

- Adc 0808Document6 pagesAdc 0808GokulThalaNo ratings yet

- Design and Implementation of Parallel Connected DC-DC Buck ConvertersDocument6 pagesDesign and Implementation of Parallel Connected DC-DC Buck ConvertersColzi ChenNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Arduino Driving Power Mosfet uRiZsEVG6kDocument11 pagesArduino Driving Power Mosfet uRiZsEVG6kahas viyanaNo ratings yet

- University of Engineering & Technology LahoreDocument43 pagesUniversity of Engineering & Technology LahoreKantesh KumarNo ratings yet

- Analog To Digital ConvertDocument20 pagesAnalog To Digital ConvertluxiaofengNo ratings yet

- ADIC ExperimentsDocument41 pagesADIC ExperimentsTushar PatilNo ratings yet

- Chapter One Controlling The Operation of Wind-Solar Hybrid Power System Using Arduino-Based Hybrid MPPT ControllerDocument48 pagesChapter One Controlling The Operation of Wind-Solar Hybrid Power System Using Arduino-Based Hybrid MPPT ControllerOdebunmi NathanielNo ratings yet

- Training Curriculum: TIA Portal Module 009Document27 pagesTraining Curriculum: TIA Portal Module 009Hải Nguyễn KhắcNo ratings yet

- VE Transfer Switch-Pdf-EnDocument9 pagesVE Transfer Switch-Pdf-EnAnte MilanovićNo ratings yet

- 1999apr08 Icd PD Tac2Document11 pages1999apr08 Icd PD Tac2King GervinhoNo ratings yet

- LSC Presentation: Topic:-Dual Slope A/D ConvertorDocument8 pagesLSC Presentation: Topic:-Dual Slope A/D ConvertorSatyakam JhaNo ratings yet

- Diy Boost CalcDocument6 pagesDiy Boost Calckutu32No ratings yet

- Design Report Pss20Document46 pagesDesign Report Pss20Jaciel LMNo ratings yet

- A Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDDocument9 pagesA Closed Loop Control of Buck Boost Ac Ac Converter With Reduced THDAndrés ToroNo ratings yet

- Microchip CLC DescriptionDocument12 pagesMicrochip CLC DescriptionKamlesh YadavNo ratings yet

- Unit 2 - NewDocument61 pagesUnit 2 - NewMonster AmanNo ratings yet

- ELC Brosure Eng 08Document10 pagesELC Brosure Eng 08RunhydroNo ratings yet

- Dem 60 CDocument3 pagesDem 60 Cmohannad87No ratings yet

- AMPS - 2x - 2M2.3BWD3 3L V850 MV34.5Document38 pagesAMPS - 2x - 2M2.3BWD3 3L V850 MV34.5Josue Crespo GonzalezNo ratings yet

- Synchronization PanelDocument31 pagesSynchronization PanelHariom ChaurasiyaNo ratings yet

- 004 Pwm-OcxiDocument7 pages004 Pwm-OcxiNeodymeNo ratings yet

- Power Factor Correction AC-DC ConverterDocument5 pagesPower Factor Correction AC-DC Convertermatadamahesh1No ratings yet

- ABSTRACT: The Transformer Is A Static Device, Which ConvertsDocument15 pagesABSTRACT: The Transformer Is A Static Device, Which Convertsindhu kaviNo ratings yet

- PW2 MCDDocument5 pagesPW2 MCDUlul AzmiNo ratings yet

- Automatic Static Transfer SwitchDocument2 pagesAutomatic Static Transfer Switchanoop13No ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Ruso 6Document1 pageRuso 6Oscar SuarezNo ratings yet

- Ruso 2Document1 pageRuso 2Oscar SuarezNo ratings yet

- Ruso 4Document1 pageRuso 4Oscar SuarezNo ratings yet

- Ruso 3Document1 pageRuso 3Oscar SuarezNo ratings yet

- UNDP PV BookletDocument20 pagesUNDP PV BookletZeina RammalNo ratings yet

- ARM-A Mandatory PrimerDocument4 pagesARM-A Mandatory PrimervigneshwaranjNo ratings yet

- Vista RG750-V2 - Englisch ManualDocument9 pagesVista RG750-V2 - Englisch Manualsorsricerche100% (1)

- Micro ControllerDocument41 pagesMicro ControllerSaravana RajaNo ratings yet

- Ade NotesDocument128 pagesAde NotesKiranmai KonduruNo ratings yet

- FM 24-11 Tactical Satellite CommunicationsDocument90 pagesFM 24-11 Tactical Satellite CommunicationsMark CheneyNo ratings yet

- Operating Instructions Specification Hiperface Motor Feedback Protocol Neutral IM0064865Document79 pagesOperating Instructions Specification Hiperface Motor Feedback Protocol Neutral IM0064865Mohammad MorassaeiNo ratings yet

- Chemistry Project For Class 12 Topic: Saturated Solution: Measuring SolubilityDocument13 pagesChemistry Project For Class 12 Topic: Saturated Solution: Measuring SolubilityNishith Naik100% (1)

- 06 639Document28 pages06 639erve17No ratings yet

- Fender Am Pro Stratocaster HSS Manual y PartesDocument7 pagesFender Am Pro Stratocaster HSS Manual y PartesMario Orlando NerioNo ratings yet

- Relay MY2NDocument16 pagesRelay MY2NSofyan AndikaNo ratings yet

- JNTUK Computer Organization Nov 2015 Question PaperDocument4 pagesJNTUK Computer Organization Nov 2015 Question PaperTSRKNo ratings yet

- Dist RelayDocument6 pagesDist RelaymakroumNo ratings yet

- Chap04 (12 21 06) PDFDocument66 pagesChap04 (12 21 06) PDFHassan FarssiNo ratings yet

- MainDocument2,929 pagesMainanon_172022236No ratings yet

- 5200236-00A - Salwico AC-IR-3Fq - Addressable-Conventional IR Flame DetectorDocument4 pages5200236-00A - Salwico AC-IR-3Fq - Addressable-Conventional IR Flame DetectorcembozNo ratings yet

- Power Semiconductors and Power Supplies PDFDocument132 pagesPower Semiconductors and Power Supplies PDFtranhuutuongNo ratings yet

- Chinna Resume1Document3 pagesChinna Resume1saisurenNo ratings yet

- Unidirectional LED Based Solar Light (TorchDocument6 pagesUnidirectional LED Based Solar Light (TorchDeepak PrmNo ratings yet

- Name: Vinit J Faria Roll No. 157 STD: S.Y.J.C. (Science) Div: II Elphinstone CollegeDocument9 pagesName: Vinit J Faria Roll No. 157 STD: S.Y.J.C. (Science) Div: II Elphinstone CollegeNikit FariaNo ratings yet

- ALIA Manual AVF7000Document26 pagesALIA Manual AVF7000Abid HameedNo ratings yet

- Service Manual: VCR 5300 VCR 4300 VCR 2300Document110 pagesService Manual: VCR 5300 VCR 4300 VCR 2300wid9981No ratings yet

- Atmega168pa Au AtmelDocument419 pagesAtmega168pa Au AtmelDeibis Francisco Paredes HurtadoNo ratings yet

- Nx301a 1Document2 pagesNx301a 1AhmadAfiqNo ratings yet

- KX-FP207FX-S KX-FP218FX-S: Compact Plain Paper Fax (With Digital Answering System)Document232 pagesKX-FP207FX-S KX-FP218FX-S: Compact Plain Paper Fax (With Digital Answering System)ValeriiNo ratings yet

- What Is A Lecher AntennaDocument4 pagesWhat Is A Lecher AntennaPt AkaashNo ratings yet

- PAW3805EK-CJV2 Brief-V1.3 27062017Document1 pagePAW3805EK-CJV2 Brief-V1.3 27062017rreglosNo ratings yet