Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

1 viewsC8051F38x-pages-53

C8051F38x-pages-53

Uploaded by

lingeshtjCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- Adc Pic18f452Document8 pagesAdc Pic18f452Muhammad Ummair100% (1)

- Lab 7 ADCDocument19 pagesLab 7 ADCakkauntdlyaigrichegotoescheNo ratings yet

- C8051F38x-pages-57Document1 pageC8051F38x-pages-57lingeshtjNo ratings yet

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- Conversor A-D PIC16F877ADocument7 pagesConversor A-D PIC16F877AEsdras BonifacioNo ratings yet

- ADC Datasheet 16F877A ExtraitDocument7 pagesADC Datasheet 16F877A Extraitsaida.chelhiNo ratings yet

- C8051F38x-pages-54Document1 pageC8051F38x-pages-54lingeshtjNo ratings yet

- G12864C LCD Module ManualDocument13 pagesG12864C LCD Module Manualsigit jokoNo ratings yet

- LPC 17xx ADC: Done byDocument13 pagesLPC 17xx ADC: Done byabu taherNo ratings yet

- LPC2148 ADC ProgrammingDocument8 pagesLPC2148 ADC Programmingkhushi63No ratings yet

- Exploreembedded Com PDFDocument7 pagesExploreembedded Com PDFGonzalo ViñamaguaNo ratings yet

- ADC TutorialDocument12 pagesADC TutorialSathiya NathanNo ratings yet

- T19 AdcDocument11 pagesT19 AdcReyes Benitez LuisNo ratings yet

- Lec 7c ProgrammingIODocument7 pagesLec 7c ProgrammingIOAnonymous zN7CjfgnENo ratings yet

- ATtiny Examples For ProgramingDocument10 pagesATtiny Examples For ProgramingLeo MilosevNo ratings yet

- ADC Measurement DetailDocument9 pagesADC Measurement DetailMuhammad SiddiqueNo ratings yet

- Lecture12-Using PIC Micro Controller 16F877ADocument57 pagesLecture12-Using PIC Micro Controller 16F877ADoodee Mohammed100% (4)

- CED19I032Document20 pagesCED19I032Pranavram VNo ratings yet

- Embedded System Design - DisplaysDocument32 pagesEmbedded System Design - DisplaysAnanthNo ratings yet

- Embedded SystemDocument15 pagesEmbedded Systembrahma2deen2chaudharNo ratings yet

- Embedded SystemDocument15 pagesEmbedded Systembrahma2deen2chaudharNo ratings yet

- Microcontroller BasicsDocument14 pagesMicrocontroller BasicsholaNo ratings yet

- United International University: EEE 424: Microprocessor and Interfacing Laboratory Experiment#5Document7 pagesUnited International University: EEE 424: Microprocessor and Interfacing Laboratory Experiment#5Nura Alam ProtikNo ratings yet

- The ADC of The AVR: Analog To Digital ConversionDocument25 pagesThe ADC of The AVR: Analog To Digital ConversionZauhari EffendiNo ratings yet

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- Lab 09 - MESDocument8 pagesLab 09 - MESMuhammad Sarmad BaigNo ratings yet

- PIC18f452: Course: ContactDocument13 pagesPIC18f452: Course: ContactMalik Adil FarooqNo ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- LCD 128x64 Tech12864GDocument10 pagesLCD 128x64 Tech12864GMarlon PerinNo ratings yet

- Graphic Display AGM-12864A-801Document15 pagesGraphic Display AGM-12864A-801Anonymous nMZN9dJvaZNo ratings yet

- 89c51 Raining Cou Week1Document33 pages89c51 Raining Cou Week1api-3761333No ratings yet

- ADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERDocument17 pagesADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERTechreinnovate0% (1)

- Peripheral Interfacing Unit Iii: Mr. S. Vinod Lecturer Eee DepartmentDocument123 pagesPeripheral Interfacing Unit Iii: Mr. S. Vinod Lecturer Eee DepartmentVinod SrinivasanNo ratings yet

- LCM12864B: LCD Module User ManualDocument11 pagesLCM12864B: LCD Module User ManualDenes MarschalkoNo ratings yet

- AVRDocument20 pagesAVRAhsan KhanNo ratings yet

- Interfacing With Adc and DacDocument6 pagesInterfacing With Adc and Dacvennila GNo ratings yet

- Solution: Analog To Digital ConverterDocument11 pagesSolution: Analog To Digital ConverterAll OneNo ratings yet

- 14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140Document3 pages14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140asdasdasfli.elkinNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- 21 Adc2Document9 pages21 Adc2vishnuksNo ratings yet

- Addis Ababa UniversityDocument8 pagesAddis Ababa UniversityEZRA MOHAMMEDNo ratings yet

- ADC Interfacing With MicrocontrollersDocument9 pagesADC Interfacing With MicrocontrollersLuis MezaNo ratings yet

- 2 AdcDocument13 pages2 AdcM.i. RehmanNo ratings yet

- Datasheet LCD 128x64 ATM12864DDocument21 pagesDatasheet LCD 128x64 ATM12864DRafael MendozaNo ratings yet

- A) Discuss About The Coding Instruction of ADC With Necessary Registers, Bits and Bit Pattern TablesDocument11 pagesA) Discuss About The Coding Instruction of ADC With Necessary Registers, Bits and Bit Pattern TablesAll OneNo ratings yet

- Iotuni 22Document24 pagesIotuni 22Ashwin BenkeNo ratings yet

- 8051 CH8Document42 pages8051 CH8Usama JavedNo ratings yet

- WR - DC3001 - E01 - 1 ZXWR RNS Dimensioning 57Document57 pagesWR - DC3001 - E01 - 1 ZXWR RNS Dimensioning 57noumizredhaNo ratings yet

- MSP432 Chapter4 UARTDocument25 pagesMSP432 Chapter4 UARTSukkesh SNo ratings yet

- Analog-to-Digital ConverterDocument21 pagesAnalog-to-Digital ConverterThành TrườngNo ratings yet

- AVR ATMEGA16/32: Your Best Friend in Autonomous Robotics !!!Document25 pagesAVR ATMEGA16/32: Your Best Friend in Autonomous Robotics !!!sidraiz26No ratings yet

- ZXWR RNC Dimensioning Principle-KPNGBDocument52 pagesZXWR RNC Dimensioning Principle-KPNGBfatehmeNo ratings yet

- ADC of PIC MicrocontrollerDocument4 pagesADC of PIC Microcontrollerkillbill100% (2)

- Example of Power Supply: Normal Temperature Type Extended Temperature TypeDocument1 pageExample of Power Supply: Normal Temperature Type Extended Temperature Typerdc02271No ratings yet

- Implementing An Analog-to-Digital Converter On The Texas Instruments MSP430 MicrocontrollerDocument8 pagesImplementing An Analog-to-Digital Converter On The Texas Instruments MSP430 MicrocontrollerAdnan khan khanNo ratings yet

- Adc 0804Document41 pagesAdc 0804AndySilvandNo ratings yet

- ADC in AVR ATmega16Document7 pagesADC in AVR ATmega16Gaurav Shinde100% (1)

- Adm1602k Nsa Fbs 3.3vDocument22 pagesAdm1602k Nsa Fbs 3.3vHer ManTokNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- C8051F38x-pages-62Document1 pageC8051F38x-pages-62lingeshtjNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- C8051F38x-pages-35Document1 pageC8051F38x-pages-35lingeshtjNo ratings yet

- C8051F38x-pages-37Document1 pageC8051F38x-pages-37lingeshtjNo ratings yet

- C8051F38x-pages-30Document1 pageC8051F38x-pages-30lingeshtjNo ratings yet

- C8051F38x-pages-12Document1 pageC8051F38x-pages-12lingeshtjNo ratings yet

- C8051F38x-pages-23Document1 pageC8051F38x-pages-23lingeshtjNo ratings yet

- doc0180-pages-25Document1 pagedoc0180-pages-25lingeshtjNo ratings yet

- doc0180-pages-23Document1 pagedoc0180-pages-23lingeshtjNo ratings yet

- doc0180-pages-2Document1 pagedoc0180-pages-2lingeshtjNo ratings yet

- Linux Kernel SlidesDocument473 pagesLinux Kernel SlideslingeshtjNo ratings yet

- CommonAPICppAMMSeoul (1)-pages-18Document1 pageCommonAPICppAMMSeoul (1)-pages-18lingeshtjNo ratings yet

- doc0180-pages-16Document1 pagedoc0180-pages-16lingeshtjNo ratings yet

C8051F38x-pages-53

C8051F38x-pages-53

Uploaded by

lingeshtj0 ratings0% found this document useful (0 votes)

1 views1 pageCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

1 views1 pageC8051F38x-pages-53

C8051F38x-pages-53

Uploaded by

lingeshtjCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 1

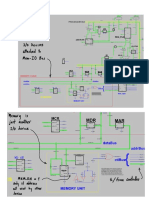

C8051F380/1/2/3/4/5/6/7/C

SFR Definition 6.1. ADC0CF: ADC0 Configuration

Bit 7 6 5 4 3 2 1 0

Name AD0SC[4:0] AD0LJST Reserved

Type R/W R/W R/W

Reset 1 1 1 1 1 0 0 0

SFR Address = 0xBC; SFR Page = All Pages

Bit Name Function

7:3 AD0SC[4:0] ADC0 SAR Conversion Clock Period Bits.

SAR Conversion clock is derived from system clock by the following equation, where

AD0SC refers to the 5-bit value held in bits AD0SC4–0. SAR Conversion clock

requirements are given in the ADC specification table.

SYSCLK

AD0SC = ------------------------ – 1

CLK SAR

Note: If the Memory Power Controller is enabled (MPCE = '1'), AD0SC must be set to at least

"00001" for proper ADC operation.

2 AD0LJST ADC0 Left Justify Select.

0: Data in ADC0H:ADC0L registers are right-justified.

1: Data in ADC0H:ADC0L registers are left-justified.

Note: The AD0LJST bit is only valid for 10-bit mode (AD08BE = 0).

1:0 Reserved Must Write 00b.

57 Rev. 1.5

You might also like

- Adc Pic18f452Document8 pagesAdc Pic18f452Muhammad Ummair100% (1)

- Lab 7 ADCDocument19 pagesLab 7 ADCakkauntdlyaigrichegotoescheNo ratings yet

- C8051F38x-pages-57Document1 pageC8051F38x-pages-57lingeshtjNo ratings yet

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- Conversor A-D PIC16F877ADocument7 pagesConversor A-D PIC16F877AEsdras BonifacioNo ratings yet

- ADC Datasheet 16F877A ExtraitDocument7 pagesADC Datasheet 16F877A Extraitsaida.chelhiNo ratings yet

- C8051F38x-pages-54Document1 pageC8051F38x-pages-54lingeshtjNo ratings yet

- G12864C LCD Module ManualDocument13 pagesG12864C LCD Module Manualsigit jokoNo ratings yet

- LPC 17xx ADC: Done byDocument13 pagesLPC 17xx ADC: Done byabu taherNo ratings yet

- LPC2148 ADC ProgrammingDocument8 pagesLPC2148 ADC Programmingkhushi63No ratings yet

- Exploreembedded Com PDFDocument7 pagesExploreembedded Com PDFGonzalo ViñamaguaNo ratings yet

- ADC TutorialDocument12 pagesADC TutorialSathiya NathanNo ratings yet

- T19 AdcDocument11 pagesT19 AdcReyes Benitez LuisNo ratings yet

- Lec 7c ProgrammingIODocument7 pagesLec 7c ProgrammingIOAnonymous zN7CjfgnENo ratings yet

- ATtiny Examples For ProgramingDocument10 pagesATtiny Examples For ProgramingLeo MilosevNo ratings yet

- ADC Measurement DetailDocument9 pagesADC Measurement DetailMuhammad SiddiqueNo ratings yet

- Lecture12-Using PIC Micro Controller 16F877ADocument57 pagesLecture12-Using PIC Micro Controller 16F877ADoodee Mohammed100% (4)

- CED19I032Document20 pagesCED19I032Pranavram VNo ratings yet

- Embedded System Design - DisplaysDocument32 pagesEmbedded System Design - DisplaysAnanthNo ratings yet

- Embedded SystemDocument15 pagesEmbedded Systembrahma2deen2chaudharNo ratings yet

- Embedded SystemDocument15 pagesEmbedded Systembrahma2deen2chaudharNo ratings yet

- Microcontroller BasicsDocument14 pagesMicrocontroller BasicsholaNo ratings yet

- United International University: EEE 424: Microprocessor and Interfacing Laboratory Experiment#5Document7 pagesUnited International University: EEE 424: Microprocessor and Interfacing Laboratory Experiment#5Nura Alam ProtikNo ratings yet

- The ADC of The AVR: Analog To Digital ConversionDocument25 pagesThe ADC of The AVR: Analog To Digital ConversionZauhari EffendiNo ratings yet

- Pic 16 F 628Document20 pagesPic 16 F 628Merényi Oszkár100% (1)

- Lab 09 - MESDocument8 pagesLab 09 - MESMuhammad Sarmad BaigNo ratings yet

- PIC18f452: Course: ContactDocument13 pagesPIC18f452: Course: ContactMalik Adil FarooqNo ratings yet

- F 818Document9 pagesF 818Eric YangNo ratings yet

- LCD 128x64 Tech12864GDocument10 pagesLCD 128x64 Tech12864GMarlon PerinNo ratings yet

- Graphic Display AGM-12864A-801Document15 pagesGraphic Display AGM-12864A-801Anonymous nMZN9dJvaZNo ratings yet

- 89c51 Raining Cou Week1Document33 pages89c51 Raining Cou Week1api-3761333No ratings yet

- ADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERDocument17 pagesADC, DAC and SENSOR INTERFACING IN AVR MICROCONTROLLERTechreinnovate0% (1)

- Peripheral Interfacing Unit Iii: Mr. S. Vinod Lecturer Eee DepartmentDocument123 pagesPeripheral Interfacing Unit Iii: Mr. S. Vinod Lecturer Eee DepartmentVinod SrinivasanNo ratings yet

- LCM12864B: LCD Module User ManualDocument11 pagesLCM12864B: LCD Module User ManualDenes MarschalkoNo ratings yet

- AVRDocument20 pagesAVRAhsan KhanNo ratings yet

- Interfacing With Adc and DacDocument6 pagesInterfacing With Adc and Dacvennila GNo ratings yet

- Solution: Analog To Digital ConverterDocument11 pagesSolution: Analog To Digital ConverterAll OneNo ratings yet

- 14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140Document3 pages14.4. Register Description: 14.4.1. I2C - M - 0 - CONTROL - REG 0x2140asdasdasfli.elkinNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- 21 Adc2Document9 pages21 Adc2vishnuksNo ratings yet

- Addis Ababa UniversityDocument8 pagesAddis Ababa UniversityEZRA MOHAMMEDNo ratings yet

- ADC Interfacing With MicrocontrollersDocument9 pagesADC Interfacing With MicrocontrollersLuis MezaNo ratings yet

- 2 AdcDocument13 pages2 AdcM.i. RehmanNo ratings yet

- Datasheet LCD 128x64 ATM12864DDocument21 pagesDatasheet LCD 128x64 ATM12864DRafael MendozaNo ratings yet

- A) Discuss About The Coding Instruction of ADC With Necessary Registers, Bits and Bit Pattern TablesDocument11 pagesA) Discuss About The Coding Instruction of ADC With Necessary Registers, Bits and Bit Pattern TablesAll OneNo ratings yet

- Iotuni 22Document24 pagesIotuni 22Ashwin BenkeNo ratings yet

- 8051 CH8Document42 pages8051 CH8Usama JavedNo ratings yet

- WR - DC3001 - E01 - 1 ZXWR RNS Dimensioning 57Document57 pagesWR - DC3001 - E01 - 1 ZXWR RNS Dimensioning 57noumizredhaNo ratings yet

- MSP432 Chapter4 UARTDocument25 pagesMSP432 Chapter4 UARTSukkesh SNo ratings yet

- Analog-to-Digital ConverterDocument21 pagesAnalog-to-Digital ConverterThành TrườngNo ratings yet

- AVR ATMEGA16/32: Your Best Friend in Autonomous Robotics !!!Document25 pagesAVR ATMEGA16/32: Your Best Friend in Autonomous Robotics !!!sidraiz26No ratings yet

- ZXWR RNC Dimensioning Principle-KPNGBDocument52 pagesZXWR RNC Dimensioning Principle-KPNGBfatehmeNo ratings yet

- ADC of PIC MicrocontrollerDocument4 pagesADC of PIC Microcontrollerkillbill100% (2)

- Example of Power Supply: Normal Temperature Type Extended Temperature TypeDocument1 pageExample of Power Supply: Normal Temperature Type Extended Temperature Typerdc02271No ratings yet

- Implementing An Analog-to-Digital Converter On The Texas Instruments MSP430 MicrocontrollerDocument8 pagesImplementing An Analog-to-Digital Converter On The Texas Instruments MSP430 MicrocontrollerAdnan khan khanNo ratings yet

- Adc 0804Document41 pagesAdc 0804AndySilvandNo ratings yet

- ADC in AVR ATmega16Document7 pagesADC in AVR ATmega16Gaurav Shinde100% (1)

- Adm1602k Nsa Fbs 3.3vDocument22 pagesAdm1602k Nsa Fbs 3.3vHer ManTokNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- C8051F38x-pages-62Document1 pageC8051F38x-pages-62lingeshtjNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- C8051F38x-pages-35Document1 pageC8051F38x-pages-35lingeshtjNo ratings yet

- C8051F38x-pages-37Document1 pageC8051F38x-pages-37lingeshtjNo ratings yet

- C8051F38x-pages-30Document1 pageC8051F38x-pages-30lingeshtjNo ratings yet

- C8051F38x-pages-12Document1 pageC8051F38x-pages-12lingeshtjNo ratings yet

- C8051F38x-pages-23Document1 pageC8051F38x-pages-23lingeshtjNo ratings yet

- doc0180-pages-25Document1 pagedoc0180-pages-25lingeshtjNo ratings yet

- doc0180-pages-23Document1 pagedoc0180-pages-23lingeshtjNo ratings yet

- doc0180-pages-2Document1 pagedoc0180-pages-2lingeshtjNo ratings yet

- Linux Kernel SlidesDocument473 pagesLinux Kernel SlideslingeshtjNo ratings yet

- CommonAPICppAMMSeoul (1)-pages-18Document1 pageCommonAPICppAMMSeoul (1)-pages-18lingeshtjNo ratings yet

- doc0180-pages-16Document1 pagedoc0180-pages-16lingeshtjNo ratings yet