Professional Documents

Culture Documents

Cpu-cfc

Cpu-cfc

Uploaded by

istiakeislam7Copyright:

Available Formats

You might also like

- JBW1 - Rev2 PDFDocument1 pageJBW1 - Rev2 PDFSreekanthMylavarapuNo ratings yet

- Compal NM-A271 ACLU1&ACLU2 - G40-70 & G50-70 - REV 1.0 - Lenovo IdeaPad G40-70, G50-70 PDFDocument59 pagesCompal NM-A271 ACLU1&ACLU2 - G40-70 & G50-70 - REV 1.0 - Lenovo IdeaPad G40-70, G50-70 PDFDaniel NegutNo ratings yet

- Tesla RCM DiagramDocument4 pagesTesla RCM DiagrampeefincaNo ratings yet

- Cross Reference: K0402 M03 M M M2 M3 MDocument4 pagesCross Reference: K0402 M03 M M M2 M3 Mkatie farrellNo ratings yet

- Bluetooth 2 Click Schematic v102Document1 pageBluetooth 2 Click Schematic v102Ammar AlkindyNo ratings yet

- Astm A488Document1 pageAstm A488Mohamed FaragNo ratings yet

- IBM Thinkpad Z61 (Quanta BW2)Document80 pagesIBM Thinkpad Z61 (Quanta BW2)Maks ProstNo ratings yet

- Description of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QDocument1 pageDescription of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QTuấn Lê QuangNo ratings yet

- Check Flight Availability - Cathay Pacific CargoDocument1 pageCheck Flight Availability - Cathay Pacific CargoAde NugrahaNo ratings yet

- A351 Service ManualDocument15 pagesA351 Service ManualDark FoxNo ratings yet

- 610c rm-836 SchematicDocument42 pages610c rm-836 SchematicVladimir GutarraNo ratings yet

- 303 14 PDFDocument38 pages303 14 PDFTuan TranNo ratings yet

- DIY TP4056 Charger CircuitDocument1 pageDIY TP4056 Charger Circuitv3642093No ratings yet

- MaterialDocument2 pagesMaterialdurgeshwardNo ratings yet

- G700-T00 Circuit DiagramDocument28 pagesG700-T00 Circuit DiagramRiza Virsada0% (1)

- MT6572 SchematicDocument19 pagesMT6572 SchematicdomisoftNo ratings yet

- weatherSTAMP - UnknownDocument1 pageweatherSTAMP - UnknownJony DarkoNo ratings yet

- 1 Componente Plantate: Rohde & Schwarz TopexDocument8 pages1 Componente Plantate: Rohde & Schwarz TopexCristian DobreNo ratings yet

- Iprog Mainboard SCHDocument1 pageIprog Mainboard SCHnelson lince100% (1)

- SM Bus Block DiagramDocument1 pageSM Bus Block Diagramradu2000vNo ratings yet

- 05a-BSSOM - S13 - BSC ARCHITECTURE AND FUNCTIONS - 6-65894 - v6Document46 pages05a-BSSOM - S13 - BSC ARCHITECTURE AND FUNCTIONS - 6-65894 - v6azzou dino32No ratings yet

- Moog SpringDocument18 pagesMoog SpringRicardo Rangel PosadasNo ratings yet

- TC-P42XT50L: 42 Inch Class 720p Plasma HDTVDocument12 pagesTC-P42XT50L: 42 Inch Class 720p Plasma HDTVELECTRONICA J Y CENTRO ELECTRONICONo ratings yet

- G610 U00Document36 pagesG610 U00Mauriciø Ruiz100% (1)

- Kim Uno Rev1 SchematicDocument1 pageKim Uno Rev1 SchematicweaponNo ratings yet

- 1.SCH List: RF BB SchematicsDocument36 pages1.SCH List: RF BB SchematicsLuis RodriguezNo ratings yet

- AC6925ADatasheetV1 0Document12 pagesAC6925ADatasheetV1 0АлексNo ratings yet

- A245 04pa Schematics - Dec. 1992 PDFDocument16 pagesA245 04pa Schematics - Dec. 1992 PDFtrung vothaiNo ratings yet

- More Smoky Amp Rev.ADocument3 pagesMore Smoky Amp Rev.AGryf Audio CompanyNo ratings yet

- SchematicDocument1 pageSchematicHue TruongNo ratings yet

- NSM D4u CTG3832 1711173022Document4 pagesNSM D4u CTG3832 1711173022kamalshak050No ratings yet

- 59Document79 pages59jroyal692974No ratings yet

- 4X SCHDocument70 pages4X SCHCs FixNo ratings yet

- Oz8380aln B4 0 TRDocument1 pageOz8380aln B4 0 TRAnacleto ChitalakumbiNo ratings yet

- Megasquirtavr v2.2 SCH PDFDocument6 pagesMegasquirtavr v2.2 SCH PDFgiapy0000No ratings yet

- DesafioDocument1 pageDesafioWilliam Anderson FernandesNo ratings yet

- Empty 100-Pin TQFP PT MCU CARD 1Document5 pagesEmpty 100-Pin TQFP PT MCU CARD 1Marian VladianuNo ratings yet

- lpc1114 SynthDocument1 pagelpc1114 SynthMirel-Cătălin ChirilăNo ratings yet

- Oz8153ln D 0 TRDocument1 pageOz8153ln D 0 TRЖељко Гелић0% (1)

- Ford Figo b517 2010 25 Ewd10Document1 pageFord Figo b517 2010 25 Ewd10sandeepNo ratings yet

- QM - Xc7A35T - Ddr3 Core Board: User ManualDocument13 pagesQM - Xc7A35T - Ddr3 Core Board: User ManualNgoc AnhNo ratings yet

- Walkie Talkie GERBERDocument1 pageWalkie Talkie GERBERAbhishek TiwariNo ratings yet

- Specifications: PartsDocument1 pageSpecifications: PartsFabio Da Silva Assunçao AssunçaoNo ratings yet

- CXD2861ERDocument30 pagesCXD2861ERZaegorNo ratings yet

- MT6351VDocument1 pageMT6351Vant franzzyNo ratings yet

- MB39A128ADocument1 pageMB39A128AY. Leonel MolinaNo ratings yet

- 16 FebDocument2 pages16 Febemma sofiaNo ratings yet

- Maintenance Guide CA-01,02Document12 pagesMaintenance Guide CA-01,02Wolaé Mathurin Edmond AmegandjinNo ratings yet

- ATIC71B1Document1 pageATIC71B1budi nugrohoNo ratings yet

- GPS EspDocument5 pagesGPS Espjak broseNo ratings yet

- Pivar103 Pivar103: Pilm56701 Pilm56708 Pilm56701 Pilm56708Document1 pagePivar103 Pivar103: Pilm56701 Pilm56708 Pilm56701 Pilm56708Hiroshi KoikeNo ratings yet

- CM508Document1 pageCM508MarshdeLangeNo ratings yet

- PRACTICAL TESTDocument4 pagesPRACTICAL TESTFaris IzzatNo ratings yet

- Datasheet MB86C311BDocument23 pagesDatasheet MB86C311BFelipe ShaderNo ratings yet

- Faroe Dis x32 MB MV (18742-1 0gg02) PDFDocument69 pagesFaroe Dis x32 MB MV (18742-1 0gg02) PDFRosa María AmoneNo ratings yet

- NCP81206MNTXGDocument1 pageNCP81206MNTXGElla Wijaya ChandraNo ratings yet

- NCP81205Document1 pageNCP81205Tom TomNo ratings yet

- OpenVox IX210 Asterisk IP PBX DatasheetDocument2 pagesOpenVox IX210 Asterisk IP PBX Datasheetmaple4VOIPNo ratings yet

- User Guide: Lenovo Thinkbook 14 Gen 3 and Lenovo Thinkbook 15 Gen 3Document34 pagesUser Guide: Lenovo Thinkbook 14 Gen 3 and Lenovo Thinkbook 15 Gen 3Abdul Hady Abu BakarNo ratings yet

- Xilinx Xc7k160t-2ffg676i Fpga PriceDocument6 pagesXilinx Xc7k160t-2ffg676i Fpga PricejackNo ratings yet

- Poweredge R730 and R730Xd: Technical GuideDocument64 pagesPoweredge R730 and R730Xd: Technical Guideender40No ratings yet

- Compal NM-A273 ACLUA, ACLUB REV 0.3 (1.0) - Lenovo Z50-70Document59 pagesCompal NM-A273 ACLUA, ACLUB REV 0.3 (1.0) - Lenovo Z50-70kasimkaNo ratings yet

- COM Express Carrier Design Guide 1.0Document160 pagesCOM Express Carrier Design Guide 1.0Mingje ShenNo ratings yet

- Ethernet: PC ScadaDocument43 pagesEthernet: PC ScadarockNo ratings yet

- Rdso Spec For STP Clause 5.15.9.1Document48 pagesRdso Spec For STP Clause 5.15.9.1sinhavivek12897No ratings yet

- GA-B85M-HD3: User's ManualDocument36 pagesGA-B85M-HD3: User's ManualChee LeongNo ratings yet

- Quanta 0P5A DA0P5AMB6D00 Rev 1A PDFDocument46 pagesQuanta 0P5A DA0P5AMB6D00 Rev 1A PDFDeMzo SMpNo ratings yet

- Sony Vaio VPC-W Series MBX-219 Quanta SY3 Schematic DiagramDocument44 pagesSony Vaio VPC-W Series MBX-219 Quanta SY3 Schematic DiagramRenatoNo ratings yet

- User Manual: Fanless Embedded Box PCDocument72 pagesUser Manual: Fanless Embedded Box PCbabuchas69No ratings yet

- Ex B150M V5Document26 pagesEx B150M V5FahrezaNo ratings yet

- NVIDIA Jetson Nano: Product Design GuideDocument62 pagesNVIDIA Jetson Nano: Product Design GuideVuk AntonicNo ratings yet

- Optiplex 780 Arrowhead RA03Document43 pagesOptiplex 780 Arrowhead RA03João Luis N. Do AmaralNo ratings yet

- Toshiba Satellite U400d - Quanta Bu2 - Rev 1aDocument35 pagesToshiba Satellite U400d - Quanta Bu2 - Rev 1aAngel Rose AlarasNo ratings yet

- DX DiagDocument13 pagesDX DiagPedro HenriqueNo ratings yet

- Biostar B550MX e Pro SpecDocument5 pagesBiostar B550MX e Pro SpecLuis Fernando Zavala GonzálezNo ratings yet

- PartsDocument4 pagesPartsMandy FisherNo ratings yet

- MSI - 7642v1.0 (G52 76421X1) (890GXM G65) PDFDocument110 pagesMSI - 7642v1.0 (G52 76421X1) (890GXM G65) PDFКирилл КошкинNo ratings yet

- 1.2.1.13 Lab - Research Computer Components PDFDocument3 pages1.2.1.13 Lab - Research Computer Components PDFAnonymous jtNxAr0% (1)

- Z8NR-D12 Vs Z8NA-D6Document3 pagesZ8NR-D12 Vs Z8NA-D6starams50% (1)

- PowerEdge 11G T610 Tower Server Details - DellDocument3 pagesPowerEdge 11G T610 Tower Server Details - DellPrasetio SigitNo ratings yet

- Imba9454 PDFDocument228 pagesImba9454 PDFJose SoaresNo ratings yet

- HP EliteBook 840 G5-QuickSpecsDocument37 pagesHP EliteBook 840 G5-QuickSpecsChristopher Emeka-ChrisNo ratings yet

- MB Manual Ga-H81m-S1 v2.1 eDocument34 pagesMB Manual Ga-H81m-S1 v2.1 eDraghiNikoNo ratings yet

- DesktopDocument11 pagesDesktopvelusamys1No ratings yet

- 2.5.F PC Asus ROGDocument3 pages2.5.F PC Asus ROGWahyuni HasanNo ratings yet

- Virtex-5 Family Overview: General DescriptionDocument13 pagesVirtex-5 Family Overview: General Descriptionviraldoshi1989No ratings yet

Cpu-cfc

Cpu-cfc

Uploaded by

istiakeislam7Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Cpu-cfc

Cpu-cfc

Uploaded by

istiakeislam7Copyright:

Available Formats

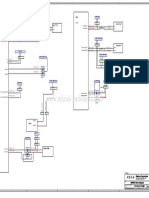

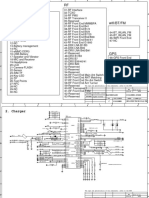

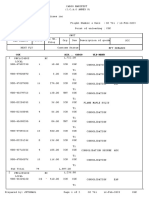

Main Board

CFG U0301E

CFG Straps

BGA1440

0Ohm R0610 B31 BN25 1 T0606

22 CLK_CPU_BCLK BCLKP CFG[0]

0Ohm 2 1 R0609 CLK_CPU_BCLK_X1 A32 BN27 CFG0 1 T0607

22 CLK_CPU_BCLK# BCLKN CFG[1] +1.0V_VCCST

2 1 CLK_CPU_BCLK#_X1 BN26 CFG1 1 T0608

CFG[2]

0Ohm R0608 D35 BN28 CFG2

22 CLK_PCI_BCLK PCI_BCLKP CFG[3]

0Ohm 2 1 R0607 CLK_PCI_BCLK_X1 C36 BR20 CFG3 1 T0610

22 CLK_PCI_BCLK#

2 1 CLK_PCI_BCLK#_X1

PCI_BCLKN CFG[4]

BM20 CFG4 1 T0611 R0617 1 2 51Ohm CFG Straps for Processor

CFG[5]

0Ohm R0611 E31 BT20 CFG5 1 T0612 XDP_TDO_CPU

22 CLK_24M CLK24P CFG[6] ref : Intel 544924_Skylake_EDS_Vol_1_Rev0.9 P.121

0Ohm 2 1 R0612 CLK_24M_X1 D31 BP20 CFG6 1 T0613 R0633 1 @ 2 51Ohm

22 CLK_24M# CLK24N CFG[7]

2 1 CLK_24M#_X1 BR23 CFG7 1 T0614 XDP_TDI_CPU

CFG[8]

BR22 CFG8 1 T0615 R0630 1 @ 2 51Ohm

CFG[9] CFG[0] : Stall reset sequence after PCU PLL lock until de-asserted

BT23 CFG9 1 T0616 XDP_TMS_CPU

CFG[10]

BT22 CFG10 1 T0617 R0613 1 2 51Ohm - 1 : (Default) Normal Operation; No stall

CFG[11]

CFG[12]

BM19 CFG11 1 T0618 XDP_TCLK_CPU - 0 : Stall

R0619 56Ohm BR19 CFG12 1 T0619 R0625 1 2 51Ohm

+1.0V_VCCST CFG[13]

2 1 BP19 CFG13 1 T0620 XDP_TRST_CPU#

CFG[14] CFG[1] : Reserved Configuration Lane

R0618 1 2 220Ohm BH31 BT19 CFG14 1 T0621

80 P_SVID_ALERT#_X2 VIDALERT# CFG[15]

P_SVID_ALERT# BH32 CFG15 Reserved Configuration Lane

80 P_SVID_CLK_X2 VIDSCK

P_SVID_CLK_X2 BH29 BN23 1 T0622

80 P_SVID_DATA_X2 VIDSOUT CFG[17]

P_SVID_DATA_X2 BR30 BP23 CFG17 1 T0623

PROCHOT# CFG[16] CFG[2] : PCI Express* Static x16 Lane Numbering Reversal

R0601 100Ohm H_PROCHOT_D# BP22 CFG16 1 T0624

+1.0V_VCCST CFG[19]

2 1% 1 BT13 BN22 CFG19 1 T0625 - 1 : (Default) Normal Operation

DDR_VTT_CNTL CFG[18]

DDR_VTT_CTRL CFG18 - 0 : Lane Numbers Reversed

BR27 1 T0626 R0605 1 1% 2 1KOhm

must close to CPU BPM#[0]

BT27 XDP_BPM0 1 T0627 CFG0 @

BPM#[1] CFG[3] : Reserved configuration lanes

BM31 XDP_BPM1 1 T0601

BPM#[2]

R0620 1 2 60.4Ohm H13 BT30 XDP_BPM2 1 T0602 R0634 1 1% 2 1KOhm Reserved Configuration Lane

58 VCCST_PWRGD_CPU VCCST_PWRGD BPM#[3]

H_VCCST_PWRGD XDP_BPM3 CFG1 @

R0621 0Ohm BT31

20 H_CPUPWRGD PROCPWRGD CFG[4] : eDP Enable

R0606 2 1 0Ohm H_CPUPWRGD_X1 BP35 BT28 1 2 SL0606 R0627 1 1% 2 1KOhm

21 PCH_PLTRST_CPU# RESET# PROC_TDO 0402 PCH_JTAG_TDO 20

PLTRST_CPU# BM34 BL32 XDP_TDO_CPU 1 2 SL0603 CFG2 - 1 : Disabled

21 H_PM_SYNC PM_SYNC PROC_TDI 0402 PCH_JTAG_TDI 20

21 H_PM_DOWN

R0622 1 2 20Ohm BP31

PM_DOWN PROC_TMS

BP28 XDP_TDI_CPU 1 2 SL0602

PCH_JTAG_TMS 20

- 0 : Enabled

R0623 2 1 0Ohm BT34 BR28 1 0402 2 1 2

H_PM_DOWN_X1 XDP_TMS_CPU SL0601 R0635 1% 1KOhm

30 PECI_EC PECI PROC_TCK 0402 PCH_JTAGX 20

R0624 1 2 12Ohm H_PECI J31 XDP_TCLK_CPU CFG3 @

21 PCH_PECI THERMTRIP# CFG[6:5] : PCI Expres* Bifurcation

H_THERMTRIP# BP30 1 2 SL0607

21 PCH_THERMTRIP# PROC_TRST# 0402 CPU_TRST# 27

T0603 1 BR33 BL30 XDP_TRST_CPU# 1 2 SL0605 R0632 1 1% 2 1KOhm - 00 : 1 x8 , 2 x4 PCI Express*

SKTOCC# PROC_PREQ# 0402 PCH_PREQ# 27

T0604 1 H_SKTOCC# BN1

PROC_SELECT# PROC_PRDY#

BP27 XDP_PREQ# 1 2 SL0604

PCH_PRDY# 27

CFG4 @ - 01 : Reserved

0402

H_PROC_SELECT# XDP_PRDY# - 10 : 2 x8 PCI Express*

T0605 1 BM30 R0628 1 1% 2 1KOhm - 11 : 1 x16 PCI Express*

CATERR#

H_CATERR# BT25 CFG5 @

CFG_RCOMP

CFG[7] : PEG Training

R0626 1 1% 2 1KOhm

2

CFG6 @ - 1 : (Default) PEG Train Immediately Following RESET# de-assertion

R0616 - 0 : PEG Wait for BIOS for Training

BGA1140 49.9Ohm R0629 1 1% 2 1KOhm

1% CFG7 @

+1.0V_VCCST

CFG[19:8] : Reserved Configuration Lanes

1

Place close to CPU Reserved Configuration Lanes

GND

R0636 1 2 51Ohm

H_CATERR#

For CPU states check Intel 544924_Skylake_EDS_Vol_1_Rev0.9 P.121

Richard 20141209

Boundary Scan TP (CPU) R0.1-37

T0628 1 T0629 1

XDP_PREQ# XDP_TMS_CPU

T0630 1 T0631 1

XDP_PRDY# XDP_TRST_CPU#

T0632 1 T0633 1

CFG3 XDP_TDI_CPU

T0634 1 T0635 1

XDP_TDO_CPU XDP_TCLK_CPU

DDR_VTT_CTRL:

System Memory Power Gate Control:

Disables the platform memory VTT regulator

in C8 and deeper and S3.

Ref:544924_544924_Skylake_EDS_Vol_1_Rev0.9.pdf P.120

For EMI VTT Enable

@ +1.2V +3VS

C0603 1 2 680PF/50V

H_CPUPWRGD

@

C0604 1 2 680PF/50V U0301K

PECI_EC

1

BGA1440

1

@ R0603 0OHM C0602

C0605 1 2 680PF/50V D1 BM33 DDR_VTT_CTRL 1 2 0.1UF/25V R0604

RSVD_TP13 RSVD_TP10

PCH_PREQ# E1 BL33 U0601 300KOhm

RSVD_TP14 RSVD_TP9

2

@ E3

2

RSVD_TP16

C0606 1 2 680PF/50V E2 BJ14 1 NC 5

RSVD_TP15 RSVD_TP2 VCC

PCH_JTAG_TDI BJ13 R0602 @ 0OHM 2 A

RSVD_TP1

BR1 1 2 DDR_PG_CTRL_RR 3 Y 4 R0640 0OHM

RSVD_TP11 GND DDR_PG_CTRL 86

BT2 BK28 1 2

RSVD_TP12 RSVD19

BJ28

RSVD12

@ BN35 74AUP1G07GW

RSVD33

C0608 1 2 680PF/50V BJ18

VSS201

H_PM_SYNC J24

RSVD48

@ H24 BJ16

RSVD47 RSVD_TP3

C0609 1 2 680PF/50V BN33 BK16

RSVD32 RSVD_TP7

H_PM_DOWN BL34 R0650 0OHM

RSVD28 11,30,45,57,70,84,88 SUSB_EC#

@ 1 2 @SUSB

C0610 1 2 680PF/50V N29 BK24

RSVD50 RSVD_TP8

PCH_JTAG_TMS R14 BJ24

RSVD51 RSVD_TP4

AE29

AA14

RSVD4

BK21

Control From EC SUSB

RSVD3 RSVD15

BJ21

RSVD8

@ A36

GND RSVD1

C0612 1 2 680PF/50V A37 BT17

PCH_PRDY#

RSVD2 RSVD41

BR17 CPU SIDEBAND SIGNALS

RSVD37

@ H23 +VCCSTG

27 PCH_TRIGGER_CPU PROC_TRIGIN

C0613 1 2 680PF/50V R0631 1 2 30Ohm J23 BK18

27 CPU_TRIGGER_PCH PROC_TRIGOUT VSS211

PCH_JTAG_TDO CPU_TRIGGER_PCH_X1

@ F30 BJ34

1

RSVD44 RSVD_TP6

C0614 1 2 680PF/50V E30 BJ33

RSVD43 RSVD_TP5

PCH_JTAGX R0615 R0.1-11 OD

B30 GND 1KOhm

RSVD6

C30 D0608

2

RSVD42

G13 R0614 1

RSVD45

@ G3 AJ8 1 2 3

RSVD46 RSVD5 THRO_CPU# 30

C0616 1 2 680PF/50V J3 BL31 H_PROCHOT_D# H_PROCHOT_D#_R 2

RSVD49 RSVD27

XDP_BPM3 499OHM

1

B2 @ BAT54AW

NCTF1

B38 C0601

NCTF2

BP1 43PF/50V

NCTF3

2

BR35 BR2

RSVD39 NCTF4

BR31 C1 R0652 0OHM

RSVD38 NCTF5 IMVP8_VRHOT# 80

BH30 C38 1 2

RSVD7 NCTF6

R0653 0OHM

PWRLIMIT#_CPU 89

1 2

BGA1140

Project Name Rev

G752VY 2.0

Title : CPU CFG

Size

Dept.: Engineer:

ASUSTeK COMPUTER INC. NB1 Richard Liu

C

Date: Tuesday, July 21, 2015 Sheet 6 of 102

You might also like

- JBW1 - Rev2 PDFDocument1 pageJBW1 - Rev2 PDFSreekanthMylavarapuNo ratings yet

- Compal NM-A271 ACLU1&ACLU2 - G40-70 & G50-70 - REV 1.0 - Lenovo IdeaPad G40-70, G50-70 PDFDocument59 pagesCompal NM-A271 ACLU1&ACLU2 - G40-70 & G50-70 - REV 1.0 - Lenovo IdeaPad G40-70, G50-70 PDFDaniel NegutNo ratings yet

- Tesla RCM DiagramDocument4 pagesTesla RCM DiagrampeefincaNo ratings yet

- Cross Reference: K0402 M03 M M M2 M3 MDocument4 pagesCross Reference: K0402 M03 M M M2 M3 Mkatie farrellNo ratings yet

- Bluetooth 2 Click Schematic v102Document1 pageBluetooth 2 Click Schematic v102Ammar AlkindyNo ratings yet

- Astm A488Document1 pageAstm A488Mohamed FaragNo ratings yet

- IBM Thinkpad Z61 (Quanta BW2)Document80 pagesIBM Thinkpad Z61 (Quanta BW2)Maks ProstNo ratings yet

- Description of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QDocument1 pageDescription of Configuration C30: Generator Protection REG670 1MRK 502 074-BEN QTuấn Lê QuangNo ratings yet

- Check Flight Availability - Cathay Pacific CargoDocument1 pageCheck Flight Availability - Cathay Pacific CargoAde NugrahaNo ratings yet

- A351 Service ManualDocument15 pagesA351 Service ManualDark FoxNo ratings yet

- 610c rm-836 SchematicDocument42 pages610c rm-836 SchematicVladimir GutarraNo ratings yet

- 303 14 PDFDocument38 pages303 14 PDFTuan TranNo ratings yet

- DIY TP4056 Charger CircuitDocument1 pageDIY TP4056 Charger Circuitv3642093No ratings yet

- MaterialDocument2 pagesMaterialdurgeshwardNo ratings yet

- G700-T00 Circuit DiagramDocument28 pagesG700-T00 Circuit DiagramRiza Virsada0% (1)

- MT6572 SchematicDocument19 pagesMT6572 SchematicdomisoftNo ratings yet

- weatherSTAMP - UnknownDocument1 pageweatherSTAMP - UnknownJony DarkoNo ratings yet

- 1 Componente Plantate: Rohde & Schwarz TopexDocument8 pages1 Componente Plantate: Rohde & Schwarz TopexCristian DobreNo ratings yet

- Iprog Mainboard SCHDocument1 pageIprog Mainboard SCHnelson lince100% (1)

- SM Bus Block DiagramDocument1 pageSM Bus Block Diagramradu2000vNo ratings yet

- 05a-BSSOM - S13 - BSC ARCHITECTURE AND FUNCTIONS - 6-65894 - v6Document46 pages05a-BSSOM - S13 - BSC ARCHITECTURE AND FUNCTIONS - 6-65894 - v6azzou dino32No ratings yet

- Moog SpringDocument18 pagesMoog SpringRicardo Rangel PosadasNo ratings yet

- TC-P42XT50L: 42 Inch Class 720p Plasma HDTVDocument12 pagesTC-P42XT50L: 42 Inch Class 720p Plasma HDTVELECTRONICA J Y CENTRO ELECTRONICONo ratings yet

- G610 U00Document36 pagesG610 U00Mauriciø Ruiz100% (1)

- Kim Uno Rev1 SchematicDocument1 pageKim Uno Rev1 SchematicweaponNo ratings yet

- 1.SCH List: RF BB SchematicsDocument36 pages1.SCH List: RF BB SchematicsLuis RodriguezNo ratings yet

- AC6925ADatasheetV1 0Document12 pagesAC6925ADatasheetV1 0АлексNo ratings yet

- A245 04pa Schematics - Dec. 1992 PDFDocument16 pagesA245 04pa Schematics - Dec. 1992 PDFtrung vothaiNo ratings yet

- More Smoky Amp Rev.ADocument3 pagesMore Smoky Amp Rev.AGryf Audio CompanyNo ratings yet

- SchematicDocument1 pageSchematicHue TruongNo ratings yet

- NSM D4u CTG3832 1711173022Document4 pagesNSM D4u CTG3832 1711173022kamalshak050No ratings yet

- 59Document79 pages59jroyal692974No ratings yet

- 4X SCHDocument70 pages4X SCHCs FixNo ratings yet

- Oz8380aln B4 0 TRDocument1 pageOz8380aln B4 0 TRAnacleto ChitalakumbiNo ratings yet

- Megasquirtavr v2.2 SCH PDFDocument6 pagesMegasquirtavr v2.2 SCH PDFgiapy0000No ratings yet

- DesafioDocument1 pageDesafioWilliam Anderson FernandesNo ratings yet

- Empty 100-Pin TQFP PT MCU CARD 1Document5 pagesEmpty 100-Pin TQFP PT MCU CARD 1Marian VladianuNo ratings yet

- lpc1114 SynthDocument1 pagelpc1114 SynthMirel-Cătălin ChirilăNo ratings yet

- Oz8153ln D 0 TRDocument1 pageOz8153ln D 0 TRЖељко Гелић0% (1)

- Ford Figo b517 2010 25 Ewd10Document1 pageFord Figo b517 2010 25 Ewd10sandeepNo ratings yet

- QM - Xc7A35T - Ddr3 Core Board: User ManualDocument13 pagesQM - Xc7A35T - Ddr3 Core Board: User ManualNgoc AnhNo ratings yet

- Walkie Talkie GERBERDocument1 pageWalkie Talkie GERBERAbhishek TiwariNo ratings yet

- Specifications: PartsDocument1 pageSpecifications: PartsFabio Da Silva Assunçao AssunçaoNo ratings yet

- CXD2861ERDocument30 pagesCXD2861ERZaegorNo ratings yet

- MT6351VDocument1 pageMT6351Vant franzzyNo ratings yet

- MB39A128ADocument1 pageMB39A128AY. Leonel MolinaNo ratings yet

- 16 FebDocument2 pages16 Febemma sofiaNo ratings yet

- Maintenance Guide CA-01,02Document12 pagesMaintenance Guide CA-01,02Wolaé Mathurin Edmond AmegandjinNo ratings yet

- ATIC71B1Document1 pageATIC71B1budi nugrohoNo ratings yet

- GPS EspDocument5 pagesGPS Espjak broseNo ratings yet

- Pivar103 Pivar103: Pilm56701 Pilm56708 Pilm56701 Pilm56708Document1 pagePivar103 Pivar103: Pilm56701 Pilm56708 Pilm56701 Pilm56708Hiroshi KoikeNo ratings yet

- CM508Document1 pageCM508MarshdeLangeNo ratings yet

- PRACTICAL TESTDocument4 pagesPRACTICAL TESTFaris IzzatNo ratings yet

- Datasheet MB86C311BDocument23 pagesDatasheet MB86C311BFelipe ShaderNo ratings yet

- Faroe Dis x32 MB MV (18742-1 0gg02) PDFDocument69 pagesFaroe Dis x32 MB MV (18742-1 0gg02) PDFRosa María AmoneNo ratings yet

- NCP81206MNTXGDocument1 pageNCP81206MNTXGElla Wijaya ChandraNo ratings yet

- NCP81205Document1 pageNCP81205Tom TomNo ratings yet

- OpenVox IX210 Asterisk IP PBX DatasheetDocument2 pagesOpenVox IX210 Asterisk IP PBX Datasheetmaple4VOIPNo ratings yet

- User Guide: Lenovo Thinkbook 14 Gen 3 and Lenovo Thinkbook 15 Gen 3Document34 pagesUser Guide: Lenovo Thinkbook 14 Gen 3 and Lenovo Thinkbook 15 Gen 3Abdul Hady Abu BakarNo ratings yet

- Xilinx Xc7k160t-2ffg676i Fpga PriceDocument6 pagesXilinx Xc7k160t-2ffg676i Fpga PricejackNo ratings yet

- Poweredge R730 and R730Xd: Technical GuideDocument64 pagesPoweredge R730 and R730Xd: Technical Guideender40No ratings yet

- Compal NM-A273 ACLUA, ACLUB REV 0.3 (1.0) - Lenovo Z50-70Document59 pagesCompal NM-A273 ACLUA, ACLUB REV 0.3 (1.0) - Lenovo Z50-70kasimkaNo ratings yet

- COM Express Carrier Design Guide 1.0Document160 pagesCOM Express Carrier Design Guide 1.0Mingje ShenNo ratings yet

- Ethernet: PC ScadaDocument43 pagesEthernet: PC ScadarockNo ratings yet

- Rdso Spec For STP Clause 5.15.9.1Document48 pagesRdso Spec For STP Clause 5.15.9.1sinhavivek12897No ratings yet

- GA-B85M-HD3: User's ManualDocument36 pagesGA-B85M-HD3: User's ManualChee LeongNo ratings yet

- Quanta 0P5A DA0P5AMB6D00 Rev 1A PDFDocument46 pagesQuanta 0P5A DA0P5AMB6D00 Rev 1A PDFDeMzo SMpNo ratings yet

- Sony Vaio VPC-W Series MBX-219 Quanta SY3 Schematic DiagramDocument44 pagesSony Vaio VPC-W Series MBX-219 Quanta SY3 Schematic DiagramRenatoNo ratings yet

- User Manual: Fanless Embedded Box PCDocument72 pagesUser Manual: Fanless Embedded Box PCbabuchas69No ratings yet

- Ex B150M V5Document26 pagesEx B150M V5FahrezaNo ratings yet

- NVIDIA Jetson Nano: Product Design GuideDocument62 pagesNVIDIA Jetson Nano: Product Design GuideVuk AntonicNo ratings yet

- Optiplex 780 Arrowhead RA03Document43 pagesOptiplex 780 Arrowhead RA03João Luis N. Do AmaralNo ratings yet

- Toshiba Satellite U400d - Quanta Bu2 - Rev 1aDocument35 pagesToshiba Satellite U400d - Quanta Bu2 - Rev 1aAngel Rose AlarasNo ratings yet

- DX DiagDocument13 pagesDX DiagPedro HenriqueNo ratings yet

- Biostar B550MX e Pro SpecDocument5 pagesBiostar B550MX e Pro SpecLuis Fernando Zavala GonzálezNo ratings yet

- PartsDocument4 pagesPartsMandy FisherNo ratings yet

- MSI - 7642v1.0 (G52 76421X1) (890GXM G65) PDFDocument110 pagesMSI - 7642v1.0 (G52 76421X1) (890GXM G65) PDFКирилл КошкинNo ratings yet

- 1.2.1.13 Lab - Research Computer Components PDFDocument3 pages1.2.1.13 Lab - Research Computer Components PDFAnonymous jtNxAr0% (1)

- Z8NR-D12 Vs Z8NA-D6Document3 pagesZ8NR-D12 Vs Z8NA-D6starams50% (1)

- PowerEdge 11G T610 Tower Server Details - DellDocument3 pagesPowerEdge 11G T610 Tower Server Details - DellPrasetio SigitNo ratings yet

- Imba9454 PDFDocument228 pagesImba9454 PDFJose SoaresNo ratings yet

- HP EliteBook 840 G5-QuickSpecsDocument37 pagesHP EliteBook 840 G5-QuickSpecsChristopher Emeka-ChrisNo ratings yet

- MB Manual Ga-H81m-S1 v2.1 eDocument34 pagesMB Manual Ga-H81m-S1 v2.1 eDraghiNikoNo ratings yet

- DesktopDocument11 pagesDesktopvelusamys1No ratings yet

- 2.5.F PC Asus ROGDocument3 pages2.5.F PC Asus ROGWahyuni HasanNo ratings yet

- Virtex-5 Family Overview: General DescriptionDocument13 pagesVirtex-5 Family Overview: General Descriptionviraldoshi1989No ratings yet