Professional Documents

Culture Documents

C8051F38x-pages-62

C8051F38x-pages-62

Uploaded by

lingeshtjCopyright:

Available Formats

You might also like

- Cambridge IGCSE Mathematics Core and Extended Workbook by Ric Pimentel, Terry Wall PDFDocument97 pagesCambridge IGCSE Mathematics Core and Extended Workbook by Ric Pimentel, Terry Wall PDFPrince Yug86% (22)

- Charlotte Fiell, Peter Fiell The Story of Design From The Paleolithic To The Present (2016)Document516 pagesCharlotte Fiell, Peter Fiell The Story of Design From The Paleolithic To The Present (2016)Eylül Gökbudak100% (2)

- 2013 0667 TK Geo 13 ENG.123Document112 pages2013 0667 TK Geo 13 ENG.123SURYANo ratings yet

- Examination and Result Management System - TutorialsDuniya PDFDocument56 pagesExamination and Result Management System - TutorialsDuniya PDFAishwaryaNo ratings yet

- Speech & Language Therapy in Practice, Spring 2002Document32 pagesSpeech & Language Therapy in Practice, Spring 2002Speech & Language Therapy in PracticeNo ratings yet

- DOT of Kansas (KDOT) - Bridge Design Manual (2014) PDFDocument1,240 pagesDOT of Kansas (KDOT) - Bridge Design Manual (2014) PDFJohnNo ratings yet

- Ad7817 7818Document20 pagesAd7817 7818congwem qinNo ratings yet

- KA5x03xx-SERIES: KA5H0365R, KA5M0365R, KA5L0365R KA5H0380R, KA5M0380R, KA5L0380R Fairchild Power Switch (FPS)Document14 pagesKA5x03xx-SERIES: KA5H0365R, KA5M0365R, KA5L0365R KA5H0380R, KA5M0380R, KA5L0380R Fairchild Power Switch (FPS)Bidu BiduNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFJORGENo ratings yet

- Embedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorDocument9 pagesEmbedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorHILLNo ratings yet

- KA5L0565R: Fairchild Power Switch (FPS)Document10 pagesKA5L0565R: Fairchild Power Switch (FPS)miloud1911No ratings yet

- 1H0280R FairchildDocument10 pages1H0280R FairchildgeridaltNo ratings yet

- Rfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets FeaturesDocument8 pagesRfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets Featuresaleh sharapovNo ratings yet

- KA1L0380RDocument12 pagesKA1L0380Radisurya13.afNo ratings yet

- KA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Document12 pagesKA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Saad LehlouNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1Document19 pagesRF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1bulli babuNo ratings yet

- AME431B-2.5V Adjustable PrecisionShunt RegulatorDocument23 pagesAME431B-2.5V Adjustable PrecisionShunt RegulatorLangllyNo ratings yet

- AOZ1284PI Support DocumentsDocument17 pagesAOZ1284PI Support Documentsarunmohan.parasNo ratings yet

- Regulador 4949ed PDFDocument11 pagesRegulador 4949ed PDFluizNo ratings yet

- Sbaa 343Document5 pagesSbaa 343Omayma BoukatayaNo ratings yet

- Polyphase Energy Metering IC With Pulse Output ADE7752/ADE7752ADocument1 pagePolyphase Energy Metering IC With Pulse Output ADE7752/ADE7752ABárbara ConstanzaNo ratings yet

- KA1M0880D: Fairchild Power Switch (FPS)Document10 pagesKA1M0880D: Fairchild Power Switch (FPS)ja jaNo ratings yet

- Getting Started With ADCC For PIC18 PDFDocument23 pagesGetting Started With ADCC For PIC18 PDFzhangsanNo ratings yet

- Multifunction Very Low Drop Voltage Regulator: DescriptionDocument10 pagesMultifunction Very Low Drop Voltage Regulator: DescriptionErasmo FrancoNo ratings yet

- Noninverting Circuit For High-To-Low Voltage Level Translation Very ImportantDocument7 pagesNoninverting Circuit For High-To-Low Voltage Level Translation Very Importantsung quekNo ratings yet

- KA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)Document10 pagesKA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- KA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Document10 pagesKA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Guilherme Ribeiro BarbosaNo ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- KA1L0365R/KA1M0365R/KA1H0365R: Fairchild Power Switch (FPS)Document10 pagesKA1L0365R/KA1M0365R/KA1H0365R: Fairchild Power Switch (FPS)periNo ratings yet

- Features Applications: Sbvs022B - September 2000 - Revised June 2009Document17 pagesFeatures Applications: Sbvs022B - September 2000 - Revised June 2009demononesNo ratings yet

- Ref 102Document19 pagesRef 102Janosi ParaNo ratings yet

- NCP431A, SC431A, NCP431B, NCP432B Series Programmable Precision ReferencesDocument17 pagesNCP431A, SC431A, NCP431B, NCP432B Series Programmable Precision ReferencesPedro OrtegaNo ratings yet

- Aoz1212ai PDFDocument18 pagesAoz1212ai PDF060279No ratings yet

- Ad5547 5557Document20 pagesAd5547 5557이길현No ratings yet

- AS3691 DatasheetDocument22 pagesAS3691 DatasheetRnDES1 CMLNo ratings yet

- C8051F38x-pages-63Document1 pageC8051F38x-pages-63lingeshtjNo ratings yet

- AOZ1282CIDocument13 pagesAOZ1282CIBelalang TempurNo ratings yet

- Bc2401 315/433Mhz Super-Regenerative Ook RX Ic: Features General DescriptionDocument7 pagesBc2401 315/433Mhz Super-Regenerative Ook RX Ic: Features General DescriptionMadhusudanan AshokNo ratings yet

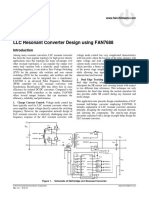

- LLC Resonant Converter Design Using FAN7688: 2. Dual Edge Tracking SR Control: FAN7688 Uses ADocument21 pagesLLC Resonant Converter Design Using FAN7688: 2. Dual Edge Tracking SR Control: FAN7688 Uses APhúc ThiệnNo ratings yet

- AH277ADocument10 pagesAH277Adhana0809No ratings yet

- ADE7757 Analog DevicesDocument14 pagesADE7757 Analog DevicesKashif HassanNo ratings yet

- Ad 5791Document27 pagesAd 5791Truong Dang VinhNo ratings yet

- TS1117BDocument8 pagesTS1117BImonkNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2Document17 pagesRF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2mohsengsmNo ratings yet

- Mosfet Potencia Sihlr014Document8 pagesMosfet Potencia Sihlr014Jorge Martinez PerezNo ratings yet

- FFB 2907 - FairchildDocument13 pagesFFB 2907 - FairchildStevenNo ratings yet

- FP5217Document14 pagesFP5217عبدالله ابراهيمNo ratings yet

- FAN1117A: 1A Adjustable/Fixed Low Dropout Linear RegulatorDocument9 pagesFAN1117A: 1A Adjustable/Fixed Low Dropout Linear RegulatorVicente MiróNo ratings yet

- Arduino Nano 3 User ManualDocument20 pagesArduino Nano 3 User ManualDj PopNo ratings yet

- F DatasheetDocument16 pagesF DatasheetTerelia Kinan GallenNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- KA3S0765R/KA3S0765RF: Fairchild Power Switch (FPS)Document13 pagesKA3S0765R/KA3S0765RF: Fairchild Power Switch (FPS)Maxi PereiraNo ratings yet

- A2I09VD030NDocument23 pagesA2I09VD030NAhmedNo ratings yet

- 3S0880RDocument14 pages3S0880RgdiliogNo ratings yet

- SPS Ka1m0880: To-3p-5lDocument8 pagesSPS Ka1m0880: To-3p-5lAndrzej WojtalaNo ratings yet

- Ka1m0880b DatasheetDocument8 pagesKa1m0880b DatasheetluisNo ratings yet

- K Type Thermocouple Meseurement Circuit With Precision ADCDocument9 pagesK Type Thermocouple Meseurement Circuit With Precision ADCmehdi.bzinebNo ratings yet

- Cap 2Document8 pagesCap 2pietisc pietiscNo ratings yet

- Mk6 Softstart PSUDocument1 pageMk6 Softstart PSUGlobal Ship SparesNo ratings yet

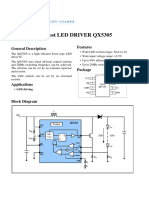

- Boost LED DRIVER QX5305: General Description FeaturesDocument6 pagesBoost LED DRIVER QX5305: General Description FeaturesGenir MacagnanNo ratings yet

- Linear Regulators Fundamentals and CompensationDocument32 pagesLinear Regulators Fundamentals and Compensationnaiad09No ratings yet

- Adjustable Precision Shunt Regulators: NC AnodeDocument15 pagesAdjustable Precision Shunt Regulators: NC AnodeAmir QayyumNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- C8051F38x-pages-37Document1 pageC8051F38x-pages-37lingeshtjNo ratings yet

- C8051F38x-pages-30Document1 pageC8051F38x-pages-30lingeshtjNo ratings yet

- C8051F38x-pages-35Document1 pageC8051F38x-pages-35lingeshtjNo ratings yet

- C8051F38x-pages-23Document1 pageC8051F38x-pages-23lingeshtjNo ratings yet

- doc0180-pages-25Document1 pagedoc0180-pages-25lingeshtjNo ratings yet

- C8051F38x-pages-12Document1 pageC8051F38x-pages-12lingeshtjNo ratings yet

- doc0180-pages-23Document1 pagedoc0180-pages-23lingeshtjNo ratings yet

- doc0180-pages-16Document1 pagedoc0180-pages-16lingeshtjNo ratings yet

- CommonAPICppAMMSeoul (1)-pages-18Document1 pageCommonAPICppAMMSeoul (1)-pages-18lingeshtjNo ratings yet

- Linux Kernel SlidesDocument473 pagesLinux Kernel SlideslingeshtjNo ratings yet

- doc0180-pages-2Document1 pagedoc0180-pages-2lingeshtjNo ratings yet

- KBI - Group 2 - Community Mapping (RRA & PRA)Document13 pagesKBI - Group 2 - Community Mapping (RRA & PRA)Yudha OkpriandaNo ratings yet

- Sustainable DevelopmentDocument11 pagesSustainable DevelopmentrcayNo ratings yet

- Goodle Drive Tutorial # 2Document4 pagesGoodle Drive Tutorial # 2JOEL P. RODRIGUEZNo ratings yet

- CRM Opc BlainesDocument2 pagesCRM Opc BlainesVara Prasad PaluriNo ratings yet

- See Also:: Eighteenth Dynasty of Egypt Family TreeDocument1 pageSee Also:: Eighteenth Dynasty of Egypt Family TreeBilly FrankovickNo ratings yet

- Biography of Francisco ArcellanaDocument4 pagesBiography of Francisco ArcellanabooboothefoolNo ratings yet

- Rand Oh Di So 22324668100220Document2 pagesRand Oh Di So 22324668100220Crystal RojasNo ratings yet

- Activity 1 - Mad LibsDocument4 pagesActivity 1 - Mad Libsapi-298144022No ratings yet

- Unit-4 Disaster Management NotesDocument33 pagesUnit-4 Disaster Management Notesholalo6378No ratings yet

- Contadores 2GDocument5 pagesContadores 2GJosé Luis Gutiérrez NietoNo ratings yet

- Cornwall's Disadvantaged NeighbourhoodsDocument32 pagesCornwall's Disadvantaged NeighbourhoodsNick Wilding100% (2)

- Behavioral Finance AssignmentDocument8 pagesBehavioral Finance Assignmentthulli06No ratings yet

- Gravograph MachinesDocument2 pagesGravograph MachinesIndranil ChowdhuryNo ratings yet

- Infectious Laryngotracheitis in Poultry: Razol RazalanDocument27 pagesInfectious Laryngotracheitis in Poultry: Razol RazalanLemuel Lagasca Razalan IVNo ratings yet

- Mass SongsDocument20 pagesMass SongsJason LayaNo ratings yet

- National Rural Health MissionDocument418 pagesNational Rural Health MissionRoy GoldenNo ratings yet

- M2 Imalis Schedule 2021-2022-: July 21StDocument1 pageM2 Imalis Schedule 2021-2022-: July 21StMohammed Abdul Rahman KhanNo ratings yet

- Science 9 Q4 Intro To KinematicsDocument54 pagesScience 9 Q4 Intro To KinematicsSire WillNo ratings yet

- Road Safety Banner 2018Document18 pagesRoad Safety Banner 2018Safety ManagerNo ratings yet

- MPCA Response 5.29.20Document2 pagesMPCA Response 5.29.20Duluth News TribuneNo ratings yet

- Suplemente - Junio - VIRTUAL REALITY Exam UGRDocument1 pageSuplemente - Junio - VIRTUAL REALITY Exam UGRAnaGarcíaReyesNo ratings yet

- EXTER T150-st: Installation ManualDocument24 pagesEXTER T150-st: Installation ManualdwdawadNo ratings yet

- Andreas: Focused Assessment With Sonography in TraumaDocument13 pagesAndreas: Focused Assessment With Sonography in Traumarina paramitaNo ratings yet

- Operating System Unit 3 Part 1Document20 pagesOperating System Unit 3 Part 1kuldeep kumarNo ratings yet

C8051F38x-pages-62

C8051F38x-pages-62

Uploaded by

lingeshtjCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

C8051F38x-pages-62

C8051F38x-pages-62

Uploaded by

lingeshtjCopyright:

Available Formats

C8051F380/1/2/3/4/5/6/7/C

7. Voltage Reference Options

The Voltage reference multiplexer for the ADC is configurable to use an externally connected voltage ref-

erence, the on-chip reference voltage generator routed to the VREF pin, the unregulated power supply

voltage (VDD), or the regulated 1.8 V internal supply (see Figure 7.1). The REFSL bit in the Reference

Control register (REF0CN, SFR Definition 7.1) selects the reference source for the ADC. For an external

source or the on-chip reference, REFSL should be set to 0 to select the VREF pin. To use VDD as the ref-

erence source, REFSL should be set to 1. To override this selection and use the internal regulator as the

reference source, the REGOVR bit can be set to 1.

The BIASE bit enables the internal voltage bias generator, which is used by many of the analog peripher-

als on the device. This bias is automatically enabled when any peripheral which requires it is enabled, and

it does not need to be enabled manually. The bias generator may be enabled manually by writing a 1 to the

BIASE bit in register REF0CN. The electrical specifications for the voltage reference circuit are given in

Table 5.12.

The C8051F380/1/2/3/C devices also include an on-chip voltage reference circuit which consists of a

1.2 V, temperature stable bandgap voltage reference generator and a selectable-gain output buffer ampli-

fier. The buffer is configured for 1x or 2x gain using the REFBGS bit in register REF0CN. On the 1x gain

setting the output voltage is nominally 1.2 V, and on the 2x gain setting the output voltage is nominally

2.4 V. The on-chip voltage reference can be driven on the VREF pin by setting the REFBE bit in register

REF0CN to a 1. The maximum load seen by the VREF pin must be less than 200 µA to GND. Bypass

capacitors of 0.1 µF and 4.7 µF are recommended from the VREF pin to GND, and a minimum of 0.1uF is

required. If the on-chip reference is not used, the REFBE bit should be cleared to 0. Electrical specifica-

tions for the on-chip voltage reference are given in Table 5.12.

Important Note about the VREF Pin: When using either an external voltage reference or the on-chip ref-

erence circuitry, the VREF pin should be configured as an analog pin and skipped by the Digital Crossbar.

Refer to Section “20. Port Input/Output” on page 153 for the location of the VREF pin, as well as details of

how to configure the pin in analog mode and to be skipped by the crossbar.

REF0CN

REGOVR

REFBGS

TEMPE

REFBE

REFSL

BIASE

To ADC, IDAC,

EN Internal Oscillators,

Bias Generator

Reference,

IOSCEN TempSensor

EN

VDD External Temp Sensor To Analog Mux

Voltage

Reference

R1 Circuit

VREF EN

1x/2x 1.2V Reference REFBE

REFBGS

GND 0

0

+

4.7F 0.1F VREF

VDD 1

(to ADC)

Recommended Bypass Internal

1

Capacitors Regulator

REGOVR

Figure 7.1. Voltage Reference Functional Block Diagram

Rev. 1.5 66

You might also like

- Cambridge IGCSE Mathematics Core and Extended Workbook by Ric Pimentel, Terry Wall PDFDocument97 pagesCambridge IGCSE Mathematics Core and Extended Workbook by Ric Pimentel, Terry Wall PDFPrince Yug86% (22)

- Charlotte Fiell, Peter Fiell The Story of Design From The Paleolithic To The Present (2016)Document516 pagesCharlotte Fiell, Peter Fiell The Story of Design From The Paleolithic To The Present (2016)Eylül Gökbudak100% (2)

- 2013 0667 TK Geo 13 ENG.123Document112 pages2013 0667 TK Geo 13 ENG.123SURYANo ratings yet

- Examination and Result Management System - TutorialsDuniya PDFDocument56 pagesExamination and Result Management System - TutorialsDuniya PDFAishwaryaNo ratings yet

- Speech & Language Therapy in Practice, Spring 2002Document32 pagesSpeech & Language Therapy in Practice, Spring 2002Speech & Language Therapy in PracticeNo ratings yet

- DOT of Kansas (KDOT) - Bridge Design Manual (2014) PDFDocument1,240 pagesDOT of Kansas (KDOT) - Bridge Design Manual (2014) PDFJohnNo ratings yet

- Ad7817 7818Document20 pagesAd7817 7818congwem qinNo ratings yet

- KA5x03xx-SERIES: KA5H0365R, KA5M0365R, KA5L0365R KA5H0380R, KA5M0380R, KA5L0380R Fairchild Power Switch (FPS)Document14 pagesKA5x03xx-SERIES: KA5H0365R, KA5M0365R, KA5L0365R KA5H0380R, KA5M0380R, KA5L0380R Fairchild Power Switch (FPS)Bidu BiduNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFJORGENo ratings yet

- Embedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorDocument9 pagesEmbedded ASIC Macrocell: Power Management RE028 Fixed 4.5V 30 Ma LDO Voltage RegulatorHILLNo ratings yet

- KA5L0565R: Fairchild Power Switch (FPS)Document10 pagesKA5L0565R: Fairchild Power Switch (FPS)miloud1911No ratings yet

- 1H0280R FairchildDocument10 pages1H0280R FairchildgeridaltNo ratings yet

- Rfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets FeaturesDocument8 pagesRfd14N05L, Rfd14N05Lsm, Rfp14N05L: 14A, 50V, 0.100 Ohm, Logic Level, N-Channel Power Mosfets Featuresaleh sharapovNo ratings yet

- KA1L0380RDocument12 pagesKA1L0380Radisurya13.afNo ratings yet

- KA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Document12 pagesKA1L0380B/KA1L0380RB/KA1M0380RB/ KA1H0380RB: Fairchild Power Switch (SPS)Saad LehlouNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1Document19 pagesRF LDMOS Wideband Integrated Power Amplifier: MMRF2004NBR1bulli babuNo ratings yet

- AME431B-2.5V Adjustable PrecisionShunt RegulatorDocument23 pagesAME431B-2.5V Adjustable PrecisionShunt RegulatorLangllyNo ratings yet

- AOZ1284PI Support DocumentsDocument17 pagesAOZ1284PI Support Documentsarunmohan.parasNo ratings yet

- Regulador 4949ed PDFDocument11 pagesRegulador 4949ed PDFluizNo ratings yet

- Sbaa 343Document5 pagesSbaa 343Omayma BoukatayaNo ratings yet

- Polyphase Energy Metering IC With Pulse Output ADE7752/ADE7752ADocument1 pagePolyphase Energy Metering IC With Pulse Output ADE7752/ADE7752ABárbara ConstanzaNo ratings yet

- KA1M0880D: Fairchild Power Switch (FPS)Document10 pagesKA1M0880D: Fairchild Power Switch (FPS)ja jaNo ratings yet

- Getting Started With ADCC For PIC18 PDFDocument23 pagesGetting Started With ADCC For PIC18 PDFzhangsanNo ratings yet

- Multifunction Very Low Drop Voltage Regulator: DescriptionDocument10 pagesMultifunction Very Low Drop Voltage Regulator: DescriptionErasmo FrancoNo ratings yet

- Noninverting Circuit For High-To-Low Voltage Level Translation Very ImportantDocument7 pagesNoninverting Circuit For High-To-Low Voltage Level Translation Very Importantsung quekNo ratings yet

- KA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)Document10 pagesKA1L0880B/KA1M0880B: Fairchild Power Switch (FPS)vetchboyNo ratings yet

- KA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Document10 pagesKA1M0565R/KA1H0565R: Fairchild Power Switch (FPS)Guilherme Ribeiro BarbosaNo ratings yet

- Datasheet DMO565RDocument21 pagesDatasheet DMO565RSteve Bravo83% (6)

- KA1L0365R/KA1M0365R/KA1H0365R: Fairchild Power Switch (FPS)Document10 pagesKA1L0365R/KA1M0365R/KA1H0365R: Fairchild Power Switch (FPS)periNo ratings yet

- Features Applications: Sbvs022B - September 2000 - Revised June 2009Document17 pagesFeatures Applications: Sbvs022B - September 2000 - Revised June 2009demononesNo ratings yet

- Ref 102Document19 pagesRef 102Janosi ParaNo ratings yet

- NCP431A, SC431A, NCP431B, NCP432B Series Programmable Precision ReferencesDocument17 pagesNCP431A, SC431A, NCP431B, NCP432B Series Programmable Precision ReferencesPedro OrtegaNo ratings yet

- Aoz1212ai PDFDocument18 pagesAoz1212ai PDF060279No ratings yet

- Ad5547 5557Document20 pagesAd5547 5557이길현No ratings yet

- AS3691 DatasheetDocument22 pagesAS3691 DatasheetRnDES1 CMLNo ratings yet

- C8051F38x-pages-63Document1 pageC8051F38x-pages-63lingeshtjNo ratings yet

- AOZ1282CIDocument13 pagesAOZ1282CIBelalang TempurNo ratings yet

- Bc2401 315/433Mhz Super-Regenerative Ook RX Ic: Features General DescriptionDocument7 pagesBc2401 315/433Mhz Super-Regenerative Ook RX Ic: Features General DescriptionMadhusudanan AshokNo ratings yet

- LLC Resonant Converter Design Using FAN7688: 2. Dual Edge Tracking SR Control: FAN7688 Uses ADocument21 pagesLLC Resonant Converter Design Using FAN7688: 2. Dual Edge Tracking SR Control: FAN7688 Uses APhúc ThiệnNo ratings yet

- AH277ADocument10 pagesAH277Adhana0809No ratings yet

- ADE7757 Analog DevicesDocument14 pagesADE7757 Analog DevicesKashif HassanNo ratings yet

- Ad 5791Document27 pagesAd 5791Truong Dang VinhNo ratings yet

- TS1117BDocument8 pagesTS1117BImonkNo ratings yet

- RF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2Document17 pagesRF LDMOS Wideband Integrated Power Amplifier: MHV5IC1810NR2mohsengsmNo ratings yet

- Mosfet Potencia Sihlr014Document8 pagesMosfet Potencia Sihlr014Jorge Martinez PerezNo ratings yet

- FFB 2907 - FairchildDocument13 pagesFFB 2907 - FairchildStevenNo ratings yet

- FP5217Document14 pagesFP5217عبدالله ابراهيمNo ratings yet

- FAN1117A: 1A Adjustable/Fixed Low Dropout Linear RegulatorDocument9 pagesFAN1117A: 1A Adjustable/Fixed Low Dropout Linear RegulatorVicente MiróNo ratings yet

- Arduino Nano 3 User ManualDocument20 pagesArduino Nano 3 User ManualDj PopNo ratings yet

- F DatasheetDocument16 pagesF DatasheetTerelia Kinan GallenNo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- KA3S0765R/KA3S0765RF: Fairchild Power Switch (FPS)Document13 pagesKA3S0765R/KA3S0765RF: Fairchild Power Switch (FPS)Maxi PereiraNo ratings yet

- A2I09VD030NDocument23 pagesA2I09VD030NAhmedNo ratings yet

- 3S0880RDocument14 pages3S0880RgdiliogNo ratings yet

- SPS Ka1m0880: To-3p-5lDocument8 pagesSPS Ka1m0880: To-3p-5lAndrzej WojtalaNo ratings yet

- Ka1m0880b DatasheetDocument8 pagesKa1m0880b DatasheetluisNo ratings yet

- K Type Thermocouple Meseurement Circuit With Precision ADCDocument9 pagesK Type Thermocouple Meseurement Circuit With Precision ADCmehdi.bzinebNo ratings yet

- Cap 2Document8 pagesCap 2pietisc pietiscNo ratings yet

- Mk6 Softstart PSUDocument1 pageMk6 Softstart PSUGlobal Ship SparesNo ratings yet

- Boost LED DRIVER QX5305: General Description FeaturesDocument6 pagesBoost LED DRIVER QX5305: General Description FeaturesGenir MacagnanNo ratings yet

- Linear Regulators Fundamentals and CompensationDocument32 pagesLinear Regulators Fundamentals and Compensationnaiad09No ratings yet

- Adjustable Precision Shunt Regulators: NC AnodeDocument15 pagesAdjustable Precision Shunt Regulators: NC AnodeAmir QayyumNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- C8051F38x-pages-56Document1 pageC8051F38x-pages-56lingeshtjNo ratings yet

- C8051F38x-pages-55Document1 pageC8051F38x-pages-55lingeshtjNo ratings yet

- C8051F38x-pages-37Document1 pageC8051F38x-pages-37lingeshtjNo ratings yet

- C8051F38x-pages-30Document1 pageC8051F38x-pages-30lingeshtjNo ratings yet

- C8051F38x-pages-35Document1 pageC8051F38x-pages-35lingeshtjNo ratings yet

- C8051F38x-pages-23Document1 pageC8051F38x-pages-23lingeshtjNo ratings yet

- doc0180-pages-25Document1 pagedoc0180-pages-25lingeshtjNo ratings yet

- C8051F38x-pages-12Document1 pageC8051F38x-pages-12lingeshtjNo ratings yet

- doc0180-pages-23Document1 pagedoc0180-pages-23lingeshtjNo ratings yet

- doc0180-pages-16Document1 pagedoc0180-pages-16lingeshtjNo ratings yet

- CommonAPICppAMMSeoul (1)-pages-18Document1 pageCommonAPICppAMMSeoul (1)-pages-18lingeshtjNo ratings yet

- Linux Kernel SlidesDocument473 pagesLinux Kernel SlideslingeshtjNo ratings yet

- doc0180-pages-2Document1 pagedoc0180-pages-2lingeshtjNo ratings yet

- KBI - Group 2 - Community Mapping (RRA & PRA)Document13 pagesKBI - Group 2 - Community Mapping (RRA & PRA)Yudha OkpriandaNo ratings yet

- Sustainable DevelopmentDocument11 pagesSustainable DevelopmentrcayNo ratings yet

- Goodle Drive Tutorial # 2Document4 pagesGoodle Drive Tutorial # 2JOEL P. RODRIGUEZNo ratings yet

- CRM Opc BlainesDocument2 pagesCRM Opc BlainesVara Prasad PaluriNo ratings yet

- See Also:: Eighteenth Dynasty of Egypt Family TreeDocument1 pageSee Also:: Eighteenth Dynasty of Egypt Family TreeBilly FrankovickNo ratings yet

- Biography of Francisco ArcellanaDocument4 pagesBiography of Francisco ArcellanabooboothefoolNo ratings yet

- Rand Oh Di So 22324668100220Document2 pagesRand Oh Di So 22324668100220Crystal RojasNo ratings yet

- Activity 1 - Mad LibsDocument4 pagesActivity 1 - Mad Libsapi-298144022No ratings yet

- Unit-4 Disaster Management NotesDocument33 pagesUnit-4 Disaster Management Notesholalo6378No ratings yet

- Contadores 2GDocument5 pagesContadores 2GJosé Luis Gutiérrez NietoNo ratings yet

- Cornwall's Disadvantaged NeighbourhoodsDocument32 pagesCornwall's Disadvantaged NeighbourhoodsNick Wilding100% (2)

- Behavioral Finance AssignmentDocument8 pagesBehavioral Finance Assignmentthulli06No ratings yet

- Gravograph MachinesDocument2 pagesGravograph MachinesIndranil ChowdhuryNo ratings yet

- Infectious Laryngotracheitis in Poultry: Razol RazalanDocument27 pagesInfectious Laryngotracheitis in Poultry: Razol RazalanLemuel Lagasca Razalan IVNo ratings yet

- Mass SongsDocument20 pagesMass SongsJason LayaNo ratings yet

- National Rural Health MissionDocument418 pagesNational Rural Health MissionRoy GoldenNo ratings yet

- M2 Imalis Schedule 2021-2022-: July 21StDocument1 pageM2 Imalis Schedule 2021-2022-: July 21StMohammed Abdul Rahman KhanNo ratings yet

- Science 9 Q4 Intro To KinematicsDocument54 pagesScience 9 Q4 Intro To KinematicsSire WillNo ratings yet

- Road Safety Banner 2018Document18 pagesRoad Safety Banner 2018Safety ManagerNo ratings yet

- MPCA Response 5.29.20Document2 pagesMPCA Response 5.29.20Duluth News TribuneNo ratings yet

- Suplemente - Junio - VIRTUAL REALITY Exam UGRDocument1 pageSuplemente - Junio - VIRTUAL REALITY Exam UGRAnaGarcíaReyesNo ratings yet

- EXTER T150-st: Installation ManualDocument24 pagesEXTER T150-st: Installation ManualdwdawadNo ratings yet

- Andreas: Focused Assessment With Sonography in TraumaDocument13 pagesAndreas: Focused Assessment With Sonography in Traumarina paramitaNo ratings yet

- Operating System Unit 3 Part 1Document20 pagesOperating System Unit 3 Part 1kuldeep kumarNo ratings yet