Professional Documents

Culture Documents

313307-DIGITAL-TECHNIQUES-1

313307-DIGITAL-TECHNIQUES-1

Uploaded by

seemakasture75Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

313307-DIGITAL-TECHNIQUES-1

313307-DIGITAL-TECHNIQUES-1

Uploaded by

seemakasture75Copyright:

Available Formats

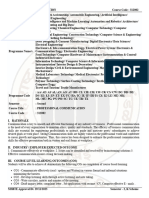

DIGITAL TECHNIQUES Course Code : 313307

: Artificial Intelligence/ Artificial Intelligence and Machine Learning/ Automation and

Robotics/ Computer Technology/

Computer Engineering/ Computer Science & Engineering/ Digital Electronics/ Data

Sciences/

Programme Name/s Electronics & Tele-communication Engg./ Electronics & Communication Engg./

Electronics Engineering/ Computer Hardware & Maintenance/

Instrumentation & Control/ Industrial Electronics/ Instrumentation/ Medical

Electronics/

Electronics & Computer Engg.

Programme Code : AI/ AN/ AO/ CM/ CO/ CW/ DE/ DS/ EJ/ ET/ EX/ HA/ IC/ IE/ IS/ MU/ TE

Semester : Third

Course Title : DIGITAL TECHNIQUES

Course Code : 313307

I. RATIONALE

Digitization implies use of digital circuits in most of automation and industrial systems. The knowledge of logic

gates, combinational and sequential circuits using discrete gates and digital ICs will enable students to interpret

working of digital equipment and test their functionality.

II. INDUSTRY / EMPLOYER EXPECTED OUTCOME

The aim of this course is to help students to attain the following industry/employer expected outcome through

various teaching learning experiences:

Student will able to test the functionality of the digital circuits/system.

III. COURSE LEVEL LEARNING OUTCOMES (COS)

Students will be able to achieve & demonstrate the following COs on completion of course based learning

CO1 - Apply number system and codes concept to interprete working of digital systems.

CO2 - Apply Boolean laws to minimize complex Boolean function.

CO3 - Develop combinational logic circuits for given applications.

CO4 - Develop sequential logic circuits using Flip-flops.

CO5 - Interpret the functions of data converters and memories in digital electronic systems.

IV. TEACHING-LEARNING & ASSESSMENT SCHEME

Learning Scheme Assessment Scheme

Actual

Based on LL &

Contact Based on

Theory TL

Course Course Hrs./Week SL

Course Title Abbr Credits Paper Total

Code Category/s SLH NLH Practical

Duration Marks

FA- SA-

CL TL LL Total FA-PR SA-PR SLA

TH TH

Max Max Max Min Max Min Max Min Max Min

DIGITAL

313307 DTE DSC 3 - 2 1 6 3 3 30 70 100 40 25 10 25# 10 25 10 175

TECHNIQUES

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

Total IKS Hrs for Sem. : 0 Hrs

Abbreviations: CL- ClassRoom Learning , TL- Tutorial Learning, LL-Laboratory Learning, SLH-Self Learning

Hours, NLH-Notional Learning Hours, FA - Formative Assessment, SA -Summative assessment, IKS - Indian

Knowledge System, SLA - Self Learning Assessment

Legends: @ Internal Assessment, # External Assessment, *# On Line Examination , @$ Internal Online

Examination

Note :

1. FA-TH represents average of two class tests of 30 marks each conducted during the semester.

2. If candidate is not securing minimum passing marks in FA-PR of any course then the candidate shall be

declared as "Detained" in that semester.

3. If candidate is not securing minimum passing marks in SLA of any course then the candidate shall be

declared as fail and will have to repeat and resubmit SLA work.

4. Notional Learning hours for the semester are (CL+LL+TL+SL)hrs.* 15 Weeks

5. 1 credit is equivalent to 30 Notional hrs.

6. * Self learning hours shall not be reflected in the Time Table.

7. * Self learning includes micro project / assignment / other activities.

V. THEORY LEARNING OUTCOMES AND ALIGNED COURSE CONTENT

Theory Learning Suggested

Learning content mapped with Theory Learning

Sr.No Outcomes (TLO's)aligned Learning

Outcomes (TLO's) and CO's.

to CO's. Pedagogies.

TLO 1.1 Convert the given

number from one number

system to another number

system.

TLO 1.2 Perform

arithmetic operations on Unit - I Number Systems

binary numbers. 1.1 Number Systems: Types of Number Systems (Binary,

TLO 1.3 Subtract given Octal, Decimal, Hexadecimal), conversion of number

binary numbers using 1’s systems

and 2’s compliment 1.2 Binary Arithematic: Addition, Subtraction,

Lecture Using

1 method. Multiplication and Division

Chalk-Board

TLO 1.4 Convert the given 1.3 Subtraction using 1's and 2's complement method

coded number into the 1.4 Codes: BCD, Gray code, Excess-3 and ASCII

other specified code. code,Code conversions, Applications of codes.

TLO 1.5 Write the 1.5 BCD Arithematic: BCD Addition, Subtraction using 9's

application of the given and 10's complement

code.

TLO 1.6 Perform BCD

addition and subtraction

for the given Decimal

numbers .

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

Theory Learning Suggested

Learning content mapped with Theory Learning

Sr.No Outcomes (TLO's)aligned Learning

Outcomes (TLO's) and CO's.

to CO's. Pedagogies.

TLO 2.1 Define the given

characteristics parameters

of the digital logic Unit - II Logic Gates and Boolean Algebra

families. 2.1 Logic Families: Characteristics Parameters of logic

TLO 2.2 Draw symbol and Families- Noise margin, Power dissipation, Figure of merit

truth table of given logic ,Fan in, Fan out, Speed of operation Current and Voltage

gates. parameters, Comparison of TTL, CMOS and ECL logic

Flipped

TLO 2.3 Explain the family

Classroom

2 concept of Buffer and 2.2 Introduction to positive and negative logic systems,

Lecture Using

Tristate logic . Logic Gates: Symbol ,Truth table of Basic logic

Chalk-Board

TLO 2.4 Implement basic gates(AND,OR,NOT),Universal gates(NAND,NOR) and

gates and other gates with Special purpose gates(EX-OR,EX-NOR)

the help of universal gate. 2.3 Buffer: Tristate logic, Unidirectional and Bidirectional

TLO 2.5 Simplify the 2.4 Boolean algebra : Laws of Boolean algebra, Duality

given expression using Theorem ,De-Morgan's theorem

Boolean laws and develop

logic circuits .

Unit - III Combinational Logic Circuits

TLO 3.1 Develop logic

3.1 Standard Boolean expression: Sum of products [SOP]

circuits for standard

and Products of Sum [POS], Min-term and Max-term,

SOP/POS form of the

SOP-POS form conversion, realisation using NAND/NOR

given logic expression.

gates

TLO 3.2 Minimize the

3.2 Boolean Expression reduction using K-map:

given logic expression

Minimization of Boolean expressions (upto 4 variables)

using Kmap (up to 4 Flipped

using SOP and POS form

variables). Classroom

3.3 Arithematic circuits : design Half and Full Adder using

3 TLO 3.3 Design Adder and Presentations

K-maps, design Half and Full Subtractor using K-maps ,

subtractor using Kmap. Lecture Using

BCD Adder and Subtractor (4-bit)

TLO 3.4 Describe working Chalk-Board

3.4 Encoder and Decoder: Functions of Encoder and

of specified Encoder and

Decoder, Block Diagram and Truth table, Priority Encoder

Decoder with help of block

(4:2, 8:3), BCD to 7 segment Decoder/Driver, Decimal to

diagram and truth table.

BCD encoder

TLO 3.5 Describe the

3.5 Multiplexer and Demultiplexer: Working, Truth table

working of Multiplexer

and applications of MUX and DEMUX. MUX tree,

and Demultiplexer.

DEMUX tree, DEMUX as Decoder

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

Theory Learning Suggested

Learning content mapped with Theory Learning

Sr.No Outcomes (TLO's)aligned Learning

Outcomes (TLO's) and CO's.

to CO's. Pedagogies.

TLO 4.1 Differentiate

between Latch and Flip

Flop.

TLO 4.2 Explain basic

memory cell and use

relevant triggering Unit - IV Sequential Logic Circuits

technique for the given 4.1 Difference between Combinational and Sequential

digital circuit. Logic circuits, Flips- Flops and Latch, Basic memory cell

TLO 4.3 Describe the truth ,RS-Latch using NAND and NOR, Triggering methods-

tables for the given Flip Edge trigger and Level Trigger

flops, applications of Flip 4.2 Flip-Flops: S-R, J-K, T and D, Truth table and logic

Video

flops. circuits of each flip-flop, Excitation table, applications

Demonstrations

TLO 4.4 Use the given 4.3 Race around condition in JK flip-flop, Master- Slave

4 Lecture Using

type of flip flop and its JK Flip Flop

Chalk-Board

excitation table to design 4.4 Shift registers- Serial In Serial Out, Serial In Parallel

Simulation

specific type of counter. Out, Parallel In Serial Out ,Parallel In Parallel Out,4-bit

TLO 4.5 Describe the universal shift register

working of specified shift 4.5 Counters- Synchronous and Asynchronous counters,

register with the help of Modulus of counter, Ripple counter, Ring Counter, Twisted

timing diagram. Ring Counter, Up – down counter, Decade Counter, MOD-

TLO 4.6 Design specified N counter, Timing Diagram

modulo-N counter using

Flip flops .

TLO 4.7 Design Ring

/Twisted ring counter using

given Flip-Flop.

TLO 5.1 Describe the

working of the given type Unit - V Data Converters and Memories

of DAC. 5.1 Digital to Analog Data Converter (DAC)- circuit

TLO 5.2 Calculate the diagram and working of Weighted resistor DAC and R-2R

output voltage for the Ladder DAC , DAC IC 0808

given digital input for 5.2 Analog to Digital Data Converter (ADC) : Block Video

specified DAC. Diagram, Types and Working of Dual Slope ADC, Demonstrations

5

TLO 5.3 Describe the Successive Approximation, Flash Type ADC, ADC IC Lecture Using

working of the given type 0808/09 specifications Chalk-Board

of ADC. 5.3 Memories: Organization, RAM ( SRAM, DRAM),

TLO 5.4 Compare working Volatile and Non-Volatile, ROM (PROM, EPROM,

of ROM,EPROM, EEPROM), Flash Memory, Comparison of RAM and

EEPROM and Flash ROM,EPROM and Flash Memory

Memory .

VI. LABORATORY LEARNING OUTCOME AND ALIGNED PRACTICAL / TUTORIAL EXPERIENCES.

Practical / Tutorial / Laboratory Sr Laboratory Experiment / Practical Titles / Number Relevant

Learning Outcome (LLO) No Tutorial Titles of hrs. COs

LLO 1.1 Test the functionality of

* Test the functionality of AND, OR, NOT, Ex-

basic gates.

1 OR and EX-NOR logic Gates using equivalent 2 CO2

LLO 1.2 Test the functionality of

74 series or CMOS Devices [CD] series.

special purpose gates.

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

Practical / Tutorial / Laboratory Sr Laboratory Experiment / Practical Titles / Number Relevant

Learning Outcome (LLO) No Tutorial Titles of hrs. COs

LLO 2.1 Test the functionality of

* Test the functionality of the given Universal

NAND and NOR gate of using 2 2 CO2

Gates using equivalent 74 series /CD series.

breadboard.

LLO 3.1 Test the functionality of the

constructed Basic gates using 3 * Construct Basic Gates using Universal Gates. 2 CO2

universal gates.

LLO 4.1 Construct Ex-OR, EX- Construct Exclusive Gates using Universal

4 2 CO2

NOR gates using universal gates. Gates.

LLO 5.1 Build the logic circuit on

breadboard to verify the De - 5 * Verify De-Morgan's Theorem (1 and 2). 2 CO2

Morgan's theorems.

LLO 6.1 Verify the truth table of

Half and Full adder circuits for the 6 * Implement 2 input, 3 input Adder Circuit. 2 CO3

given input.

LLO 7.1 Verify the truth table of

Half and Full subtractor using 7 Implement 2 input, 3 input Subtractor Circuit. 2 CO3

Boolean expressions.

LLO 8.1 Construct and test BCD to Test the output of BCD to 7 Segment Decoder

8 2 CO3

7 segment using Digital IC. using Digital IC for the given inputs.

LLO 9.1 Build/Test 2 or 4 bit

Check the output of comparator circuit consists

Magnitude comparator using Digital 9 2 CO3

of Digital IC.

IC.

LLO 10.1 Build / test function of * Build and test the functionality of 4:1/8:1

10 2 CO3

MUX Digital IC. Multiplexer.

LLO 11.1 Build / test function of Build and test the functionality of 1:4/1:8 De-

11 2 CO3

DEMUX Digital IC. Multiplexer.

LLO 12.1 Test functionality of RS Implement and verify the truth table of RS Flip

12 2 CO4

flip flop using NAND Gate . flop.

LLO 13.1 Test functionality of

Implement and test the functionality of master

Master Slave (MS) JK flip-flop 13 2 CO4

slave- JK Flip Flop using Digital IC.

using Digital IC.

LLO 14.1 Test functionality and Use Digital IC to construct and test the

14 2 CO4

truth table for D and T Flip flop. functionality of D and T flip flop.

LLO 15.1 Interpret timing diagram Build 4- bit Universal Shift register and observe

15 2 CO4

of 4 bit Universal Shift Register. the timing diagram.

LLO 16.1 Interpret timing diagram

of 4-bit ripple counter using Digital 16 Implement Ripple Counter using Digital IC. 2 CO4

IC.

LLO 17.1 Interpret timing diagram

17 * Implement Decade Counter Using Digital IC. 2 CO4

of Decade counter (Mod-10).

LLO 18.1 Build R-2R resistive

* Test the output of given R-2R type Digital to

network on breadboard to convert 18 2 CO5

Analog Converter for the given input.

given digital data into analog.

Note : Out of above suggestive LLOs -

'*' Marked Practicals (LLOs) Are mandatory.

Minimum 80% of above list of lab experiment are to be performed.

Judicial mix of LLOs are to be performed to achieve desired outcomes.

VII. SUGGESTED MICRO PROJECT / ASSIGNMENT/ ACTIVITIES FOR SPECIFIC LEARNING /

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

SKILLS DEVELOPMENT (SELF LEARNING)

Micro project

Implement 1:8 DEMUX using 1:4 /1:2 DE-MUX.

Build a circuit to implement 4 Bit adder.

Build a 4bit parity generator and parity tester.

Implement 16:1 MUX using 8:1/4:1 MUX.

Build a circuit to test 7 bit segment display.

Build a LED display bar.

Develop a project on Burglar alarm.

Light Detector circuit using NAND gate.

Note :

Above is just a suggestive list of microprojects and assignments; faculty must prepare their own bank of

microprojects, assignments, and activities in a similar way.

The faculty must allocate judicial mix of tasks, considering the weaknesses and / strengths of the student in

acquiring the desired skills.

If a microproject is assigned, it is expected to be completed as a group activity.

SLA marks shall be awarded as per the continuous assessment record.

If the course does not have associated SLA component, above suggestive listings is applicable to Tutorials

and maybe considered for FA-PR evaluations.

VIII. LABORATORY EQUIPMENT / INSTRUMENTS / TOOLS / SOFTWARE REQUIRED

Relevant

Sr.No Equipment Name with Broad Specifications LLO

Number

Digital Storage Oscilloscope

25MHz/60MHz/70MHz/100MHz Dual Channel, 4 Trace CRT / TFT based X10 magnification

1 20 nS max sweep rate, Alternate triggering Component tester and with optional features such 15,16,17

as Digital Read out, USB interface. Any other Oscilloscope with additional features is also

suitable with magnifying probe at least two probes, if possible isolated probe

Trainer kit for 4 bit Counter using Flip Flops

4 bit ripple counter synchronous counter IC 7476 based circuit, Input given by switches and

2 16,17

output indicated on LED, Facility to select MOD 8 or MOD 16 mode, Built in DC power

supply and manual pulser with indicator

Trainer kit IC DAC IC 0800

Trainer based on IC 0800, 8 bit digital input selected by switches and provision for

3 18

measurement of analog output. Facility to study effect of change in reference voltage, Built in

buffer amplifier, Built in DC power supply

Digital multimeter

4 All

3.5 digit with R , V, I measurements, diode and BJT testing

Digital IC Tester

5 All

Tests a wide range of Analog and Digital ICs such as 74 series /CD series

Bread Board Development System

Bread Board system with DC power output 5V,+/-12V and 0-5V variable , digital voltmeter

6 All

,ammeter , LED indicators 8 no , logic input switches 8 no, 7 segment display 2 no,

clockgenerator

Trainer kits for digital ICs

7 Trainer kit should consists of digital ICs for logic gates, flop flop, shift registers, counter All

alongwith toggle switches for inputs and bi-colourLED at outputs, built in power supply

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

IX. SUGGESTED WEIGHTAGE TO LEARNING EFFORTS & ASSESSMENT PURPOSE (Specification

Table)

Aligned Learning R- U- A- Total

Sr.No Unit Unit Title

COs Hours Level Level Level Marks

1 I Number Systems CO1 5 2 4 2 8

Logic Gates and Boolean

2 II CO2 8 2 4 6 12

Algebra

3 III Combinational Logic Circuits CO3 12 4 6 8 18

4 IV Sequential Logic Circuits CO4 14 4 6 8 18

5 V Data Converters and Memories CO5 6 4 6 4 14

Grand Total 45 16 26 28 70

X. ASSESSMENT METHODOLOGIES/TOOLS

Formative assessment (Assessment for Learning)

Two offline unit tests of 30 marks and average of two unit test marks will be consider for out of 30 marks.

Each practical will be assessed considering 60% weightage to process, 40% weightage to product.

For formative assessment of laboratory learning 25 marks

Summative Assessment (Assessment of Learning)

End semester assessment is of 70 marks.

End semester summative assessment of 25 marks for laboratory learning

XI. SUGGESTED COS - POS MATRIX FORM

Programme

Specific

Programme Outcomes (POs)

Outcomes*

(PSOs)

Course PO-5

Outcomes PO-1 Basic Engineering

(COs) PO-3 PO-7

and PO-2 PO-4 Practices for

Design/ PO-6 Project Life PSO- PSO- PSO-

Discipline Problem Engineering Society,

Development Management Long 1 2 3

Specific Analysis Tools Sustainability

of Solutions Learning

Knowledge and

Environment

CO1 2 - 1 - - - 3

CO2 2 - 2 - - - 2

CO3 3 2 3 2 - 1 2

CO4 3 2 3 2 - 1 2

CO5 2 - 2 2 1 1 2

Legends :- High:03, Medium:02,Low:01, No Mapping: -

*PSOs are to be formulated at institute level

XII. SUGGESTED LEARNING MATERIALS / BOOKS

Sr.No Author Title Publisher with ISBN Number

McGraw-Hill Publishing, New Delhi,2009

1 Jain R.P Modern Digital Electronics

ISBN:9780070669116

MSBTE Approval Dt. Semester - 3, K Scheme

DIGITAL TECHNIQUES Course Code : 313307

Sr.No Author Title Publisher with ISBN Number

PHI learning Private limited, ISBN:978-81-

2 Anand Kumar Fundamentals of Digital Circuits

203-5268-1

Salivahanan S, Vikas Publishing House, New Delhi,2013

3 Digital Circuits and Design

Arivazhagan S. ISBN: 9789325960411

McGraw-Hill Publishing, New Delhi,2016

4 Puri.V.K Digital Electronics

ISBN:97800746331751

Malvino A.P Donald McGraw-Hill Education, New Delhi

5 Digital Principles

.P. Leach ISBN:9789339203405

Digital Electronics: Principles, Wiley India, Delhi, 2007,

6 Anil.K.Maini

Devices and Applications ISBN:9780470032145

Pearson Education India, Delhi

7 Floyd, Thomas Digital Fundamentals

2014,ISBN:9780132737968

Publisher: Oxford University Press, ISBN:

8 G.K.Kharate Digital Electronics

9780198061830

XIII . LEARNING WEBSITES & PORTALS

Sr.No Link / Portal Description

1 https://studytronics.weebly.com/digital-electronics.html Basics of Digital Electronics

Introduction To Digital Number System &

2 https://www.udemy.com/course/basics-of-digital-techniques/

Logic Gates

Boolean Algebra and Logic Gates,

https://www.geeksforgeeks.org/synchronous-sequential-circuit

3 Combinational and Sequential Logic

s-in-digital-logic/

Circuits

4 https://onlinecourses.nptel.ac.in/noc19_ee51/preview Digital Circuits

5 https://de-iitr.vlabs.ac.in/ Virtual Labs for Digital Systems

https://www.tutorialspoint.com/digital_circuits/digital_circ

6 Sequential Circuits

uits_sequential_circuits.htm

Note :

Teachers are requested to check the creative common license status/financial implications of the suggested

online educational resources before use by the students

MSBTE Approval Dt. Semester - 3, K Scheme

You might also like

- PLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingFrom EverandPLC Controls with Structured Text (ST): IEC 61131-3 and best practice ST programmingRating: 4 out of 5 stars4/5 (11)

- Project Proposal of FM ReceiverDocument4 pagesProject Proposal of FM ReceiverAta Ur Rahman KhalidNo ratings yet

- Database Management System 1Document7 pagesDatabase Management System 1pooja herwadeNo ratings yet

- 311302-Basic Maths SyllabusDocument9 pages311302-Basic Maths SyllabusSuriRawatNo ratings yet

- 311001-Fundamentals of Ict SyllabusDocument10 pages311001-Fundamentals of Ict SyllabusSuriRawatNo ratings yet

- 311302-BASIC MATHEMATICS (K-Scheme-Syllabus)Document8 pages311302-BASIC MATHEMATICS (K-Scheme-Syllabus)jacksparrowcom4No ratings yet

- Applied MathematicsDocument7 pagesApplied Mathematics24Vaishnavi KhambayateNo ratings yet

- 311305-Basic Science SyllabusDocument12 pages311305-Basic Science SyllabusSuriRawatNo ratings yet

- Applied Mathematics (K Scheme Syllabus)Document6 pagesApplied Mathematics (K Scheme Syllabus)pagareaaryan.2007No ratings yet

- 312009-Programming in 'C' Language - 240109 - 232135Document9 pages312009-Programming in 'C' Language - 240109 - 232135dhanu2399No ratings yet

- 312009-Programming in 'C' LanguageDocument8 pages312009-Programming in 'C' LanguageTushar RathodNo ratings yet

- 312303-Programming in C 271223Document8 pages312303-Programming in C 271223ts6071270No ratings yet

- MathDocument6 pagesMathjsa62uqNo ratings yet

- Programming INC PIC AEC 4 1 4 1 10 5 3 30 70 100 40 50 20 50# 20 25 10 225Document8 pagesProgramming INC PIC AEC 4 1 4 1 10 5 3 30 70 100 40 50 20 50# 20 25 10 225punnyaiys20compNo ratings yet

- 311305-Basic Science 210923Document18 pages311305-Basic Science 210923theboyaman22No ratings yet

- 311302-Basic Mathematics Syllabus BMS MsbtepdfDocument9 pages311302-Basic Mathematics Syllabus BMS Msbtepdf2250 Mustak ShaikhNo ratings yet

- Engg GraphicsDocument7 pagesEngg GraphicskirankumarNo ratings yet

- 312001-LINUX BASICS(syllabus)Document9 pages312001-LINUX BASICS(syllabus)vasundhara grpNo ratings yet

- 313301-Data Structure Using cDocument6 pages313301-Data Structure Using catharv.ghadigaonkar287No ratings yet

- Object Oriented Programming Using CDocument8 pagesObject Oriented Programming Using Cpooja herwadeNo ratings yet

- Data Structure Using C 1Document6 pagesData Structure Using C 1pooja herwadeNo ratings yet

- 311302-Basic Mathematics 210923Document14 pages311302-Basic Mathematics 210923Pooja GhanghavNo ratings yet

- Linux BasicsDocument7 pagesLinux BasicsHarshal MakodeNo ratings yet

- 313304-Object Oriented Programming Using c++Document7 pages313304-Object Oriented Programming Using c++atharv.ghadigaonkar287No ratings yet

- MATHEMATICSDocument6 pagesMATHEMATICSmohitniks1648No ratings yet

- 312002-Professional Communication 271223Document6 pages312002-Professional Communication 271223Kishor BhitadeNo ratings yet

- 312309-Elements of Electronics 281223Document9 pages312309-Elements of Electronics 281223suyashbadgujar2008No ratings yet

- 313022-Computer Aided DraftingDocument7 pages313022-Computer Aided DraftingklkanphadeNo ratings yet

- 311006-Engineering GraphicsDocument7 pages311006-Engineering Graphicsvallabhdongare1209No ratings yet

- 312301-Applied Mathematics 271223Document7 pages312301-Applied Mathematics 271223yashraj shindeNo ratings yet

- Basic ScienceDocument9 pagesBasic SciencekirankumarNo ratings yet

- Basic MathematicsDocument7 pagesBasic MathematicskirankumarNo ratings yet

- Electronic Materials ComponentsDocument8 pagesElectronic Materials ComponentsgpkpaperNo ratings yet

- Basic Science K Scheme PDFDocument10 pagesBasic Science K Scheme PDFvdvikram066No ratings yet

- 311303-Communication Skills (English) SyllabusDocument7 pages311303-Communication Skills (English) SyllabusSuriRawatNo ratings yet

- 313351 Thermal EngineeringDocument7 pages313351 Thermal EngineeringklkanphadeNo ratings yet

- Engineering GraphicsDocument6 pagesEngineering Graphicsvp4455820No ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document3 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Deepti MishraNo ratings yet

- 312003-Social and Life SkillsDocument10 pages312003-Social and Life Skillsdreamdose2906No ratings yet

- Don Bosco Institute of Technology: Course Syllabi With CO'sDocument2 pagesDon Bosco Institute of Technology: Course Syllabi With CO'sprashantgeminiNo ratings yet

- Manufacturing TechnologyDocument7 pagesManufacturing Technologytrinkle saindaneNo ratings yet

- Dr. MPS Memorial College of Business Studies, Agra (Department of IT)Document528 pagesDr. MPS Memorial College of Business Studies, Agra (Department of IT)Anupma MalhotraNo ratings yet

- Syllabus - Electrical Sem 4Document81 pagesSyllabus - Electrical Sem 4vcb.polykondagaonNo ratings yet

- 641 D 526409739 DSPLab OutlineDocument4 pages641 D 526409739 DSPLab OutlineTayyaba ParveenNo ratings yet

- 4th Sem NotesDocument18 pages4th Sem NotesyashNo ratings yet

- Course Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Document10 pagesCourse Description Form (CDF) Digital Signal Processing EEE324 - Updated 4Huzaifa YasirNo ratings yet

- III Year 2nd Semester Syllabus2022Document17 pagesIII Year 2nd Semester Syllabus2022Ecell FarewellNo ratings yet

- Fundamental of Electrical EngineeringDocument9 pagesFundamental of Electrical Engineeringsujitvarekar03No ratings yet

- 313346 Production DrawingDocument6 pages313346 Production DrawingklkanphadeNo ratings yet

- Diploma IT 3rd Sem SylDocument20 pagesDiploma IT 3rd Sem Sylshriram1082883No ratings yet

- c1 Scsr2043 Operating Systems Course OutlineDocument7 pagesc1 Scsr2043 Operating Systems Course OutlineError 404No ratings yet

- Digital Electronics and Computer OrganizationDocument3 pagesDigital Electronics and Computer OrganizationSai Prajwal SavanamNo ratings yet

- Syllabus Copy For StudentsDocument2 pagesSyllabus Copy For StudentsAcomplishing DreamsNo ratings yet

- 312308-Applied Science-1Document10 pages312308-Applied Science-1Rohini AdaskarNo ratings yet

- SignalsyllDocument107 pagesSignalsyllManikya MakshiNo ratings yet

- EE 320 (CS 320) - Computer Organization and Assembly - Jahangir IkramDocument4 pagesEE 320 (CS 320) - Computer Organization and Assembly - Jahangir IkramSheikh AsherNo ratings yet

- Bcse2370 DCN LabDocument27 pagesBcse2370 DCN LabJATIN KUMAR SHARMA 22SCSE1012203No ratings yet

- Galgotias University, Greater Noida FALL Semester 2017-2018 Course HandoutDocument3 pagesGalgotias University, Greater Noida FALL Semester 2017-2018 Course HandoutLiNuNo ratings yet

- Lab Manual - Data MiningDocument26 pagesLab Manual - Data Miningroymegha454No ratings yet

- S YBTechComputer Engg - SyllabusDocument31 pagesS YBTechComputer Engg - SyllabusRushabh Patel0% (1)

- PRA2.NETDocument3 pagesPRA2.NETseemakasture75No ratings yet

- Oops ProgramsDocument100 pagesOops Programsseemakasture75No ratings yet

- JAVA PRACTICAL PROGRAMSDocument57 pagesJAVA PRACTICAL PROGRAMSseemakasture75No ratings yet

- rpaDocument10 pagesrpaseemakasture75No ratings yet

- ROBOTIC PROCESS1Document14 pagesROBOTIC PROCESS1seemakasture75No ratings yet

- 17. Quality Management SystemDocument63 pages17. Quality Management Systemseemakasture75No ratings yet

- Dmaic and Approach of Six SigmaDocument4 pagesDmaic and Approach of Six Sigmaseemakasture75No ratings yet

- Skills BuildDocument1 pageSkills Buildseemakasture75No ratings yet

- Robotic Process AutomationDocument9 pagesRobotic Process Automationseemakasture75No ratings yet

- Passive Voice - 2Document1 pagePassive Voice - 2seemakasture75No ratings yet

- Mic Paper Solution 22Document17 pagesMic Paper Solution 22seemakasture75No ratings yet

- DCC PIP On Chapter 3Document10 pagesDCC PIP On Chapter 3seemakasture75No ratings yet

- JPR S 22Document26 pagesJPR S 22seemakasture75No ratings yet

- Poem AppreciationDocument3 pagesPoem Appreciationseemakasture75No ratings yet

- MIC Assginment 3 SolutionDocument5 pagesMIC Assginment 3 Solutionseemakasture75No ratings yet

- RMMMDocument2 pagesRMMMseemakasture75No ratings yet

- JPR Notes 6.managing Input Output Files in Java 1Document19 pagesJPR Notes 6.managing Input Output Files in Java 1seemakasture75No ratings yet

- DCC PIP 4th UnitDocument11 pagesDCC PIP 4th Unitseemakasture75No ratings yet

- DCC PIP On Chapter 1Document10 pagesDCC PIP On Chapter 1seemakasture75No ratings yet

- DCC Chapter2 CompressedDocument31 pagesDCC Chapter2 Compressedseemakasture75No ratings yet

- DCC PIP 2nd UnitDocument9 pagesDCC PIP 2nd Unitseemakasture75No ratings yet

- Ec2203-Digital Electronics Question BankDocument22 pagesEc2203-Digital Electronics Question BankRamadhuraiNo ratings yet

- This Experiment Is Individual!Document5 pagesThis Experiment Is Individual!Rachel MonesNo ratings yet

- UTC317/B/TB Linear Integrated Circuit: Youwang Electronics Co - LTDDocument9 pagesUTC317/B/TB Linear Integrated Circuit: Youwang Electronics Co - LTDAlexisNo ratings yet

- APLAB LTD. Rhino UPSDocument2 pagesAPLAB LTD. Rhino UPSTanmoy AcharyaNo ratings yet

- PHASAR-Based WDM-Devices: Principles, Design and ApplicationsDocument15 pagesPHASAR-Based WDM-Devices: Principles, Design and ApplicationsPedro SgNo ratings yet

- Cired2015 0104Document6 pagesCired2015 0104Brajan's B.No ratings yet

- XP Communication - Eng - V2.2 PDFDocument318 pagesXP Communication - Eng - V2.2 PDFRZNo ratings yet

- Physical Layer Deep Learning of Encodings For The MIMO Fading ChannelDocument5 pagesPhysical Layer Deep Learning of Encodings For The MIMO Fading Channeljun zhaoNo ratings yet

- Microprocessor ComponentsDocument2 pagesMicroprocessor ComponentsBryan YaranonNo ratings yet

- General Power Quality IssueDocument3 pagesGeneral Power Quality IssueRizwan 106No ratings yet

- AQUASCOPE3Document4 pagesAQUASCOPE3Jose Rino De MattaNo ratings yet

- ITC Imp QuesDocument8 pagesITC Imp QuesjormnNo ratings yet

- 3000/01 Chassis Processor: Technical ManualDocument19 pages3000/01 Chassis Processor: Technical ManualJoaquín LunaNo ratings yet

- Cisco 800Document144 pagesCisco 800la_leon2275No ratings yet

- 信號與系統Chap. 3 Class NotesDocument46 pages信號與系統Chap. 3 Class NoteswangliNo ratings yet

- Pre de EmphasisDocument3 pagesPre de Emphasisashis nayakNo ratings yet

- Harmonic Quality in Naval ShipsDocument6 pagesHarmonic Quality in Naval Shipstkdrt2166No ratings yet

- AD9951 AppnoteDocument6 pagesAD9951 Appnoteshabaz_yousaf2734No ratings yet

- Transformer Phasor DiagramDocument21 pagesTransformer Phasor DiagramblbmalekNo ratings yet

- M Tender 514Document5 pagesM Tender 514gbaludbNo ratings yet

- USB 2.0 Connect Timing ECNDocument5 pagesUSB 2.0 Connect Timing ECNmpm proiectareNo ratings yet

- TrimbleR10 Quick Ref ENGDocument10 pagesTrimbleR10 Quick Ref ENGkamalsayedNo ratings yet

- FDFS2P102: Integrated P-Channel MOSFET and Schottky DiodeDocument5 pagesFDFS2P102: Integrated P-Channel MOSFET and Schottky DiodeManuel LeaNo ratings yet

- Schneider Electric - Acti9-iSPN-Vigi - A9D73610Document3 pagesSchneider Electric - Acti9-iSPN-Vigi - A9D73610Suministros VariosNo ratings yet

- 2.25. - SCR-SCRF Battery SaftDocument68 pages2.25. - SCR-SCRF Battery Saftgenial72No ratings yet

- Catalogo Novik NeoDocument32 pagesCatalogo Novik NeorafaelciceliniNo ratings yet

- Report On Hall Effect TransducersDocument7 pagesReport On Hall Effect TransducersChris Balmaceda0% (1)

- Samsung LN40C650L1FXZA Fast Track Guide (SM) SchematicDocument4 pagesSamsung LN40C650L1FXZA Fast Track Guide (SM) SchematicRich RodNo ratings yet

- EC1313 Two Marks Linear Integrated CircuitsDocument11 pagesEC1313 Two Marks Linear Integrated Circuitsmoney_kandan2004No ratings yet