Professional Documents

Culture Documents

stgap2sics

stgap2sics

Uploaded by

Kantesh KudapaliCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

stgap2sics

stgap2sics

Uploaded by

Kantesh KudapaliCopyright:

Available Formats

STGAP2SICS

Datasheet

Galvanically isolated 4 A single gate driver for SiC MOSFETs

Features

• High voltage rail up to 1200 V

• Driver current capability: 4 A sink/source @25°C

• dV/dt transient immunity ±100 V/ns in full temperature range

• Overall input-output propagation delay: 75 ns

• Separate sink and source option for easy gate driving configuration

• 4 A Miller CLAMP dedicated pin option

• UVLO function

• Gate driving voltage up to 26 V

• 3.3 V, 5 V TTL/CMOS inputs with hysteresis

• Temperature shut-down protection

• Standby function

• 6 kV galvanic isolation

Product status link • Wide body SO-8W package

• UL 1577 recognized

STGAP2SICS

Description

Product label

The STGAP2SICS is a single gate driver which provides galvanic isolation between

the gate driving channel and the low voltage control and interface circuitry.

The gate driver is characterized by 4 A capability and rail-to-rail outputs, making the

device also suitable for mid and high power applications such as power conversion

and motor driver inverters in industrial applications. The device is available in

two different configurations. The configuration with separated output pins allows

to independently optimize turn-on and turn-off by using dedicated gate resistors.

The configuration featuring single output pin and Miller CLAMP function prevents

gate spikes during fast commutations in half-bridge topologies. Both configurations

provide high flexibility and bill of material reduction for external components.

The device integrates protection functions: UVLO with optimized value for SiC

MOSFETs and thermal shut down are included to facilitate the design of highly

reliable systems. Dual input pins allow the selection of signal polarity control and

implementation of HW interlocking protection to avoid cross-conduction in case of

controller malfunction. The input to output propagation delay is less than 75 ns, which

delivers high PWM control accuracy. A standby mode is available to reduce idle

power consumption.

DS13402 - Rev 4 - September 2022 www.st.com

For further information contact your local STMicroelectronics sales office.

STGAP2SICS

Block diagram

1 Block diagram

Figure 1. Block diagram - Single output and Miller Clamp configuration

VDD VH

I

S UVLO

IN+ VH

O Floating Level

GOUT

Control L Section

Control

Shifter

A

Logic T

Logic

CLAMP

IN- I

O

N GNDISO

Floating ground A +

GND

VCLAMPth

Figure 2. Block diagram - Separate output configuration

VDD VH

I

S UVLO

IN+ VH

O Floating Level

GON

Control L Section

Control

Shifter

A

Logic T

Logic

GOFF

IN- I

O

N GNDISO

Floating ground

GND

DS13402 - Rev 4 page 2/22

STGAP2SICS

Pin description and connection diagram

2 Pin description and connection diagram

Figure 3. Pin connection (top view) - Single output and Miller CLAMP option

VDD 1 8 GNDISO

IN+ 2 7 CLAMP

IN- 3 6 GOUT

GND 4 5 VH

Figure 4. Pin connection (top view) - Separated outputs option

VDD 1 8 GNDISO

IN+ 2 7 GOFF

IN- 3 6 GON

GND 4 5 VH

Table 1. Pin Description

Pin #

Pin Name Type Function

Figure 4 Figure 3

1 1 VDD Power Supply Driver logic supply voltage.

2 2 IN+ Logic Input Driver logic input, active high.

3 3 IN- Logic Input Driver logic input, active low.

4 4 GND Power Supply Driver logic ground.

5 5 VH Power Supply Gate driving positive voltage supply.

- 6 GOUT Analog Output Sink/Source output.

- 7 CLAMP Analog Output Active Miller Clamp.

6 - GON Analog Output Source output.

7 - GOFF Analog Output Sink output.

8 8 GNDISO Power Supply Gate driving Isolated ground.

DS13402 - Rev 4 page 3/22

STGAP2SICS

Electrical data

3 Electrical data

3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

Test

Symbol Parameter Min. Max. Unit

condition

VDD Logic supply voltage vs. GND - -0.3 6.5 V

VLOGIC Logic pins voltage vs. GND - -0.3 6.5 V

VH Positive supply voltage (VH vs. GNDISO) - -0.3 28 V

VOUT Voltage on gate driver outputs (GON, GOFF, CLAMP VS. GNDISO) - -0.3 VH+0.3 V

TJ Junction temperature - -40 150 °C

TS Storage temperature - -50 150 °C

ESD HBM (human body model) - 2 kV

3.2 Thermal data

Table 3. Thermal data

Symbol Parameter Package Value Unit

Rth(JA) Thermal resistance junction to ambient SO-8W 120 °C/W

3.3 Recommended operating conditions

Table 4. Recommended operating conditions

Symbol Parameter Test conditions Min. Max. Unit

VDD Logic supply voltage vs. GND - 3.1 5.5 V

VLOGIC Logic pins voltage vs. GND - 0 5.5 V

VH Positive supply voltage (VH vs. GNDISO) - Max(VHON) 26 V

FSW Maximum switching frequency(1) - - 1 MHz

tOUT Output pulse width (GOUT, GON-GOFF) - 100 - ns

TJ Operating Junction Temperature - -40 125 °C

1. Actual limit depends on power dissipation and TJ.

DS13402 - Rev 4 page 4/22

STGAP2SICS

Electrical characteristics

4 Electrical characteristics

Table 5. Electrical characteristics (TJ = 25°C, VH = 18 V, VDD = 5 V unless otherwise specified)

Symbol Pin Parameter Test conditions Min. Typ. Max. Unit

Dynamic characteristics

Input to output propagation

tDon IN+, IN- - 50 75 90 ns

delay ON

Input to output propagation

tDoff IN+, IN- - 50 75 90 ns

delay OFF

tr - Rise time CL = 4.7 nF - 30 - ns

tf - Fall time See Figure 12 - 30 - ns

Pulse Width Distortion

PWD - - - - 20 ns

|tDon-tDoff|

tdeglitch IN+, IN- Inputs deglitch filter - - 20 40 ns

Common-mode transient VCM = 1500 V,

CMTI (1) - 100 - - V/ns

immunity, |dVISO/dt| See Figure 13

Supply voltage

VHon - VH UVLO turn-on threshold - 14.6 15.5 16.4 V

VHoff - VH UVLO turn-off threshold - 13.9 14.8 15.7 V

VHhyst - VH UVLO hysteresis - 600 750 950 mV

VH undervoltage quiescent

IQHU - VH = 7V - 1.3 1.8 mA

supply current

IQH - VH quiescent supply current - - 1.3 1.8 mA

Standby VH quiescent supply

IQHSBY - Standby mode - 400 550 µA

current

IGOFF = 0.2 A;

SafeClp - GOFF active clamp - 2 2.3 V

VH floating

IQDD - VDD quiescent supply current - - 1.0 1.3 mA

Standby VDD quiescent

IQDDSBY - Standby mode - 40 65 µA

supply current

Logic Inputs

Low level logic threshold

Vil IN+, IN- - 0.29·VDD 0.33·VDD 0.37·VDD V

voltage

High level logic threshold

Vih IN+, IN- - 0.62·VDD 0.66·VDD 0.70·VDD V

voltage

IINh IN+, IN- INx logic “1” input bias current INx = 5 V 33 50 70 µA

IINl IN+, IN- INx logic “0” input bias current INx = GND - - 1 µA

Rpd IN+, IN- Inputs pull-down resistors INx = 5 V 70 100 150 kΩ

Driver buffer section

TJ = 25°C - 4 - A

IGON - Source short circuit current TJ = -40 to +125°C

(1)

3 - 5 A

Source output high level

VGONH - IGON = 100 mA VH-0.15 VH-0.125 - V

voltage

DS13402 - Rev 4 page 5/22

STGAP2SICS

Electrical characteristics

Symbol Pin Parameter Test conditions Min. Typ. Max. Unit

RGON - Source RDS_ON IGON = 100 mA - 1.25 1.5 Ω

TJ = 25°C - 4 -

IGOFF - Sink short-circuit current TJ = -40 to +125°C A

(1)

3 - 5.5

VGOFFL - Sink output low level voltage IGOFF = 100 mA - 100 120 mV

RGOFF - Sink RDS_ON IGOFF = 100 mA - 1.0 1.2 Ω

Miller Clamp

VCLAMPth - CLAMP voltage threshold VCLAMP vs.GNDISO 1.3 2 2.6 V

VCLAMP = 15V

TJ = 25°C - 4 -

ICLAMP - CLAMP short-circuit current A

TJ = -40 to +125°C

(1)

2 - 5

CLAMP low level output

VCLAMP_L - ICLAMP = 100mA - 96 115 mV

voltage

RCLAMP - CLAMP RDS_ON ICLAMP = 100mA - 0.96 1.15 Ω

Over-temperature protection

TSD - Shutdown temperature - 170 - - °C

Thys - Temperature hysteresis - - 20 - °C

Standby

tSTBY - Standby time See Control inputs 200 280 500 µs

tWUP - Wake-up time See Control inputs 10 20 35 µs

tawake - Wake-up delay See Control inputs 90 140 200 µs

tstbyfilt - Standby filter See Control inputs 200 280 800 ns

1. Characterization data, not tested in production.

DS13402 - Rev 4 page 6/22

STGAP2SICS

Isolation

5 Isolation

Table 6. Isolation and safety-related specifications

Parameter Symbol Value Unit Conditions

Clearance (Minimum External Air Measured from input terminals to output terminals,

CLR 8 mm

Gap) shortest distance through air

Creepage (*) Measured from input terminals to output terminals,

CPG 8 mm

(Minimum External Tracking) shortest distance path along body

Comparative Tracking

CTI ≥ 400 V DIN IEC 112/VDE 0303 Part 1

Index (Tracking Resistance)

Isolation Group - II - Material Group (DIN VDE 0110, 1/89, Table 1)

Table 7. Isolation characteristics

Parameter Symbol Test Conditions Characteristic Unit

Maximum Working Isolation Voltage VIORM - 1200 VPEAK

Method a, Type test

VPR = VIORM ×1.6, tm = 10 s 1920 VPEAK

Input to Output test voltage Partial discharge < 5 pC

VPR

In accordance with VDE 0884-11 Method b1, 100 % Production test

VPR = VIORM×1.875, tm = 1 s 2250 VPEAK

Partial discharge < 5 pC

Transient Overvoltage (Highest

VIOTM tini = 60 s Type test 6000 VPEAK

Allowable Overvoltage)

Maximum Surge TestVoltage VIOSM Type test 6000 VPEAK

Isolation Resistance RIO VIO = 500 V; Type test >109 Ω

Table 8. Isolation voltage as per UL 1577

Parameter Symbol Characteristic Unit

Isolation Withstand Voltage, 1min (Type test) VISO 3535/5000 VRMS/VPEAK

Isolation TestVoltage, 1sec (100% production) VISOtest 4242/6000 VRMS/VPEAK

Recognized under the UL 1577 Component Recognition Program - file number E362869

DS13402 - Rev 4 page 7/22

STGAP2SICS

Functional description

6 Functional description

6.1 Gate driving power supply and UVLO

The STGAP2SiCS is a flexible and compact gate driver with 4 A output current and rail-to-rail outputs. The device

allows implementation of either unipolar or bipolar gate driving.

Figure 5. Power supply configuration for unipolar and bipolar gate driving

Unipolar gate driving Bipolar gate driving

VDD VDD

VDD VDD

1uF 100nF 1uF 100nF

VH VH

IN+ I 100nF 1uF

+ IN+ I 100nF 1uF +

S VH S VH

O GON O GON

L L

IN- A IN- A

T GOFF T GOFF

I

I

O O 1uF +

N N VL

GND GNDISO GND GNDISO

Undervoltage protection is available on VH supply pin. A fixed hysteresis sets the turn-off threshold, thus avoiding

intermittent operation.

When VH voltage falls below the VHoff threshold, the output buffer enters a “safe state”. When VH voltage

reaches the VHon threshold, the device returns to normal operation and sets the output according to actual input

pins status.

The VDD and VH supply pins must be properly filtered with local bypass capacitors. The use of capacitors with

different values in parallel provides both local storage for impulsive current supply and high-frequency filtering.

The best filtering is obtained by using low-ESR SMT ceramic capacitors and are therefore recommended. A 100

nF ceramic capacitor must be placed as close as possible to each supply pin, and a second bypass capacitor with

value in the range between 1 µF and 10 µF should be placed close to it.

6.2 Power-up, power-down and “safe state”

The following conditions define the “safe state”:

• GOFF = ON state;

• GON = High Impedance;

• CLAMP = ON state (for STGAP2SiCSC);

Such conditions are maintained at power-up of the isolated side (VH < VHon) and during whole device power

down phase (VH < VHoff), regardless of the value of the input pins.

The device integrates a structure which clamps the driver output to a voltage not higher than SafeClp when VH

voltage is not high enough to actively turn the internal GOFF MOSFET on. If VH positive supply pin is floating or

not supplied the GOFF pin is therefore clamped to a voltage smaller than SafeClp.

If the supply voltage VDD of the control section of the device is not supplied, the output is put in safe state, and

remains in such condition until the VDD voltage returns within operative conditions.

After power-up of both isolated and low voltage sides, the device output state depends on the status of the input

pins.

DS13402 - Rev 4 page 8/22

STGAP2SICS

Control inputs

6.3 Control inputs

The device is controlled through the IN+ and IN- logic inputs, in accordance with the truth table below.

Table 9. Inputs truth table (applicable when device is not in UVLO or "safe state")

Input pins Output pins

IN+ IN- GON GOFF

L L OFF ON

H L ON OFF

L H OFF ON

H H OFF ON

A deglitch filter allows input signals with duration shorter than tdeglitch to be ignored, thereby preventing noise

spikes potentially present in the application from generating unwanted commutations.

6.4 Miller Clamp function

The Miller clamp function allows the control of the Miller current during the power stage switching in half-bridge

configurations. When the external power transistor is in the OFF state, the driver operates to avoid the induced

turn-on phenomenon that may occur when the other switch in the same leg is being turned on, due to the CGD

capacitance.

During the turn-off period the gate of the external switch is monitored through the CLAMP pin. The CLAMP switch

is activated when gate voltage goes below the voltage threshold, VCLAMPth, thus creating a low impedance path

between the switch gate and the GNDISO pin.

6.5 Watchdog

The isolated HV side has a watchdog function in order to identify when it is not able to communicate with LV side,

for example because the VDD of the LV side is not supplied. In this case the output of the driver is forced in “safe

state” until communication link is properly established again.

6.6 Thermal shutdown protection

The device provides a thermal shutdown protection. When junction temperature reaches the TSD temperature

threshold, the device is forced in “safe state”. The device operation is restored as soon as the junction

temperature is lower than TSD-Thys.

DS13402 - Rev 4 page 9/22

STGAP2SICS

Standby function

6.7 Standby function

In order to reduce the power consumption of both control interface and gate driving sides the device can be put in

standby mode. In standby mode the quiescent current from VDD and VH supply pins is reduced to IQDDSBY and

IQHSBY respectively, and the output remains in “safe state” (the output is actively forced low).

The way to enter standby is to keep both IN+ and IN- high (“standby” value) for a time longer than tSTBY. During

stand-by the inputs can change from the “standby” value.

To exit stand-by, IN+ and IN- must be put in any combination different from the “standby” value for a time longer

than tstbyfilt, and then in the “standby” value for a time t such that tWUP<t <tSTBY.

When the input configuration is changed from the “standby” value the output is enabled and set according to

inputs state after a time tawake.

Figure 6. Standby state sequences

Sequence to enter stand-by mode

“stand-by”: IN+ = IN- = HIGH

t < tSTBY t = tSTBY is any different combination

duration too short

IN+ & IN- “stand-by” “stand-by”

Device status ACTIVE STAND-BY

Output ACTIVE SAFE-STATE

Sequence to exit stand-by mode

t = tSTBY t > tstbyfilt t < tWUP t > tSTBY tWUP < t < tSTBY t = tawake

duration duration too long

too short

IN+ & IN- “stand-by” “stand-by” “stand-by” “stand-by”

Device status ACTIVE STAND-BY ACTIVE

Output ACTIVE SAFE-STATE ACTIVE

DS13402 - Rev 4 page 10/22

STGAP2SICS

Typical application diagram

7 Typical application diagram

Figure 7. Typical application diagram - Separated outputs

VDD

VDD HV_BUS

VH_HS

UVLO

VDD VH

IN+ I

R

C S

UVLO

O Level

VH

Shifter GON

Control L Floating

Section

IN- A

Logic T

Control

Logic

GOFF

VDD R

C I

O GND_HS

N Floating ground

GND GNDISO

HIN

VDD Load_ Phase

MCU LIN VDD

VH VH_LS

UVLO

VDD

IN+

I

R

C S

UVLO

O Level

VH

Shifter GON

Control L Floating

Section

IN- A

Logic T

Control

Logic

R GOFF

C I

O GND_LS

N Floating ground GNDISO

GND

GND_PWR

Figure 8. Typical application diagram - Separated outputs and negative gate driving

VDD

VDD HV_BUS

VH_HS

UVLO

VDD VH

IN+ I

+

R

C S VH

UVLO

O Level

VH

Shifter GON

Control L Floating

Section

IN- A

Logic T

Control

Logic

GOFF

VDD R

C I

O VL_HS

N Floating ground GND_HS

GND GNDISO

VL

+

HIN

VDD Load_ Phase

MCU LIN VDD

VH VH_LS

UVLO

VDD

IN+

I

+

R

C S VH

UVLO

O Level

VH

Shifter GON

Control L Floating

Section

IN- A

Logic T

Control

Logic

R GOFF

C I

O VL_LS

N Floating ground GNDISO GND_LS

GND

VL

+ GND_PWR

DS13402 - Rev 4 page 11/22

STGAP2SICS

Typical application diagram

Figure 9. Typical application diagram - Miller Clamp

VDD

VH_HS

VDD HV_BUS

VH

I

IN+ S UVLO

R VH

C O Floating Level

Control L Section

Control

Shifter

GOUT

A

IN- Logic T

Logic

I

VDD R

C

O

CLAMP

GND_HS

N

GND Floating ground A + GNDISO

VCLAMPth

HIN

VDD Load_ Phase

MCU LIN VDD

VH_LS

VH

I

IN+ S UVLO

R VH

C O Floating Level

Control L Section

Control

Shifter

GOUT

A

IN- Logic T

Logic

R I CLAMP

C

O

GND_LS

N

Floating ground A + GNDISO

GND

VCLAMPth GND_PWR

Figure 10. Typical application diagram - Miller Clamp and negative gate driving

VDD

VDD HV_BUS

VH_HS

VH

I

IN+ S UVLO +

R VH VH

C O Floating Level GOUT

Control L Section

Control

Shifter

A

IN- Logic T

Logic

I CLAMP

VDD R

C

O

VL_HS

N

Floating ground A + GNDISO GND_HS

GND

VCLAMPth VL

+

HIN

VDD Load_ Phase

MCU LIN VDD

VH_LS

VH

I

IN+ S UVLO +

R VH VH

C O Floating Level GOUT

Control L Section

Control

Shifter

A

IN- Logic T

Logic

R I CLAMP

C

O

VL_LS

N

Floating ground A + GNDISO GND_LS

GND

VCLAMPth VL

+ GND_PWR

DS13402 - Rev 4 page 12/22

STGAP2SICS

Layout

8 Layout

8.1 Layout guidelines and considerations

In order to optimize the PCB layout, the following considerations should be taken into account:

• SMT ceramic capacitors (or different types of low-ESR and low-ESL capacitors) must be placed close to

each supply rail pins. A 100 nF capacitor must be placed between VDD and GND and between VH and

GNDISO, as close as possible to device pins, in order to filter high-frequency noise and spikes. In order to

provide local storage for pulsed current, a second capacitor with a value between 1 µF and 10 µF should

also be placed close to the supply pins.

• It is good practice to add filtering capacitors close to logic inputs of the device (IN+, IN-), particularly for fast

switching or noisy applications.

• The power transistors must be placed as close as possible to the gate driver to minimize the gate loop area

and inductance that might carry noise or cause ringing.

• To avoid degradation of the isolation between the primary and secondary side of the driver, there should not

be any trace or conductive area below the driver.

• If the system has multiple layers, it is recommended to connect the VH and GNDISO pins to internal ground

or power planes through multiple vias of adequate size. These vias should be located close to the IC pins to

maximize thermal conductivity.

8.2 Layout example

An example of STGAP2SiCSC half-bridge suggested PCB layout with main signals highlighted by different colors

is shown in Figure 11. It is recommended to follow this example for correct positioning and connection of filtering

capacitors.

Figure 11. Half-bridge suggested PCB layout

RIN CVH1

G1

CIN ROFF

Q1

DOFF

CIN

RON

U1

RIN

CG

D1

CVDD1 CVH2

DBOOT

S1

RBOOT

G2

RIN CVH1 Q2

ROFF

CG

CIN D2

DOFF

CIN

RON

RIN

U2

CVDD1 CVH2 S2

TOP BOTTOM

DS13402 - Rev 4 page 13/22

STGAP2SICS

Testing and characterization information

9 Testing and characterization information

Figure 12. Timings definition

IN+ 50% 50%

IN- 50% 50%

tr tf tr tf

90% 90% 90% 90%

GON-GOFF 10% 10% 10% 10%

t Don t Doff t Don t Doff

Figure 13. CMTI test circuit

VDD

+

VDD

VH

+

IN+ I

S1

S

-

O GON

L Output V out

+

IN- A monitoring node VH

T GOFF

I

O

N

GND GNDISO

G1

DS13402 - Rev 4 page 14/22

STGAP2SICS

Package information

10 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages,

depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product

status are available at: www.st.com. ECOPACK is an ST trademark.

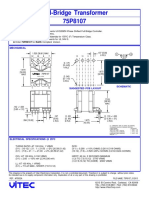

10.1 SO-8W package information

Table 10. SO-8W package dimensions

Dimensions (mm)

Symbol

Min. Typ. Max

A 2.34 2.64

A1 0.1 0.3

b 0.3 0.51

c 0.2 0.33

D(1) 5.64 6.05

e 1.27 BSC

E1 7.39 7.59

E 10.11 10.52

L 0.61 0.91

h 0.25 0.76

Ɵ 0° 8°

aaa 0.25

bbb 0.25

ccc 0.1

1. Dimension “D” does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed

0.15mm per side.

DS13402 - Rev 4 page 15/22

STGAP2SICS

SO-8W suggested land pattern

Figure 14. SO-8W mechanical data

0.01

A

c

8X b L

A1

D

e/2

E1

h X 45°

6X e

10.2 SO-8W suggested land pattern

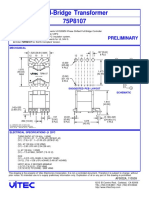

Figure 15. SO-8W suggested land pattern

1.27

0.6 (x8)

8.00 1.5

11.00

DS13402 - Rev 4 page 16/22

STGAP2SICS

Ordering information

11 Ordering information

Table 11. Device summary

Order code Output configuration Package marking Package Packaging

STGAP2SICSTR GON-GOFF GAP2IS SO-8W Tape and Reel

STGAP2SICSCTR GOUT-CLAMP GAP2SIC SO-8W Tape and Reel

DS13402 - Rev 4 page 17/22

STGAP2SICS

Revision history

Table 12. Document revision history

Date Version Changes

10-Sep-2020 1 Initial release.

Update VDD parameter in Table 4; update Isolation Resistance Test condition

13-Aug-2021 2 parameter in Table 7; update title of Table 8; change Figure 15 and Figure 10;

updated Table 3; updated Driver buffer section and Standby in Table 5.

15-Oct-2021 3 Updated test condition in Table 5

29-Sep-2022 4 Added UL file certification

DS13402 - Rev 4 page 18/22

STGAP2SICS

Contents

Contents

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2

2 Pin description and connection diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

3 Electrical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4

3.1 Absolute maximum ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.2 Thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

3.3 Recommended operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

4 Electrical characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

5 Isolation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7

6 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.1 Gate driving power supply and UVLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.2 Power-up, power-down and “safe state”. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

6.3 Control inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6.4 Miller Clamp function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6.5 Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6.6 Thermal shutdown protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

6.7 Standby function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

7 Typical application diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

8 Layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

8.1 Layout guidelines and considerations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

8.2 Layout example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

9 Testing and characterization information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

10 Package information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

10.1 SO-8W package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

10.2 SO-8W suggested land pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

11 Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

List of tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

List of figures. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

DS13402 - Rev 4 page 19/22

STGAP2SICS

List of tables

List of tables

Table 1. Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Table 2. Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 3. Thermal data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 4. Recommended operating conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Table 5. Electrical characteristics (TJ = 25°C, VH = 18 V, VDD = 5 V unless otherwise specified) . . . . . . . . . . . . . . . . . . . 5

Table 6. Isolation and safety-related specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 7. Isolation characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 8. Isolation voltage as per UL 1577 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Table 9. Inputs truth table (applicable when device is not in UVLO or "safe state") . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Table 10. SO-8W package dimensions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Table 11. Device summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Table 12. Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

DS13402 - Rev 4 page 20/22

STGAP2SICS

List of figures

List of figures

Figure 1. Block diagram - Single output and Miller Clamp configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Figure 2. Block diagram - Separate output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Figure 3. Pin connection (top view) - Single output and Miller CLAMP option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 4. Pin connection (top view) - Separated outputs option. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

Figure 5. Power supply configuration for unipolar and bipolar gate driving . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Figure 6. Standby state sequences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Figure 7. Typical application diagram - Separated outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 8. Typical application diagram - Separated outputs and negative gate driving . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Figure 9. Typical application diagram - Miller Clamp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 10. Typical application diagram - Miller Clamp and negative gate driving . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

Figure 11. Half-bridge suggested PCB layout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Figure 12. Timings definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 13. CMTI test circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Figure 14. SO-8W mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Figure 15. SO-8W suggested land pattern . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

DS13402 - Rev 4 page 21/22

STGAP2SICS

IMPORTANT NOTICE – READ CAREFULLY

STMicroelectronics NV and its subsidiaries (“ST”) reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST

products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST

products are sold pursuant to ST’s terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of

purchasers’ products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names

are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

DS13402 - Rev 4 page 22/22

You might also like

- Stgap 2 SDocument23 pagesStgap 2 SJose Luis FernandezNo ratings yet

- Stgap 2 SicdDocument24 pagesStgap 2 SicdbaireddyNo ratings yet

- CMOS 1.8 V to 5.5 V, 2.5 Ω SPDT Switch/2:1 Mux in Tiny SC70 Package ADG779Document13 pagesCMOS 1.8 V to 5.5 V, 2.5 Ω SPDT Switch/2:1 Mux in Tiny SC70 Package ADG779d&No ratings yet

- Stdrive601: Triple Half-Bridge High-Voltage Gate DriverDocument26 pagesStdrive601: Triple Half-Bridge High-Voltage Gate DriverRadu CrisanNo ratings yet

- 4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDocument44 pages4.5-V To 65-V Input, Compact Bias Supply With Power Stage Reference Design For Igbt/Sic Gate DriversDebasish MishraNo ratings yet

- Mastergan 5Document26 pagesMastergan 5AleksMaslyc-zykNo ratings yet

- Stdrive 101Document33 pagesStdrive 101AleksMaslyc-zykNo ratings yet

- Stdrive101: Triple Half-Bridge Gate DriverDocument32 pagesStdrive101: Triple Half-Bridge Gate DriverAlper ÜZÜMNo ratings yet

- H-Bridge Gate Driver IC: Freescale Semiconductor, IncDocument21 pagesH-Bridge Gate Driver IC: Freescale Semiconductor, IncDuy NgocNo ratings yet

- ISO1H812GDocument23 pagesISO1H812Gmar_barudjNo ratings yet

- 2059771linksw ln306gnDocument18 pages2059771linksw ln306gnRegulo GomezNo ratings yet

- Linkswitch-Xt2 Family Datasheet.Document26 pagesLinkswitch-Xt2 Family Datasheet.grivasNo ratings yet

- Mastergan 4Document27 pagesMastergan 4hobad57099No ratings yet

- Omron EE SX676 DatasheetDocument68 pagesOmron EE SX676 DatasheetHkhkhkhjg HfjdjfjfNo ratings yet

- STR-A6252M: Switching RegulatorsDocument13 pagesSTR-A6252M: Switching RegulatorsAntonioPeriniNo ratings yet

- HCPL 7601 AvagoDocument13 pagesHCPL 7601 AvagoSyed Khawar MukhtarNo ratings yet

- Sg3525a DDocument10 pagesSg3525a DmarcoNo ratings yet

- NCP1250 D-2317076Document26 pagesNCP1250 D-2317076ricardo mauro oliveiraNo ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document23 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™temarioNo ratings yet

- 4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Document21 pages4.5V To 23V Input, 3-A Synchronous Step-Down SWIFT™ Converter With Eco-Mode™Egor FedorenkoNo ratings yet

- Master Gan 2Document29 pagesMaster Gan 2Tevrat çağNo ratings yet

- LV059Document136 pagesLV059Boris KoganNo ratings yet

- NCP51810 DDocument20 pagesNCP51810 DArun Rajkumar K PNo ratings yet

- lnk302 - 304 306 179954 PDFDocument19 pageslnk302 - 304 306 179954 PDFBimMarius0% (1)

- Pole Top sf6 Gas Lbs - Pt. Eei - Rev. 1.3Document4 pagesPole Top sf6 Gas Lbs - Pt. Eei - Rev. 1.3user.haleyorapowerNo ratings yet

- Data Sheet: ACPL-32JTDocument18 pagesData Sheet: ACPL-32JTkbrinaldiNo ratings yet

- Half-Duplex, Icoupler Isolated Rs-485 Transceiver: Data SheetDocument18 pagesHalf-Duplex, Icoupler Isolated Rs-485 Transceiver: Data SheetMazhar SyedNo ratings yet

- Motercontrol CardinDocument28 pagesMotercontrol CardinaNo ratings yet

- 75-V/10-A Protected Full-Bridge Power Stage Reference Design For Bipolar Stepper DrivesDocument43 pages75-V/10-A Protected Full-Bridge Power Stage Reference Design For Bipolar Stepper DrivesJitbro PrajapatiNo ratings yet

- High CMR Isolation Amplifiers: HCPL-7800 HCPL-7800A HCPL-7800BDocument17 pagesHigh CMR Isolation Amplifiers: HCPL-7800 HCPL-7800A HCPL-7800BRobert AguilarNo ratings yet

- TMC5240 Preliminary Datasheet-3115115Document149 pagesTMC5240 Preliminary Datasheet-3115115Lars domeNo ratings yet

- SN65HVD1050Document19 pagesSN65HVD1050ZaegorNo ratings yet

- Can Transceiver: Features DescriptionDocument20 pagesCan Transceiver: Features Descriptionies837No ratings yet

- En dm00345339Document19 pagesEn dm00345339bhushan.pawarNo ratings yet

- Ucc 27624Document37 pagesUcc 27624jonathan.boussoir2215No ratings yet

- 100 V Half-Bridge MOSFET Driver: Features and Benefits DescriptionDocument13 pages100 V Half-Bridge MOSFET Driver: Features and Benefits Descriptionamp divisionNo ratings yet

- Acpl 337J 500eDocument18 pagesAcpl 337J 500eAandk NovaNo ratings yet

- Three-Phase Inverter Reference Design For 200-480 VAC Drives With Opto-Emulated Input Gate DriversDocument39 pagesThree-Phase Inverter Reference Design For 200-480 VAC Drives With Opto-Emulated Input Gate DriversM. T.No ratings yet

- Tidua 15 ADocument75 pagesTidua 15 AMohammed BenzaidiNo ratings yet

- NSI50350AST3G, NSV50350AST3G Constant Current Regulator & LED DriverDocument8 pagesNSI50350AST3G, NSV50350AST3G Constant Current Regulator & LED DriverHacker4300No ratings yet

- Single-/Dual-Supply, High Voltage Isolated IGBT Gate Driver With Miller ClampDocument18 pagesSingle-/Dual-Supply, High Voltage Isolated IGBT Gate Driver With Miller Clamprizki anugrahNo ratings yet

- Abb Flyer Igct 2015Document2 pagesAbb Flyer Igct 2015Dhruv PatelNo ratings yet

- k8ab Series OutDocument7 pagesk8ab Series OutHkhkhkhjg HfjdjfjfNo ratings yet

- Tidue 54 BDocument71 pagesTidue 54 BCương PhạmNo ratings yet

- SLW Series: Years in Process Control InstrumentationDocument2 pagesSLW Series: Years in Process Control InstrumentationdklikeNo ratings yet

- Recloser PadmountedDocument12 pagesRecloser Padmountedmjbriceno@gmail.comNo ratings yet

- Can Driver Ram 2005 Ecus Marco EsteliDocument27 pagesCan Driver Ram 2005 Ecus Marco EsteliautocomputerNo ratings yet

- AgileSwitch-Fuji Data Sheet V6 2011-07-18Document3 pagesAgileSwitch-Fuji Data Sheet V6 2011-07-18AgileSwitchNo ratings yet

- Acst 6Document20 pagesAcst 6taleb 6269No ratings yet

- Green-Mode PWM Controller With High Voltage Startup Circuit: Preliminary GR8875 SeriesDocument14 pagesGreen-Mode PWM Controller With High Voltage Startup Circuit: Preliminary GR8875 SeriesaliNo ratings yet

- K3020P, K3020PG Series Optocoupler, Phototriac Output, Non-Zero Crossing, 400 VDocument8 pagesK3020P, K3020PG Series Optocoupler, Phototriac Output, Non-Zero Crossing, 400 VCharbel TadrosNo ratings yet

- ST 730Document22 pagesST 730bigm94iNo ratings yet

- Lm2588 Simple Switcher 5A Flyback Regulator With Shutdown: Check For SamplesDocument38 pagesLm2588 Simple Switcher 5A Flyback Regulator With Shutdown: Check For SamplesTeles SilvaNo ratings yet

- A89503-Datasheet (1)Document45 pagesA89503-Datasheet (1)alynaalichaudhryNo ratings yet

- LMH0324RTWTDocument9 pagesLMH0324RTWTleonisio colaçoNo ratings yet

- Technical Offer For 11kv Sm6 SwitchgearDocument6 pagesTechnical Offer For 11kv Sm6 SwitchgeardmugalloyNo ratings yet

- Stdrive601 1608253Document26 pagesStdrive601 1608253Bolinha's Wash ClubNo ratings yet

- GDA2A4S1 Ver1.0Document11 pagesGDA2A4S1 Ver1.0Mulahim sitiNo ratings yet

- Linkswitch-Cv Family: Energy-Efficient, Off-Line Switcher With Accurate Primary-Side Constant-Voltage (CV) ControlDocument21 pagesLinkswitch-Cv Family: Energy-Efficient, Off-Line Switcher With Accurate Primary-Side Constant-Voltage (CV) ControlAriel DajaoNo ratings yet

- CKV 5919355Document1 pageCKV 5919355Kantesh KudapaliNo ratings yet

- Full-Bridge Transformer 75P8107: FeaturesDocument1 pageFull-Bridge Transformer 75P8107: FeaturesKantesh KudapaliNo ratings yet

- (Cin) L65190mh2004goi148838Document2 pages(Cin) L65190mh2004goi148838Kantesh KudapaliNo ratings yet

- Full-Bridge Transformer 75P8107: PreliminaryDocument1 pageFull-Bridge Transformer 75P8107: PreliminaryKantesh KudapaliNo ratings yet

- S L V Technologies: Particulars Credit Debit Opening Balance 61,212.74Document1 pageS L V Technologies: Particulars Credit Debit Opening Balance 61,212.74Kantesh KudapaliNo ratings yet

- Analysis of Power Loss and Improved Simulation MetDocument18 pagesAnalysis of Power Loss and Improved Simulation MetKantesh KudapaliNo ratings yet

- S L V Technologies: Particulars Credit Debit Opening Balance 1,17,684.56Document1 pageS L V Technologies: Particulars Credit Debit Opening Balance 1,17,684.56Kantesh KudapaliNo ratings yet

- Uni-U3115s-6s 300v 1.2a Half Bridge Driver v3.0Document2 pagesUni-U3115s-6s 300v 1.2a Half Bridge Driver v3.0Kantesh KudapaliNo ratings yet

- DRV8305-Q1 Three-Phase Automotive Smart Gate DriverDocument58 pagesDRV8305-Q1 Three-Phase Automotive Smart Gate Drivergotcha75No ratings yet

- AN296220 Bootstrap SupplyDocument4 pagesAN296220 Bootstrap Supplya9841140155No ratings yet

- Application Note: Extremely Compact, Isolated Gate Driver Power Supply For Sic-Mosfet (6 - 10 W)Document5 pagesApplication Note: Extremely Compact, Isolated Gate Driver Power Supply For Sic-Mosfet (6 - 10 W)Wesley de PaulaNo ratings yet

- Three-Phase Inverter Reference Design For 200-480 VAC Drives With Opto-Emulated Input Gate DriversDocument39 pagesThree-Phase Inverter Reference Design For 200-480 VAC Drives With Opto-Emulated Input Gate DriversM. T.No ratings yet

- FAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionDocument18 pagesFAN7392 High-Current, High-And Low-Side, Gate-Drive IC: Features DescriptionRaghu RamanNo ratings yet

- Demonstration Board For STDRIVE601 Triple Gate Driver: Evalstdrive601Document10 pagesDemonstration Board For STDRIVE601 Triple Gate Driver: Evalstdrive601amadNo ratings yet

- LM5109B High Voltage 1-A Peak Half-Bridge Gate Driver: 1 Features 3 DescriptionDocument29 pagesLM5109B High Voltage 1-A Peak Half-Bridge Gate Driver: 1 Features 3 DescriptionDaniel JiménezNo ratings yet

- 80V To 150V Non-Isolated DC/DC: Controllers, Monolithics & MOSFET DriversDocument4 pages80V To 150V Non-Isolated DC/DC: Controllers, Monolithics & MOSFET DriversDuc VoquangNo ratings yet

- PI IGBT ProductCatalog PDFDocument52 pagesPI IGBT ProductCatalog PDFanand shekhawatNo ratings yet

- Control Integrated Power System (CIPOS™) : AN2016-10 Application NoteDocument46 pagesControl Integrated Power System (CIPOS™) : AN2016-10 Application NoteNoe SaantNo ratings yet

- Isolated Gate Driving Solutions: AN - 1909 - PL52 - 1910 - 201256Document21 pagesIsolated Gate Driving Solutions: AN - 1909 - PL52 - 1910 - 201256Adailton SantosNo ratings yet

- DC Power Switch 1473lfDocument16 pagesDC Power Switch 1473lfshabaz_yousaf2734No ratings yet

- TIDUE531 10-kW, Bidirectional Three-Phase Three-Level (T-Type) Inverter and PFCDocument94 pagesTIDUE531 10-kW, Bidirectional Three-Phase Three-Level (T-Type) Inverter and PFCvituvxiaomi redmi5plusNo ratings yet

- Avago Application Note 1335 - Main Applications and Selection of Gate Driver Optocouplers PDFDocument8 pagesAvago Application Note 1335 - Main Applications and Selection of Gate Driver Optocouplers PDFFabiano TonnNo ratings yet

- DGD2110 DGD2113 App NoteDocument10 pagesDGD2110 DGD2113 App NotecharlesNo ratings yet

- Half Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VDocument2 pagesHalf Bridge Driver Based On: C2 1uF/25V CN1 C5 10uF/25V D1 MBRS140T3G C3 220uF/63VratnaNo ratings yet

- LM5046-Phase Shifted Full Bridge ControllerDocument48 pagesLM5046-Phase Shifted Full Bridge ControllerCataNo ratings yet

- LITIX™ Power Flex TLD5190: Voltage Regulator in Buck-Boost TopologyDocument23 pagesLITIX™ Power Flex TLD5190: Voltage Regulator in Buck-Boost TopologyManoel Camargo SampaioNo ratings yet

- HIP4082IBZ A Half-Bridge FET Gate DriveDocument5 pagesHIP4082IBZ A Half-Bridge FET Gate DrivejackNo ratings yet

- DRV 8353Document87 pagesDRV 8353Gustavo BessoneNo ratings yet

- lm5110 1 PDFDocument13 pageslm5110 1 PDFHưng HQNo ratings yet

- LM5106 100-V Half-Bridge Gate Driver With Programmable Dead-TimeDocument26 pagesLM5106 100-V Half-Bridge Gate Driver With Programmable Dead-TimeRavi JagtianiNo ratings yet

- Speed Control of DC Motor Using ChopperDocument7 pagesSpeed Control of DC Motor Using ChopperKoustav DasguptaNo ratings yet

- l6498 1849607 STMicroelectronicsDocument21 pagesl6498 1849607 STMicroelectronicsWalter Martin Paz HolguinNo ratings yet

- 2-Phase + 1-Phase PWM Controller With I2C Digital Interface For Vr12 CpusDocument31 pages2-Phase + 1-Phase PWM Controller With I2C Digital Interface For Vr12 CpushoroncioNo ratings yet

- drv8343 q1Document89 pagesdrv8343 q1Lu HoaNo ratings yet

- ATMEL High Temp H BridgeDocument13 pagesATMEL High Temp H BridgeGoran ŠtetinNo ratings yet

- AP8269 AiTSemiconductorDocument11 pagesAP8269 AiTSemiconductorAlexandre Marido de AluguelNo ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument11 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersTom TomNo ratings yet

- Automotive Power Selection Guide 2019: Ultimate Power - Perfect ControlDocument146 pagesAutomotive Power Selection Guide 2019: Ultimate Power - Perfect ControlJohn Kevin ToralNo ratings yet