Professional Documents

Culture Documents

ELEC40003 DECA_Exam Paper

ELEC40003 DECA_Exam Paper

Uploaded by

Vikas BalikaiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ELEC40003 DECA_Exam Paper

ELEC40003 DECA_Exam Paper

Uploaded by

Vikas BalikaiCopyright:

Available Formats

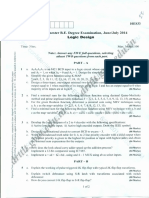

ELEC40003

IMPERIAL COLLEGE LONDON

DEPARTMENT OF ELECTRICAL AND ELECTRONIC ENGINEERING

EXAMINATIONS 2023

ExamHeader:

DIGITAL ELECTRONICS & COMPUTER ARCHITECTURE

Tuesday 9 May 14:30

Time allowed: 2:00 hours

There are THREE questions on this paper.

Answer ALL questions. Question One carries 40 marks. Question Two

and Question Three carry 30 marks each.

Any special instructions for invigilators and information for

candidates are on page 1.

Examiners responsible First Marker(s) : G. Constantinides

Second Marker(s) : T. Clarke

© Imperial College London

D IGITAL E LECTRONICS AND C OMPUTER A RCHITECTURE

1. a) Simplify the following Boolean expression. You may use any method, but the

method must be clear from your answer.

(A B +C)(A B C)

[4]

b) Simplify the Boolean expression Y = ∑ 0, 2, 4, 5, 10, 11 using a Karnaugh map,

leaving your answer in sum-of-products form. Show all your working. (You do

not need to consider the elimination of static hazards.)

[4]

c) Rewrite the Boolean expression A B C + D in minimal product-of-sums form.

[2]

d) Write the decimal values −3 and 10 in 8-bit twos complement. Then also write

their respective sign extensions in 16-bit twos complement.

[4]

e) Draw a Mealy state diagram for the circuit shown in Figure 1.1, where the flip-

flop’s clock inputs are connected to a suitable external clock signal (not shown).

[4]

Figure 1.1 A sequential circuit.

f) Write a Boolean sum-of-products equivalent to the expression B C + A C but

eliminating static hazards.

[2]

Digital Electronics and Computer Architecture ©Imperial College London 1/5

MOV R0, #255

MOV R1, #10

ADD R1, R1, R1

SBC R1, #2

MOV R2, #0x4E

MOV R3, #0x65

AND R2, R2, R3

LSR R3, R3, #1

XSR R4, R3, #1

MOV R5, #0xFF

LSL R5, R5, #8

ASR R5, R5, #3

Figure 1.2 EEP1 program

g) Figure 1.2 shows an EEP1 program which is loaded into the EEP1 instruction

ROM CODEMEM starting at location 0. The EEP1 CPU executes this program

from location 0. Write the values, in hexadecimal, of the 6 registers R0 −

R5, CODEMEN[0], and the EEP1 Program Counter, when the ASR instruction is

executing.

[8]

h) X(n − 1 : 0) is an n-bit binary value, and u(X), z(X) are respectively the un-

signed and twos complement signed interpretations of X. Derive an expression

for u(X) − z(X) in terms of the bits of X and prove that it is a multiple of 2n .

Explain what this means for the hardware implementation of twos complement

signed arithmetic.

[4]

Figure 1.3 EEP1 program

i) Figure 1.3 shows an ALU with data inputs A, B, output C, and control inputs

F1, F2, F3. Write an algebraic truth table for the ALU with 8 rows, each ex-

pressing the output C as an arithmetic expression of the inputs.

[8]

Digital Electronics and Computer Architecture ©Imperial College London 2/5

2. You are asked to design a circuit with two Boolean inputs which are to be interpreted in

this question as a single two’s complement word X(1 : 0).

The circuit behaves as a two-bit synchronous counter which, on each clock rising edge,

adds the current value of its two-bit two’s complement state Y (1 : 0) to the value of

its two’s complement input X(1 : 0) to produce its new state. If the new state would

overflow in the positive direction, then instead of the sum, the new state becomes the

maximum positive value representable as a two-bit two’s complement number. Like-

wise, if the new state would overflow in the negative direction, then instead of the sum,

the new state becomes the maximum negative value representable as a two-bit two’s

complement number.

The output of the circuit is a single bit Z which indicates whether the current state is

zero.

An example of this behaviour is shown in the timing diagram of Figure 2.1, for which

the starting state is assumed to be Y (1 : 0) = 0.

clk

X(1:0) 0 -1 1 0 1 1 -1 -1 -1 -1 0

Y(1:0) 0 0 -1 0 0 1 1 0 -1 -2 -2

Figure 2.1 Timing diagram.

a) Draw a Moore state diagram of a FSM implementing the required behaviour.

[8]

b) Write out Karnaugh maps for the output, and each bit of the next-state variable,

of the FSM. Use the Karnaugh maps to obtain the minimal sum-of-product ex-

pressions, explicitly identifying the groups in your Karnaugh maps correspond-

ing to each product term.

[ 12 ]

c) Through the application of DeMorgan’s Theorem to your sum-of-products ex-

pressions, draw a circuit directly implementing this state machine using only

D-flip flops and NAND gates. Your NAND gates may have an arbitrary num-

ber of inputs. Show all your working.

[ 10 ]

Digital Electronics and Computer Architecture ©Imperial College London 3/5

3. a) Figure 3.1 shows the required transfer of 4 words of data from memory to regis-

ters R2-R5 in an EEP1 program. Data transfers are indicated by dotted arrows.

Write a sequence P1 of EEP1 assembler instructions which implements this

transfer. Credit will be given for shorter solutions.

[6]

b) State, with reasons for correctness, a single EEP1 instruction that will imple-

ment 16-bit bitwise logical NOT: R0(i) := R1(i). You may assume the existence

of a constant value you specify in a register.

[2]

c) Showing your reasoning, derive an expression for bitwise logical OR, using

only bitwise logical AND and NOT operations.

[2]

d) Write in EEP1 assembler a subroutine P2 that implements the 16-bit bitwise

logical OR operation.

R0(i) := R0(i) + R1(i) (+ is boolean OR).

Credit will be given for correct solutions minimising the number of instructions.

[6]

e) Assume that P1 and P2 work as specified. Define x0, x1, x2, x3 to be the values

in memory locations as in Figure 3.1. Write an EEP1 assembler program P3

that includes P1 and then calls P2 multiple times to implement the bitwise

operation:

R0(i) := x0(i) + x1(i) + x2(i) + x3(i) ( + is boolean OR).

[4]

f) The code in P3 is run on a pipelined implementation of EEP1 with 200MHz

clock frequency. The pipeline runs with one stall cycle for each LDR instruction

and no other stalls. State the dynamic total of instructions, n, and dynamic

number of LDR instructions, m, in the execution of P3. Calculate, showing

your working, the instruction throughput of P3.

[5]

g) Write the entry and exit code necessary to make your program P3 into a sub-

routine complying with the EEP1 Subroutine Call Protocol. Draw the P3 stack

frame showing the relative position in memory of each stored register.

[5]

Digital Electronics and Computer Architecture ©Imperial College London 4/5

Figure 3.1 Memory pointer diagram

Digital Electronics and Computer Architecture ©Imperial College London 5/5

You might also like

- SS Brewtech 1V Using Omron E5CC PID Cheat SheetDocument2 pagesSS Brewtech 1V Using Omron E5CC PID Cheat SheetJNo ratings yet

- Eng632d1 CW1Document8 pagesEng632d1 CW1Kobi Smith100% (1)

- Eee 058Document5 pagesEee 058Brevin DraxlerNo ratings yet

- Elec103p Exam 2015Document8 pagesElec103p Exam 2015cweqingNo ratings yet

- CEG 2131 - Fall 2003 - FinalDocument14 pagesCEG 2131 - Fall 2003 - FinalAmin DhouibNo ratings yet

- Digital Electronics and Computer Architecture ELEC40003 EXAM PAPERDocument7 pagesDigital Electronics and Computer Architecture ELEC40003 EXAM PAPERVikas BalikaiNo ratings yet

- STLD 2009 RegularDocument4 pagesSTLD 2009 RegularrangerNo ratings yet

- University of Bristol Faculty of Engineering: Digital Circuits & Systems EENG14000Document7 pagesUniversity of Bristol Faculty of Engineering: Digital Circuits & Systems EENG14000栾子璇No ratings yet

- Rr210203 Switching Theory and Logic DesignDocument8 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- Rr210203 Switching Theory and Logic DesignDocument9 pagesRr210203 Switching Theory and Logic DesignSrinivasa Rao GNo ratings yet

- Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inDocument2 pagesDrttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inrama KrishnaNo ratings yet

- Mock Paper Computer ArchitectureDocument17 pagesMock Paper Computer ArchitectureYang ZhouNo ratings yet

- 19EC303 DPSD Learners Copy 11 03 24Document56 pages19EC303 DPSD Learners Copy 11 03 24Marshmellow FFNo ratings yet

- Digital Electronic Circuits (ELE-208) RCSDocument2 pagesDigital Electronic Circuits (ELE-208) RCSSudhakar JoshiNo ratings yet

- DP-Assignment Brief A1 - UpdatedDocument12 pagesDP-Assignment Brief A1 - UpdatedTân NguyễnNo ratings yet

- Digital Electronics and Microcontroller Applications Winter 2019 Answer PaperDocument15 pagesDigital Electronics and Microcontroller Applications Winter 2019 Answer PaperShreyas KingeNo ratings yet

- Ec 1202 Digital System DesignDocument8 pagesEc 1202 Digital System DesignworkubNo ratings yet

- 15A04306 Digital Logic Design4Document2 pages15A04306 Digital Logic Design4Lakshmi PrashanthNo ratings yet

- EC3352 Digital System DesignDocument22 pagesEC3352 Digital System DesignParanthaman GNo ratings yet

- DLD Ques2Document2 pagesDLD Ques2mahbub mitulNo ratings yet

- Dig2E - 2017 QuestionsDocument7 pagesDig2E - 2017 QuestionsHardik MakwanaNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- Elec1207 201819 02 Elec1207w1Document7 pagesElec1207 201819 02 Elec1207w1faihan.janNo ratings yet

- ELEC103P Exam 2017Document7 pagesELEC103P Exam 2017cweqingNo ratings yet

- Southern University CollegeDocument4 pagesSouthern University CollegeZhong Kiat TehNo ratings yet

- 18IT302Document13 pages18IT302SUSEENDRAN VNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument23 pages3 Hours / 70 Marks: Seat NoHitesh BadgujarNo ratings yet

- BE End Term 2021-22Document3 pagesBE End Term 2021-2223ucc590No ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- DLDM Question BankDocument8 pagesDLDM Question BankMayur PatilNo ratings yet

- Ect203 Logic Circuit Design, December 2021Document2 pagesEct203 Logic Circuit Design, December 2021instapc0210No ratings yet

- C-Language:) Configuration To Star Configuration. R R RDocument4 pagesC-Language:) Configuration To Star Configuration. R R Rthe crowNo ratings yet

- ELEC103P Exam 2018Document7 pagesELEC103P Exam 2018cweqingNo ratings yet

- S T L DDocument12 pagesS T L DMohan Krishna0% (1)

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Ec1312 DLCDocument5 pagesEc1312 DLCDeepak RavichandranNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignVenkat ChadalavadaNo ratings yet

- UEC702Document2 pagesUEC702RaunaqSinghNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument88 pages3 Hours / 70 Marks: Seat Noyashbirari29No ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- College of Engineering Putrajaya Campus Final Examination SEMESTER 2 2010 / 2011Document8 pagesCollege of Engineering Putrajaya Campus Final Examination SEMESTER 2 2010 / 2011shahNo ratings yet

- PHC-253 - DigitalAssignmentDocument1 pagePHC-253 - DigitalAssignmentPrashant SinghNo ratings yet

- World: Code: 9A02401Document7 pagesWorld: Code: 9A02401surya pratapNo ratings yet

- Ecs-301 Digital Logic Design 2009-10Document4 pagesEcs-301 Digital Logic Design 2009-10Satyedra MauryaNo ratings yet

- Btech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Document3 pagesBtech Biomed 4 Sem Digital Electronics Circuit Pbm4i102 2018Narinder MauryaNo ratings yet

- Ae8501 Ad-Ii Unit Wise QBDocument15 pagesAe8501 Ad-Ii Unit Wise QBpugazhNo ratings yet

- Ω Ω Ω. Find the β β β βDocument3 pagesΩ Ω Ω. Find the β β β βJoginder YadavNo ratings yet

- Code No: 35095Document8 pagesCode No: 35095SRINIVASA RAO GANTA100% (1)

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- Campusexpress - Co.in: Set No. 1Document8 pagesCampusexpress - Co.in: Set No. 1skssush100% (1)

- Qb-Prec-Dlc-Ii YearDocument15 pagesQb-Prec-Dlc-Ii YearParvatham VijayNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- COA Question Bank With SolutionDocument145 pagesCOA Question Bank With SolutionSandeep Kumar YadavNo ratings yet

- 2019 Summer Question Paper (Msbte Study Resources)Document4 pages2019 Summer Question Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- B.Tech II Year I Semester (R13) Supplementary Examinations June 2016 Time: 3 HoursDocument2 pagesB.Tech II Year I Semester (R13) Supplementary Examinations June 2016 Time: 3 HoursKareem KhanNo ratings yet

- Organic Light-Emitting Transistors: Towards the Next Generation Display TechnologyFrom EverandOrganic Light-Emitting Transistors: Towards the Next Generation Display TechnologyNo ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Digital Electronics and Computer Architecture ELEC40003 EXAM PAPERDocument7 pagesDigital Electronics and Computer Architecture ELEC40003 EXAM PAPERVikas BalikaiNo ratings yet

- ELEC40003 Digital Electronics and Computer Architecture SOLUTIONS Summer '20Document10 pagesELEC40003 Digital Electronics and Computer Architecture SOLUTIONS Summer '20Vikas BalikaiNo ratings yet

- Lecture 3 (1)Document27 pagesLecture 3 (1)Vikas BalikaiNo ratings yet

- Electronics: Novel Low-Complexity and Low-Power Flip-Flop DesignDocument12 pagesElectronics: Novel Low-Complexity and Low-Power Flip-Flop DesignVikas BalikaiNo ratings yet

- Design and Analysis of Fs-Tspc-Det Flip-Flop For Iot ApplicationsDocument9 pagesDesign and Analysis of Fs-Tspc-Det Flip-Flop For Iot ApplicationsVikas BalikaiNo ratings yet

- Lec 18 (HTML DIV+Image)Document11 pagesLec 18 (HTML DIV+Image)Informational VideosNo ratings yet

- User'S and Maintenance Manual: EnglishDocument11 pagesUser'S and Maintenance Manual: EnglishYugler Quiroga NoaNo ratings yet

- CCNA Exploration2 - Routing Protocols and Concepts - Chapter 3 ExamDocument6 pagesCCNA Exploration2 - Routing Protocols and Concepts - Chapter 3 Examchocolat4No ratings yet

- Mga Resulta Sa Web: Oooff - Urban DictionaryDocument5 pagesMga Resulta Sa Web: Oooff - Urban DictionaryFu Yu Hui JuNo ratings yet

- Kernel Context Recommender System PDFDocument19 pagesKernel Context Recommender System PDFSri Lalitha MunukutlaNo ratings yet

- Wireless Mouse Tecknet m002 PDFDocument20 pagesWireless Mouse Tecknet m002 PDFsarvanrbNo ratings yet

- Artificial Intelligence To Assist Mathematical ReasoningDocument89 pagesArtificial Intelligence To Assist Mathematical Reasoningabcdef0567890No ratings yet

- CS-3035 (ML) - CS Mid March 2023Document3 pagesCS-3035 (ML) - CS Mid March 2023Jaideep SharmaNo ratings yet

- ECMAScript 6Document6 pagesECMAScript 6Albano FuttaNo ratings yet

- SE8300 User Interface Guide: Commercial and Hotel/Lodging HVAC Fan Coil ApplicationsDocument50 pagesSE8300 User Interface Guide: Commercial and Hotel/Lodging HVAC Fan Coil ApplicationsInflation EngineeringNo ratings yet

- PDF Angular 2 Cookbook Frisbie Ebook Full ChapterDocument53 pagesPDF Angular 2 Cookbook Frisbie Ebook Full Chaptercrystal.otero761100% (7)

- GC CatalogDocument30 pagesGC CatalogMiguel QueirosNo ratings yet

- FY07 DoD ContractorsDocument191 pagesFY07 DoD Contractorsaptureinc100% (9)

- A Risk Assessment Tool For Network Resilience EvaluationDocument11 pagesA Risk Assessment Tool For Network Resilience EvaluationparamcNo ratings yet

- Samsung-Fendgo VOL004Document9 pagesSamsung-Fendgo VOL004Alvin ValorNo ratings yet

- Prediction For Manufacturing Factors in A Steel Plate Rolling Smart Factory Using Data Clustering-Based Machine LearningDocument16 pagesPrediction For Manufacturing Factors in A Steel Plate Rolling Smart Factory Using Data Clustering-Based Machine LearningKamran MujahidNo ratings yet

- MCSE-003 NoRestrictionDocument16 pagesMCSE-003 NoRestrictionBhargav Hathi100% (1)

- Multi-Head Self-Attention Transformer For Dogecoin Price PredictionDocument6 pagesMulti-Head Self-Attention Transformer For Dogecoin Price PredictionThu GiangNo ratings yet

- Overview Intel SRT Zbook17+8770w Oct 2013 4aa4-8675enwDocument4 pagesOverview Intel SRT Zbook17+8770w Oct 2013 4aa4-8675enwhutz5000No ratings yet

- BODMAS WorksheetDocument3 pagesBODMAS Worksheetkym.millikinNo ratings yet

- New Connection LT New Connection Flow Hierarchy (NPDCL) :: With Out Extension Flow DescriptionDocument2 pagesNew Connection LT New Connection Flow Hierarchy (NPDCL) :: With Out Extension Flow DescriptionchinnaNo ratings yet

- Vendor Management: Definition and UsesDocument3 pagesVendor Management: Definition and UsessnowFlakes A0% (1)

- Campus Solutions 9.0 To EBS Financials (General Ledger) Integration Developer's Reference GuideDocument171 pagesCampus Solutions 9.0 To EBS Financials (General Ledger) Integration Developer's Reference Guidesarat uppalapatiNo ratings yet

- Migration Guide - Sentinel HASP To Sentinel LDKDocument37 pagesMigration Guide - Sentinel HASP To Sentinel LDKzeljkogrNo ratings yet

- E Learning Essentials 508Document28 pagesE Learning Essentials 508api-559575515No ratings yet

- Dot Net FileDocument8 pagesDot Net FilePawan KumarNo ratings yet

- CH 2 Operational Amplifiers 2022Document88 pagesCH 2 Operational Amplifiers 2022鄭又嘉No ratings yet

- Huawei PCB Layout: Mate 10 LiteDocument2 pagesHuawei PCB Layout: Mate 10 LiteSamuel Shemuel YanezNo ratings yet

- Comparison Between Load-Flow Analysis Methods in Power SystemDocument8 pagesComparison Between Load-Flow Analysis Methods in Power SystemnpfhNo ratings yet