Professional Documents

Culture Documents

CAO Guess Paper

CAO Guess Paper

Uploaded by

baburishabh368Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CAO Guess Paper

CAO Guess Paper

Uploaded by

baburishabh368Copyright:

Available Formats

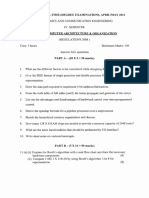

Guess Paper 2024

Pa

Arya Institute of Engineering Technology and Management

Guess Paper

Subject with Code : COA (6CAI4-04) Course & Branch: B.Tech – CSE & CSD

Year & Sem: III-B.Tech & VI -Sem

UNIT –I Computer Data Representation

Part -A (2 marks)

1. Differentiate between Computer Architecture and organization.

2. Differentiate between Instruction code and Operation Code.

3. Differentiate between memory reference and register reference computer instruction.

4. What is the Difference between Direct or Indirect address instruction.

5. What is an instruction cycle and write the phases of Instruction cycle?

6. What are the two instruction needed in the basic computer in order to set E flip -flop to 1.

7. Write the basic instruction formats for IO, Register and Memory Reference instructions.

8. Convert +1001.11 in 8 bit fraction and 6 bit exponent as per floating point representation.

9. Describe the three fields (Mode, Opcode and Address field) of 16 bit instruction format.

10. Describe the purpose of Buffer gate.

Part - B (8 marks)

1. b) Explain the phases involved in Instruction cycle with the help of necessary timing diagrams?

2. An output program resides in memory starting from address 230. It is executed after the computer

recognizes an interrupt when FGO becomes a 1 (while IEN = 11.

(a) What instruction must be placed at address 1?

(b) What must be the last two instructions of the output program?

3.Represent the following conditional control statement by two register transfer statements with control

functions.

if(P=I) then (R1 R2) else If (Q=I) then (RI R3)

4. Draw a timing diagram assuming that SC is cleared to 0 at time T3 if control signal C 7. is active.

C7T: SC0

C7 is activated with the positive clock transition associated with T7.

5.Discuss the concept of bus and memory transfers in computer systems. Explain the function

of tree-state bus buffers and their role in improving system performance.

6. The memory unit of a computer has 256K words of 32 bits each. The computer has an

instruction format with four fields: an operation code field, a mode field to specify one of

seven addressing modes, a register address field to specify one of 60 processor registers. and a

memory address. Specify the instruction format and the number of bits in each field if the in

instruction is in one memory word.

Part – C

COMPUTER ORGANISATION & ARCHITECTURE Page 1

Guess Paper 2024

Pa

1.Explain the basic Computer design and accumulator unit. With neat diagram

2. Describe Type of computer instruction with diagram.

3.Explain about bus and memory transfer in brief.

4. Describe about arithmetic shift unit with Diagram.

5.Explain about input output and interrupt handling.

6.Explain about type of computer register in brief.

UNIT –II Programming the basic computer

Part -A (2 marks)

1.Differentiate between assembly language and machine language.

2. Show how the MRI and non-MRI tables can be stored in memory.

3.Explain the difference between hardwired control and microprogrammed control.

4. Describe Subroutine.

5. The control memory in Fig. 7-2 has 4096 words of 24 bits each.

a. How many bits are there in the control address register?

b. How many bits are there in each of the four inputs shown going into the multiplexers?

c. What are the number of inputs in each multiplexer and how many multiplexers are needed?

6. program; Define the following (a) microcode. (a) microoperation (b) microinstruction

(c) microprogram

7. What is the difference between a microprocessor and a microprogram? Is it possible to design a

microprocessor without a microprogram? Are all microprogrammed computers also microprocessors?

8. Explain about control memory.

9. Explain about Microinstruction Format.

10.Explain about mapping of instruction to microinstruction format.

Part -B (8 marks)

1. What do you understand about address Sequencing? Explain about how to select address from

control memory.

2. Explain about Micro programmed control Organization.

3. Write a program to subtract two double-precision numbers.

4. Write a program loop, using a pointer and a counter, that clears to 0 the contents of hexadecimal

locations 500 through 5FF.

5. What do you understand about Input output programming? Explain about program interrupt.

6. Write a program to demonstrate the use of subroutine.

Part -C (15 marks)

COMPUTER ORGANISATION & ARCHITECTURE Page 2

Guess Paper 2024

Pa

1. An instruction at address 021 in the basic computer has 1 = 0, an operation code of the AND

instruction, and an address part equal to 083 (all numbers are in hexadecimal). The memory word at

address 083 contains the operand B8F2 and the content of AC is A937. Go over the instruction

cycle and determine the contents of the following registers at the end of the execute phase: PC, AR.

DR. AC: and IR. Repeat the problem three more times starting with an operation code of another

memory-reference instruction.

2. Explain about Microprogrammed control units with diagram.

3. Explain about assembler first pass and second pass with flowchart.

4. Describe about programming arithmetic and logic operation briefly.

5. What do you mean by control memory? How is it different from simple memory?

6. What are the various type of instructions supported by the 8086 family? Discuss each briefly.

UNIT –III Central Processing Unit

Part -A (2 marks)

1.Define about RISC characteristics.

2. Define about CISC characteristics.

3.Write the formula of speedup of pipeline processing.

4.Discuss on concept of parallel processing.

5.Explain about parallel processing.

6. The lime delay of the four segments in the pipeline are as follows: t1=50ns, t2 =30ns, t3= 95 ns,

and t4=45 ns. The interface registers delay time t= 5 ns

.a. How long would it take to add 100 pairs of numbers in the pipeline?

b. How can we reduce the total lime to about one-half of the lime calculated in part (a)?

7. Explain about RISC instruction.

8.Explain about Flynn’s Classification.

9.Explain about array processor.

10.Describe the advantage of parallel processing.

Part -B (8 marks)

1.Write the RISC I instruction in assembly language that will cause a jump to address 3200 if the Z

(zero) status bit is equal to 1.

(a) Using immediate mode

(b) Using a relative address mode (assume that PC = 3400)

2. Explain about different type of addressing modes

3. Explain about the Architecture of RISC and CISC.

4. Define the following terms:

a. Instruction pipeline

b. Arithmetic Pipeline

c. RISC pipeline

5. Explain briefly about four segment pipelines with space time Diagram.

COMPUTER ORGANISATION & ARCHITECTURE Page 3

Guess Paper 2024

Pa

6. A non-pipeline system takes 100 ns to process a task. The same task can be processed in a six -

segment pipeline with a clock cycle of 20 ns. Determine the speed up ratio of pipeline for 200

tasks. What is maximum speed - up that can be achieved?

Part -C (15 marks)

1.Formulate a six-segment instruction pipeline for a computer Specify the operations to be performed in

each segment.

2.Give an example of a RISC I instructions that will perform the following operations

(a) Decrement a register

(b) Complement a register

(c) Negate a register

(d) Clear a register to 0

(e) Divide a signed number by 4

(1) No operation.

3. Describe Different type of Instruction Format with Example of Program.

4. Explain four possible hardware schemes that can be used in an instruction pipeline in order to

minimize the performance degradation caused by instruction branching.

5. What do you understand by vector processing? Explain about the advantages and applications of

vector processing.

6.Explain about zero, one, two and three instruction format with example.

UNIT –IV Computer Arithmetic

Part -A (2 marks)

1. List four peripheral devices that produce an acceptable output for a person to understand.

2. Define about Input Output Interface.

3. Describe interrupt Initiated Interrupt.

4. Explain about priority interrupt.

5. Differentiate between synchronous and asynchronous data transfer methods in the

context of input-output operations.

6. What is the IEEE 754 standard, and how does it relate to floating-point arithmetic

operations?

7. What do you understand by VAD.

8. Describe the structure of floating-point numbers according to the IEEE 754 standard

and explain how arithmetic operations are performed on them.

COMPUTER ORGANISATION & ARCHITECTURE Page 4

Guess Paper 2024

Pa

9. What do you understand by Decimal Arithmetic unit?

10. Draw the hardware implementation of both sign magnitude and sign 2’s complement

for addition/subtraction.

Part -B (8 marks)

1. What is the basic advantage of using interrupt-initiated data transfer over transfer under

program control without an interrupt?

2. A commercial interface unit uses different names for the handshake lines associated with the

transfer of data from the 110 devices into the interface unit. The interface input handshake line

is labelled STB (strobe), and the interface output handshake line is labelled IBF (input buffer

full). A low-level signal on STB loads data from the 110 bus into the interface data register. A

high-level signal on IBF indicates that the data item has been accepted by the interface. IBF

goes low after an 110 read signal from the CPU when it reads the contents of the data register.

a. Draw a block diagram showing the CPU, the interface, and the 110 devices together with the

pertinent interconnections among the three units.

b. Draw a timing diagram for the handshaking transfer.

c. Obtain a sequence-of-events flowchart for the transfer from the device to the interface and

from the interface to the CPU.

3. What is the difference between isolated I/O and memory-mapped I/O? What are the advantages

and disadvantages of each?

4. Explain about CPU I/O communication.

5. Explain about DMA with the neat diagram.

6. Explain about Daisy chaining interrupt with neat diagram

Part -C (15 marks)

1.How many characters per second can be transmitted over a 1200-baud line in each of the

following modes? (Assume a character code of eight bits.) (15)

(a) Synchronous serial transmission.

(b) Asynchronous serial transmission with two stop bits.

(c) Asynchronous serial transmission with one stop bit.

2.Show the step-by-step multiplication process using Booth algorithm (as in Table 10-3) when the

following binary numbers are multiplied. Assume 5-bit registers that hold signed numbers. The

multiplicand in both cases is (+ 15).

a. (+15) x (+13)

b. (+15) X (-13)

3. Draw a flowchart of Floating-point division algorithm.

4.Draw the flowchart of addition and subtraction algorithm.

5.Explain about restoring and non-restoring Division algorithm.

6.Explain briefly about Booth’s algorithm.

COMPUTER ORGANISATION & ARCHITECTURE Page 5

Guess Paper 2024

Pa

UNIT –V Memory Organization

Part -A (2 marks)

1.Describe the following terminology associated with multiprocessors. (a) mutual exclusion; (b)

critical section; (c) hardware lock; (d) semaphore; (e) test-and-set instruction.

2. What do you mean by hit ratio and miss ratio.

3.Draw the block diagram of RAM and ROM chips.

4.Diffrentiate between SRAM and DRAM.

5.Explain about memory hierarchy in computer system.

6. Explain about paging to implement virtual memory.

7. explain about page replacement algorithm in memory organization.

8. Describe about main memory.

9. Differentiate between RAM and ROM.

10. What do you mean by Computer performance?

Part -B (8 marks)

1. Discuss the difference between tightly coupled multiprocessors and loosely coupled

multiprocessors from the viewpoint of hardware organization and programming techniques.

2. How many switch points are there in a crossbar switch network that connects p processors to m

memory modules?

3. Describe the characteristics of Multiprocessor.

4. A computer employs RAM chips of 256 x 8 and ROM chips of 1024 x 8. The computer system

needs 2K bytes of RAM, 4K bytes of ROM, and four interface units, each with four registers. A

memory-mapped 1/0 configuration is used. The two highest-order bits of the address bus are

assigned 00 for RAM, 01 for ROM, and 10 for interface registers. a. How many RAM and

ROM chips axe needed? b. Draw a memory-address map for the system. c. Give the address

range in hexadecimal for RAM, ROM, and interface.

5. Define following terms:

(a) Magnetic disk

(b) Magnetic Tape

6. Explain about Associative Memory in brief.

Part -C (15 marks)

1.How many characters per second can be transmitted over a 1200-baud line in each of the following

modes? (Assume a character code of eight bits.)

(a) Synchronous serial transmission.

(b) Asynchronous serial transmission with two stop bits.

(c) Asynchronous serial transmission with one stop bit

2.Define the term of “locality of reference”. How this concept is used in the design of memory system?

3.Define the following term:

1. set associative mapping

2.Direct mapping

3.Associative Mapping

COMPUTER ORGANISATION & ARCHITECTURE Page 6

Guess Paper 2024

Pa

4. What is cache coherence, and why is it important in shared-memory multiprocessor systems? How

can the problem be resolved with a snoopy cache controller?

5.Explain briefly about type of Inter-processor Arbitration.

6. Explain about Virtual memory in brief.

Prepared by: Neha Sharma.

COMPUTER ORGANISATION & ARCHITECTURE Page 7

You might also like

- Computer Organization & Architecture: Exercises 1Document13 pagesComputer Organization & Architecture: Exercises 1Haseeb Javed100% (1)

- SIEMENS Indirect AdressingDocument7 pagesSIEMENS Indirect Adressinglakolla00No ratings yet

- Control Transfer Instructions and Programming Using 8051 MicrocontrolleDocument72 pagesControl Transfer Instructions and Programming Using 8051 MicrocontrollePujaChaudhuryNo ratings yet

- 2629acomputer ArchitectureDocument15 pages2629acomputer ArchitectureSiddhant Jain SethNo ratings yet

- BSC (H) CSHT II 204 Mid2012 Ddu Assignment IDocument2 pagesBSC (H) CSHT II 204 Mid2012 Ddu Assignment IRavi RanjanNo ratings yet

- CO Previous Year O.UDocument7 pagesCO Previous Year O.UVistasNo ratings yet

- Computer Organization Unit 4 AssignmentDocument4 pagesComputer Organization Unit 4 Assignmentsaiteja1234No ratings yet

- CAO 2021 Assignment QuestionDocument9 pagesCAO 2021 Assignment Questiondawit tadewoseNo ratings yet

- DDCO UPDATED QUESTION BANKttttDocument4 pagesDDCO UPDATED QUESTION BANKttttbrahmareddy.22iseNo ratings yet

- Shivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Document5 pagesShivalik College of Engineering Question Bank Computer Organization B.Tech II Year (IV Semester)Paras TilaraNo ratings yet

- Cao Question BankDocument4 pagesCao Question Banknashikexplore1No ratings yet

- Computer Organization: Sandeep KumarDocument117 pagesComputer Organization: Sandeep KumarGaurav NNo ratings yet

- MCS 012Document4 pagesMCS 012rajatkumar.codingNo ratings yet

- 3165 BCA C 301 COA QBAnkDocument6 pages3165 BCA C 301 COA QBAnkDevipriya RajendranNo ratings yet

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Document4 pages21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RNo ratings yet

- Computer Organization and Architecture (01CE0402) Lab ManualDocument4 pagesComputer Organization and Architecture (01CE0402) Lab ManualrockyNo ratings yet

- Cs2253 Computer Organization and Architecture Question BankDocument10 pagesCs2253 Computer Organization and Architecture Question BankVenkat RamNo ratings yet

- CLSPDocument1 pageCLSPDebabala SwainNo ratings yet

- Question of Unit 3 and 4Document3 pagesQuestion of Unit 3 and 4Ritesh Kumar100% (1)

- B - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012Document2 pagesB - E / B - T E C H (Full-Time) D E G R E E Examinations, April/May 2012krithikgokul selvamNo ratings yet

- E6995ca TutDocument14 pagesE6995ca Tutrabinoss0% (1)

- Co QBDocument6 pagesCo QBHarris ChikunyaNo ratings yet

- Computer Organzation and Architecture Question BankDocument10 pagesComputer Organzation and Architecture Question Bankmichael100% (2)

- Ca Unit 1Document2 pagesCa Unit 1CSETUBENo ratings yet

- Question Bank - M5 To M7Document2 pagesQuestion Bank - M5 To M7Pieter MarkerNo ratings yet

- Unit-I: Sub: Computer Organisation and Architecture Unit Wise Important QuestionsDocument5 pagesUnit-I: Sub: Computer Organisation and Architecture Unit Wise Important QuestionsManju Reddy PalakolluNo ratings yet

- Unit-I / Part-ADocument2 pagesUnit-I / Part-AShyam SundarNo ratings yet

- COA Question PaperDocument2 pagesCOA Question PaperwahidNo ratings yet

- R5310201 Computer OrganizationDocument1 pageR5310201 Computer OrganizationsivabharathamurthyNo ratings yet

- Assignment 2 CSDDocument3 pagesAssignment 2 CSDMeenu Kamboj0% (1)

- BCA 2nd Sem Ass.2018-19Document15 pagesBCA 2nd Sem Ass.2018-19Kumar InfoNo ratings yet

- ArchitectureDocument3 pagesArchitecturesamueljamespeterNo ratings yet

- Se, All Branches. C A - oDocument2 pagesSe, All Branches. C A - oanuragnair377No ratings yet

- Syllabus 2paperDocument5 pagesSyllabus 2paperdev07panchalNo ratings yet

- 134ak - Computer OrganizationDocument2 pages134ak - Computer Organizationsameeksha chiguruNo ratings yet

- Bput CoaDocument2 pagesBput CoaANIKET SAHOONo ratings yet

- COA Sessional - II - 2018 With SolutionsDocument4 pagesCOA Sessional - II - 2018 With SolutionspoonamNo ratings yet

- Assignment 2Document2 pagesAssignment 2Riddhi VekariyaNo ratings yet

- Sheet ThreeDocument4 pagesSheet ThreeRana BadranNo ratings yet

- Coa Question BankDocument19 pagesCoa Question Banksahasneha354No ratings yet

- R07 Set No. 2Document7 pagesR07 Set No. 2Mothilal KaramtothuNo ratings yet

- (WWW - Entrance-Exam - Net) - PTU MCA 3rd Semester Sample Paper 4Document2 pages(WWW - Entrance-Exam - Net) - PTU MCA 3rd Semester Sample Paper 4Mangesh MalvankarNo ratings yet

- coa impDocument2 pagescoa impHemant TankNo ratings yet

- COA Question BankDocument3 pagesCOA Question BankWednesdayNo ratings yet

- CRC of BCA (2) Assignment (Revised Syllabus)Document17 pagesCRC of BCA (2) Assignment (Revised Syllabus)BshrinivasNo ratings yet

- Question Bank For Computer ArchitectureDocument23 pagesQuestion Bank For Computer ArchitecturesuryaNo ratings yet

- NR Set No. 2Document4 pagesNR Set No. 2adddataNo ratings yet

- Anna University QP COADocument3 pagesAnna University QP COAAbirami Satheesh KumarNo ratings yet

- Department of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Document3 pagesDepartment of Computer Science and Engineering (CSE) : Islamic University of Technology (Iut)Manus HumanNo ratings yet

- COA - Question - Bank SEM 4Document9 pagesCOA - Question - Bank SEM 4Patel SarthakNo ratings yet

- CST202 QPDocument2 pagesCST202 QPSreedevi R KrishnanNo ratings yet

- Diploma Examination, 2011: 130. Logic and Distributed Control SystemDocument5 pagesDiploma Examination, 2011: 130. Logic and Distributed Control SystemMuthuLakshmi RajendranNo ratings yet

- R7310201-Computer System OrganizationDocument4 pagesR7310201-Computer System OrganizationsivabharathamurthyNo ratings yet

- Coa Important QuestionsDocument3 pagesCoa Important Questionswhitebox6623No ratings yet

- Unit - IDocument2 pagesUnit - IPranathi NimmuNo ratings yet

- Question Bank CompleteDocument5 pagesQuestion Bank CompleteSaurabh SenNo ratings yet

- Coa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14Document6 pagesCoa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14cofasi3281No ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- MCS-012 J-16Document7 pagesMCS-012 J-16ps34778jNo ratings yet

- Computer Organization Jun 2010Document2 pagesComputer Organization Jun 2010Prasad C MNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- ENT 237 - Midterm 1 - Spring 2019Document7 pagesENT 237 - Midterm 1 - Spring 2019abdullahNo ratings yet

- Last Moment Tuitions MPDocument4 pagesLast Moment Tuitions MPsahilravimali24No ratings yet

- The M68000 Educational Computer BoardDocument13 pagesThe M68000 Educational Computer BoardPanos BriniasNo ratings yet

- Match The Following Questions in MicroprocessorDocument10 pagesMatch The Following Questions in MicroprocessorKuldeep monuNo ratings yet

- Unit-2: Basic Computer Organization and DesignDocument55 pagesUnit-2: Basic Computer Organization and DesignaaNo ratings yet

- Slides Week8 PDFDocument46 pagesSlides Week8 PDFvidhya dsNo ratings yet

- 11 Instruction Set of 8086Document61 pages11 Instruction Set of 8086kingmeno0% (1)

- Perform Subtraction of Two 16Document1 pagePerform Subtraction of Two 16Vaishnavi ChockalingamNo ratings yet

- 8085 Flags+ Add Modes-1Document11 pages8085 Flags+ Add Modes-1RiteshNo ratings yet

- Addressing Modes in 8085 MicroprocessorDocument1 pageAddressing Modes in 8085 MicroprocessorKhairil IhsanNo ratings yet

- 80286Document12 pages80286Dharmanshu Patel100% (1)

- 8086 ProgramingDocument9 pages8086 ProgramingAneel Kumar BhatiaNo ratings yet

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - Question PaperDocument9 pagesEce-Vii-dsp Algorithms & Architecture (10ec751) - Question PaperVinay Nagnath JokareNo ratings yet

- Assemblers: - Two Functions: - Some Features: - Other FeaturesDocument37 pagesAssemblers: - Two Functions: - Some Features: - Other FeaturesSharon ben aharonNo ratings yet

- Practice Assignment 11 Sol 12453Document6 pagesPractice Assignment 11 Sol 12453Baldeep Singh KwatraNo ratings yet

- 5 - 8051 - Chapter 5Document14 pages5 - 8051 - Chapter 5IsmailNo ratings yet

- TAL ProgrammingDocument553 pagesTAL ProgrammingAndre White100% (1)

- Unit-I: - 80386 IntroductionDocument74 pagesUnit-I: - 80386 IntroductionOmkar MarkadNo ratings yet

- CPU Architectures Motorola 68000Document10 pagesCPU Architectures Motorola 68000Nisa RoslanNo ratings yet

- Wa0004Document139 pagesWa0004Sammy HushNo ratings yet

- EC6013-Advanced Microprocessors and MicrocontrollersDocument8 pagesEC6013-Advanced Microprocessors and MicrocontrollerswelcometonceNo ratings yet

- 12f508 509 16f505Document98 pages12f508 509 16f505Leng SovannarithNo ratings yet

- The Z8000 Microprocessor - A Design Handbook PDFDocument323 pagesThe Z8000 Microprocessor - A Design Handbook PDFWolfgangNo ratings yet

- Sistem Mikropemproses & PengawalmikroDocument388 pagesSistem Mikropemproses & Pengawalmikrozahrim100% (1)

- PIC Guide v1.5Document31 pagesPIC Guide v1.5Önder ÖzcanNo ratings yet

- Aduc812: Microconverter Quick Reference GuideDocument2 pagesAduc812: Microconverter Quick Reference GuideFelipe VasconcelosNo ratings yet

- Cha 1Document31 pagesCha 1Asha NaveenNo ratings yet