Professional Documents

Culture Documents

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

Uploaded by

Rajesh BabuCopyright:

Available Formats

You might also like

- TYPE: MAM-880 B : Screw Air CompressorDocument22 pagesTYPE: MAM-880 B : Screw Air CompressorKader SllNo ratings yet

- RS232 CommunicationsDocument37 pagesRS232 CommunicationsNoor Kareem100% (1)

- 604.66.121.00 RM FX-0 0503 EngDocument1,068 pages604.66.121.00 RM FX-0 0503 EngАлексей Миронов50% (2)

- Kohler Engines Accessories Parts CatalogDocument56 pagesKohler Engines Accessories Parts CatalogKevins Small Engine and Tractor ServiceNo ratings yet

- 820-1398 051-6101 Schematic DiagramDocument44 pages820-1398 051-6101 Schematic DiagramDJ0% (1)

- Boundary Scan: Joint Test Action Group (Jtag)Document10 pagesBoundary Scan: Joint Test Action Group (Jtag)anuNo ratings yet

- JTAG TAP ControllerDocument5 pagesJTAG TAP ControllerTanmayKabra100% (1)

- Jtag 1Document12 pagesJtag 1lavanyaNo ratings yet

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- I2c Bus Master PIC 16FXXDocument61 pagesI2c Bus Master PIC 16FXXCamilo A. InfanteNo ratings yet

- Tap ControllerDocument16 pagesTap ControllerMoin PashaNo ratings yet

- Autonomous ManualDocument12 pagesAutonomous ManualVarun ReddyNo ratings yet

- Cdma Reverselink Waveform Generator Fpga For Production Transmit Path TestsDocument9 pagesCdma Reverselink Waveform Generator Fpga For Production Transmit Path Testsxiao zhanNo ratings yet

- App Arm JtagDocument33 pagesApp Arm Jtagcarver_uaNo ratings yet

- MM Assignmemt 3Document7 pagesMM Assignmemt 3ALL ÎÑ ÔÑÈNo ratings yet

- EDN Design Ideas 1998Document166 pagesEDN Design Ideas 1998chag1956100% (4)

- Speed Detector For HighwaysDocument29 pagesSpeed Detector For HighwaysShama MahinNo ratings yet

- 5 JtagDocument64 pages5 Jtagsharad2208No ratings yet

- MP Unit-6 Se-IiDocument51 pagesMP Unit-6 Se-IiNeha KardileNo ratings yet

- Instructions SchedulingDocument26 pagesInstructions SchedulingNishmika PothanaNo ratings yet

- 8 JTAG Unit 8Document19 pages8 JTAG Unit 8nareshNo ratings yet

- MPMC IiiDocument106 pagesMPMC IiiMani Kumar AmarlapudiNo ratings yet

- Controllability and ObservabilityDocument15 pagesControllability and ObservabilityaashishscribdNo ratings yet

- Conexion Backto Back Atraves de Puertos AuxDocument6 pagesConexion Backto Back Atraves de Puertos AuxMario RyesNo ratings yet

- Expt 2Document2 pagesExpt 2Ankit KhandelwalNo ratings yet

- 8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Document7 pages8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Yerson CrespoNo ratings yet

- Module-2: Microcontroller and Embedded SystemsDocument74 pagesModule-2: Microcontroller and Embedded Systemsswethaashok28No ratings yet

- Module-3 ARMProgram Notes.-16857877494142 PDFDocument5 pagesModule-3 ARMProgram Notes.-16857877494142 PDFrockyv9964No ratings yet

- UsartDocument15 pagesUsartsy2024286No ratings yet

- Design of Ieee 1149.1 Tap Controller Ip CoreDocument12 pagesDesign of Ieee 1149.1 Tap Controller Ip CoreCS & ITNo ratings yet

- Ee 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersDocument2 pagesEe 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersAKANSH AGRAWALNo ratings yet

- Part 1Document31 pagesPart 1SarthakGuptaNo ratings yet

- V Dinesh Ap/Ece SCE, TrichyDocument15 pagesV Dinesh Ap/Ece SCE, TrichykadaNo ratings yet

- Registration For Wiki Conference India 2011Document21 pagesRegistration For Wiki Conference India 2011Nitya SiddagangappaNo ratings yet

- Scan ChainDocument10 pagesScan ChainRaunakRajGuptaNo ratings yet

- Intelligent Water Control System Using 8051 (AT89C51) : Project ReportDocument12 pagesIntelligent Water Control System Using 8051 (AT89C51) : Project ReportNadeem AnjumNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- Task Switching:: JMP Call JMP Call Iret JMP Call IretDocument19 pagesTask Switching:: JMP Call JMP Call Iret JMP Call IretAshish PatilNo ratings yet

- MPMC UNIT 1 OwnDocument35 pagesMPMC UNIT 1 OwnchintuNo ratings yet

- Microprogram ProgramingDocument95 pagesMicroprogram Programingpoojasree27022003No ratings yet

- SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)Document61 pagesSJB Institute of Technology: CO & ARM Microcontrollers (21EC52)rohitrajww4No ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesDocument22 pagesIEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesYadav RaviNo ratings yet

- KGP RISC DocumentationDocument6 pagesKGP RISC DocumentationAbhishek TarunNo ratings yet

- How To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardDocument7 pagesHow To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardShahzad SaleemNo ratings yet

- 8085 Processor Unit I: Mr. S. VinodDocument52 pages8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNo ratings yet

- ADS8412 As A Serial ADC - ALTERA PDFDocument11 pagesADS8412 As A Serial ADC - ALTERA PDFhieuhuech1No ratings yet

- Embedded System Design Using Arduino 18ECO108J: Unit IvDocument53 pagesEmbedded System Design Using Arduino 18ECO108J: Unit IvHow MeanNo ratings yet

- Boundary Scan ArchitectureDocument6 pagesBoundary Scan ArchitectureHARISH DAMARLANo ratings yet

- Jtag PDFDocument22 pagesJtag PDFamitwangoo0% (1)

- 3.7 Timer/counter 8253/8254Document15 pages3.7 Timer/counter 8253/8254skarthikmtechNo ratings yet

- Lectures Section 3 ModifiedDocument73 pagesLectures Section 3 ModifiedcoventryUkNo ratings yet

- The 8086 Microprocessor Architecture: (8086 Datasheet)Document31 pagesThe 8086 Microprocessor Architecture: (8086 Datasheet)Feyisa BekeleNo ratings yet

- 15 - Chepter 6Document9 pages15 - Chepter 6vshalshethNo ratings yet

- Boundary Scan TesterDocument5 pagesBoundary Scan Testerrohitsingh2909No ratings yet

- Lab 7 UART DesignDocument6 pagesLab 7 UART Designaditya220No ratings yet

- Altair8800TheoryOperation 1975Document26 pagesAltair8800TheoryOperation 1975Alfredo Meurer JuniorNo ratings yet

- Nota de Aplicacion - PicoPower BasicsDocument7 pagesNota de Aplicacion - PicoPower Basicsgusti072No ratings yet

- Mm-Assignmemt-4 2Document9 pagesMm-Assignmemt-4 2Creative NKSNo ratings yet

- Power SequencerDocument31 pagesPower SequencerVenkatGollaNo ratings yet

- Encoders, Decoders: Mux, Demux & Data BusesDocument63 pagesEncoders, Decoders: Mux, Demux & Data BusesOkwir BenardNo ratings yet

- Presented by Abhilasha KalmeghDocument15 pagesPresented by Abhilasha KalmeghSuyash Sanjay SrivastavaNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- LLDDocument21 pagesLLDMohammed MhannaNo ratings yet

- CENELEC Octombrie 2020Document2 pagesCENELEC Octombrie 2020Thomas AndersenNo ratings yet

- Catchphrase Words Household Items PDFDocument2 pagesCatchphrase Words Household Items PDFPRISCILLA SIM CHOOI HAR MoeNo ratings yet

- Can Filler Machine Safety Example From EgyptDocument9 pagesCan Filler Machine Safety Example From EgyptKurowo BrummbarNo ratings yet

- Mokveld-Product Sheet Axial Surge Relief ValveDocument2 pagesMokveld-Product Sheet Axial Surge Relief Valveจตุพล กมลเลิศNo ratings yet

- Pradeepkumar SDocument2 pagesPradeepkumar SIraj ChennaiNo ratings yet

- HB959202000 (J) A30 Excitation ControllerDocument133 pagesHB959202000 (J) A30 Excitation ControllerRamakrishna100% (2)

- KTM Race On 3.0 enDocument32 pagesKTM Race On 3.0 enStanescu MarianNo ratings yet

- TCL-IR-FGP-DS-001-Datasheet For Roots Blower-20230616Document1 pageTCL-IR-FGP-DS-001-Datasheet For Roots Blower-20230616Behzad NazariNo ratings yet

- HGD-2000 Catalog V1.2Document1 pageHGD-2000 Catalog V1.2Dewytt Jhordan Cordoba CubillosNo ratings yet

- DrillingDocument51 pagesDrillingaraz_1985100% (1)

- ABB Aplication Notes - Fuses ParallelDocument24 pagesABB Aplication Notes - Fuses Paralleljulio_nunes21No ratings yet

- PO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD PanelDocument12 pagesPO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD Panelamir rudinNo ratings yet

- WiD Pricelist 2021Q4Document32 pagesWiD Pricelist 2021Q4Shashi Mae BonifacioNo ratings yet

- Kitz - Pneumatic ActuatorsDocument24 pagesKitz - Pneumatic ActuatorsdadangNo ratings yet

- 1998-2002 Honda Accord Headlights Replacement: Written By: Miroslav DjuricDocument9 pages1998-2002 Honda Accord Headlights Replacement: Written By: Miroslav DjuricJesus MezaNo ratings yet

- Up QuizDocument2 pagesUp QuizJayesh NarayanNo ratings yet

- PLC Presentation NewDocument27 pagesPLC Presentation NewPrittam Kumar JenaNo ratings yet

- MotorDocument45 pagesMotorVikash YadavNo ratings yet

- Mtu ModbusDocument6 pagesMtu ModbusOrhan DenizliNo ratings yet

- 15 ZF Rear Cover PDFDocument57 pages15 ZF Rear Cover PDFbelchior alvaro100% (1)

- PA330Document3 pagesPA330HoàngTrầnNo ratings yet

- English - EnerSolis Interface Cards User's Manual - 192321462004000Document4 pagesEnglish - EnerSolis Interface Cards User's Manual - 192321462004000Abdelwhab ElsaftyNo ratings yet

- RdsoDocument7 pagesRdsoMrinmy ChakrabortyNo ratings yet

- Bel-Art Colorimeters - Klett CatalogDocument2 pagesBel-Art Colorimeters - Klett CatalogEduardo Jiménez SánchezNo ratings yet

- Checklist For Scaffolding: Construction of Srr2-Construction Management ServicesDocument3 pagesChecklist For Scaffolding: Construction of Srr2-Construction Management ServicesChayank TiwariNo ratings yet

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

Uploaded by

Rajesh BabuOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

TDO Involves Only A Single Flip-Flop. This Allows Specific Chips To Be Tested in A S-CN

Uploaded by

Rajesh BabuCopyright:

Available Formats

is selected.

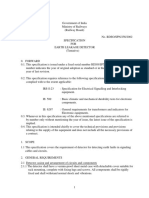

It also determines where the DK will load its value from in the Gapture-lJR state and values will be driven to output pads or core logic. Three instructions are required to be supporr-, *

BYPASSThis

instruction places the bypass register in the DR chain so that the path fi TDO involves only a single flip-flop. This allows specific chips to be tested in a s-cn. without having to shift through the lengthy shift register stages in all the chips. This ir represented with all 1's in the IR.

SAMPLE/PRELOADThis instruction places the boundary scan registers (i.e., at the chip'--the DR chain. In the Capture-DR state, it copies the chip's I/O values into the DRs. T-be scanned out in successive Shift-DR states. New values arc shifted into the DRs, hi. onto the I/O pins yet. EXTESTThis instruction allows for the testing of off-chip circuitry. It is similar r< PRELOAD, but also drives the values from the DRs onto the output pads. By drivr pattern onto the outputs of some chips and checking for that pattern at the input of : -the integrity of connections between chips can be verified. In addition to these instructions, the following are also recommended (others can be defined * IHTESTThis instruction allows for single-step testing of internal circuitry via the bour..:..- * registers. It is similar to EXTEST, but also drives the chip core with signals from the DK than from the input pads. * RUNBISTThis instruction is used to activate internal self-testing procedures within n Note that the instruction encodings are not part of the specification (except that BYPASS is . component designer must document what encodings were selected for each instruction. A typical IR bit is shown in Figure 12.26. Observe that it contains two flip-flops. The Clock.? flops of each bit arc connected to form a shift register. They are loaded with a constant value from i input in the Capture-IR state, and then are shifted out in the Shift-IR state while new values arc -r The constant value is user-defined, but must have a 01 pattern in the least significant two bits s< integrity of the scan chain can be verified. In the Update-IR state, the contents of the shift -. copied in parallel to the IR output to load the entire instruction at once.This prevents the IR fror;. tarily having illegal values while new instructions are shifted in. On reset, the IR should be asynchr loaded with an innocuous instruction such as BYPASS that does not interfere with the normal hr h n core logic.

A minimal implementation of a 3-bit control register is shown below. Notice the instruction rdefinitions. This implements the six registers required for a 3-bit instruction. The instruction is dc, produce mode_in, mode_out, and bypass signals to control the data registers, as will be discussed in tresections.

Test Data Registers

f

- Test data registers are used to set the inputs of modules to be tested ynd collect the results of running k. The simplest data register configuration consists of a boundary scan register (passing through all I/O and a bypass register (1 bit long). Figure 12.27 shows a generalized view of the data registers in :;h an internal data register has been added.This register might represent the scan chain within the chip BILBO signature register. Thus, boundary scan elegantly incorporates other built-in test structures. A -tiplexer under the control of the TAP controller selects which data register is routed to the TDO pin. '">.en internal data registers are added, the 1R decoder must produce extra control signals to select which cc is in the DR chain for a particular instruction.

You might also like

- TYPE: MAM-880 B : Screw Air CompressorDocument22 pagesTYPE: MAM-880 B : Screw Air CompressorKader SllNo ratings yet

- RS232 CommunicationsDocument37 pagesRS232 CommunicationsNoor Kareem100% (1)

- 604.66.121.00 RM FX-0 0503 EngDocument1,068 pages604.66.121.00 RM FX-0 0503 EngАлексей Миронов50% (2)

- Kohler Engines Accessories Parts CatalogDocument56 pagesKohler Engines Accessories Parts CatalogKevins Small Engine and Tractor ServiceNo ratings yet

- 820-1398 051-6101 Schematic DiagramDocument44 pages820-1398 051-6101 Schematic DiagramDJ0% (1)

- Boundary Scan: Joint Test Action Group (Jtag)Document10 pagesBoundary Scan: Joint Test Action Group (Jtag)anuNo ratings yet

- JTAG TAP ControllerDocument5 pagesJTAG TAP ControllerTanmayKabra100% (1)

- Jtag 1Document12 pagesJtag 1lavanyaNo ratings yet

- Why Boundary Scan Needed?Document39 pagesWhy Boundary Scan Needed?srikanth100% (1)

- I2c Bus Master PIC 16FXXDocument61 pagesI2c Bus Master PIC 16FXXCamilo A. InfanteNo ratings yet

- Tap ControllerDocument16 pagesTap ControllerMoin PashaNo ratings yet

- Autonomous ManualDocument12 pagesAutonomous ManualVarun ReddyNo ratings yet

- Cdma Reverselink Waveform Generator Fpga For Production Transmit Path TestsDocument9 pagesCdma Reverselink Waveform Generator Fpga For Production Transmit Path Testsxiao zhanNo ratings yet

- App Arm JtagDocument33 pagesApp Arm Jtagcarver_uaNo ratings yet

- MM Assignmemt 3Document7 pagesMM Assignmemt 3ALL ÎÑ ÔÑÈNo ratings yet

- EDN Design Ideas 1998Document166 pagesEDN Design Ideas 1998chag1956100% (4)

- Speed Detector For HighwaysDocument29 pagesSpeed Detector For HighwaysShama MahinNo ratings yet

- 5 JtagDocument64 pages5 Jtagsharad2208No ratings yet

- MP Unit-6 Se-IiDocument51 pagesMP Unit-6 Se-IiNeha KardileNo ratings yet

- Instructions SchedulingDocument26 pagesInstructions SchedulingNishmika PothanaNo ratings yet

- 8 JTAG Unit 8Document19 pages8 JTAG Unit 8nareshNo ratings yet

- MPMC IiiDocument106 pagesMPMC IiiMani Kumar AmarlapudiNo ratings yet

- Controllability and ObservabilityDocument15 pagesControllability and ObservabilityaashishscribdNo ratings yet

- Conexion Backto Back Atraves de Puertos AuxDocument6 pagesConexion Backto Back Atraves de Puertos AuxMario RyesNo ratings yet

- Expt 2Document2 pagesExpt 2Ankit KhandelwalNo ratings yet

- 8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Document7 pages8-Bit Microcontroller With 1K Bytes In-System Programmable Flash AT90S1200Yerson CrespoNo ratings yet

- Module-2: Microcontroller and Embedded SystemsDocument74 pagesModule-2: Microcontroller and Embedded Systemsswethaashok28No ratings yet

- Module-3 ARMProgram Notes.-16857877494142 PDFDocument5 pagesModule-3 ARMProgram Notes.-16857877494142 PDFrockyv9964No ratings yet

- UsartDocument15 pagesUsartsy2024286No ratings yet

- Design of Ieee 1149.1 Tap Controller Ip CoreDocument12 pagesDesign of Ieee 1149.1 Tap Controller Ip CoreCS & ITNo ratings yet

- Ee 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersDocument2 pagesEe 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersAKANSH AGRAWALNo ratings yet

- Part 1Document31 pagesPart 1SarthakGuptaNo ratings yet

- V Dinesh Ap/Ece SCE, TrichyDocument15 pagesV Dinesh Ap/Ece SCE, TrichykadaNo ratings yet

- Registration For Wiki Conference India 2011Document21 pagesRegistration For Wiki Conference India 2011Nitya SiddagangappaNo ratings yet

- Scan ChainDocument10 pagesScan ChainRaunakRajGuptaNo ratings yet

- Intelligent Water Control System Using 8051 (AT89C51) : Project ReportDocument12 pagesIntelligent Water Control System Using 8051 (AT89C51) : Project ReportNadeem AnjumNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- Task Switching:: JMP Call JMP Call Iret JMP Call IretDocument19 pagesTask Switching:: JMP Call JMP Call Iret JMP Call IretAshish PatilNo ratings yet

- MPMC UNIT 1 OwnDocument35 pagesMPMC UNIT 1 OwnchintuNo ratings yet

- Microprogram ProgramingDocument95 pagesMicroprogram Programingpoojasree27022003No ratings yet

- SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)Document61 pagesSJB Institute of Technology: CO & ARM Microcontrollers (21EC52)rohitrajww4No ratings yet

- QL ServiceManualDocument98 pagesQL ServiceManualOscar Arthur KoepkeNo ratings yet

- IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesDocument22 pagesIEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesYadav RaviNo ratings yet

- KGP RISC DocumentationDocument6 pagesKGP RISC DocumentationAbhishek TarunNo ratings yet

- How To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardDocument7 pagesHow To Implement DSP Algorithms Using The Xilinx Spartan 3E Starter BoardShahzad SaleemNo ratings yet

- 8085 Processor Unit I: Mr. S. VinodDocument52 pages8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNo ratings yet

- ADS8412 As A Serial ADC - ALTERA PDFDocument11 pagesADS8412 As A Serial ADC - ALTERA PDFhieuhuech1No ratings yet

- Embedded System Design Using Arduino 18ECO108J: Unit IvDocument53 pagesEmbedded System Design Using Arduino 18ECO108J: Unit IvHow MeanNo ratings yet

- Boundary Scan ArchitectureDocument6 pagesBoundary Scan ArchitectureHARISH DAMARLANo ratings yet

- Jtag PDFDocument22 pagesJtag PDFamitwangoo0% (1)

- 3.7 Timer/counter 8253/8254Document15 pages3.7 Timer/counter 8253/8254skarthikmtechNo ratings yet

- Lectures Section 3 ModifiedDocument73 pagesLectures Section 3 ModifiedcoventryUkNo ratings yet

- The 8086 Microprocessor Architecture: (8086 Datasheet)Document31 pagesThe 8086 Microprocessor Architecture: (8086 Datasheet)Feyisa BekeleNo ratings yet

- 15 - Chepter 6Document9 pages15 - Chepter 6vshalshethNo ratings yet

- Boundary Scan TesterDocument5 pagesBoundary Scan Testerrohitsingh2909No ratings yet

- Lab 7 UART DesignDocument6 pagesLab 7 UART Designaditya220No ratings yet

- Altair8800TheoryOperation 1975Document26 pagesAltair8800TheoryOperation 1975Alfredo Meurer JuniorNo ratings yet

- Nota de Aplicacion - PicoPower BasicsDocument7 pagesNota de Aplicacion - PicoPower Basicsgusti072No ratings yet

- Mm-Assignmemt-4 2Document9 pagesMm-Assignmemt-4 2Creative NKSNo ratings yet

- Power SequencerDocument31 pagesPower SequencerVenkatGollaNo ratings yet

- Encoders, Decoders: Mux, Demux & Data BusesDocument63 pagesEncoders, Decoders: Mux, Demux & Data BusesOkwir BenardNo ratings yet

- Presented by Abhilasha KalmeghDocument15 pagesPresented by Abhilasha KalmeghSuyash Sanjay SrivastavaNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- LLDDocument21 pagesLLDMohammed MhannaNo ratings yet

- CENELEC Octombrie 2020Document2 pagesCENELEC Octombrie 2020Thomas AndersenNo ratings yet

- Catchphrase Words Household Items PDFDocument2 pagesCatchphrase Words Household Items PDFPRISCILLA SIM CHOOI HAR MoeNo ratings yet

- Can Filler Machine Safety Example From EgyptDocument9 pagesCan Filler Machine Safety Example From EgyptKurowo BrummbarNo ratings yet

- Mokveld-Product Sheet Axial Surge Relief ValveDocument2 pagesMokveld-Product Sheet Axial Surge Relief Valveจตุพล กมลเลิศNo ratings yet

- Pradeepkumar SDocument2 pagesPradeepkumar SIraj ChennaiNo ratings yet

- HB959202000 (J) A30 Excitation ControllerDocument133 pagesHB959202000 (J) A30 Excitation ControllerRamakrishna100% (2)

- KTM Race On 3.0 enDocument32 pagesKTM Race On 3.0 enStanescu MarianNo ratings yet

- TCL-IR-FGP-DS-001-Datasheet For Roots Blower-20230616Document1 pageTCL-IR-FGP-DS-001-Datasheet For Roots Blower-20230616Behzad NazariNo ratings yet

- HGD-2000 Catalog V1.2Document1 pageHGD-2000 Catalog V1.2Dewytt Jhordan Cordoba CubillosNo ratings yet

- DrillingDocument51 pagesDrillingaraz_1985100% (1)

- ABB Aplication Notes - Fuses ParallelDocument24 pagesABB Aplication Notes - Fuses Paralleljulio_nunes21No ratings yet

- PO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD PanelDocument12 pagesPO-2033C LCD Panel Controller Board Support TTL & LVDS Panel For 4.3" 22" Digital LCD Panelamir rudinNo ratings yet

- WiD Pricelist 2021Q4Document32 pagesWiD Pricelist 2021Q4Shashi Mae BonifacioNo ratings yet

- Kitz - Pneumatic ActuatorsDocument24 pagesKitz - Pneumatic ActuatorsdadangNo ratings yet

- 1998-2002 Honda Accord Headlights Replacement: Written By: Miroslav DjuricDocument9 pages1998-2002 Honda Accord Headlights Replacement: Written By: Miroslav DjuricJesus MezaNo ratings yet

- Up QuizDocument2 pagesUp QuizJayesh NarayanNo ratings yet

- PLC Presentation NewDocument27 pagesPLC Presentation NewPrittam Kumar JenaNo ratings yet

- MotorDocument45 pagesMotorVikash YadavNo ratings yet

- Mtu ModbusDocument6 pagesMtu ModbusOrhan DenizliNo ratings yet

- 15 ZF Rear Cover PDFDocument57 pages15 ZF Rear Cover PDFbelchior alvaro100% (1)

- PA330Document3 pagesPA330HoàngTrầnNo ratings yet

- English - EnerSolis Interface Cards User's Manual - 192321462004000Document4 pagesEnglish - EnerSolis Interface Cards User's Manual - 192321462004000Abdelwhab ElsaftyNo ratings yet

- RdsoDocument7 pagesRdsoMrinmy ChakrabortyNo ratings yet

- Bel-Art Colorimeters - Klett CatalogDocument2 pagesBel-Art Colorimeters - Klett CatalogEduardo Jiménez SánchezNo ratings yet

- Checklist For Scaffolding: Construction of Srr2-Construction Management ServicesDocument3 pagesChecklist For Scaffolding: Construction of Srr2-Construction Management ServicesChayank TiwariNo ratings yet