Professional Documents

Culture Documents

Digital Electronics Exam Paper

Digital Electronics Exam Paper

Uploaded by

swarnahansOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Electronics Exam Paper

Digital Electronics Exam Paper

Uploaded by

swarnahansCopyright:

Available Formats

B.

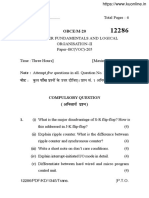

Tech 3rd sem Digital Electronics Time : 3hrs Sub Code:EE-204-F Max Marks:100

Note: Attempt five question.Q.no.1 is compulsory and one question from each of four section. Assume any missing data.

1. (a) Realize the following using Universal Gates

5

(i)

AND Gate (ii) Ex-OR Gate (iii) NOT Gate (iv) OR Gate (b) Define Combinational Ckt. Give example also. (c) Simplify (i) F= A(B+C)+BC + AC (ii) F =A(B+C) +AB +C(A+B)

2 2 (d) Give Truth Table for: 3 (i) S-R Flip-Flop (ii) J-K Flip-Flop (iii) T Flip-Flop (e) What are various Use of Multiplexers? Difference between Decoder and D-MUX. 2 (f) Differentiate b/w 3 (i) Latch and Flip-Flop (ii) Counters and Registers (iii) Race condition in Flip-Flop (iv) (g) Convert (111001001.100101)2 = ( )8 = ( )H 3

Section -A

1. (a)Simplify the given function using K-Map Method

10 F =m (0,2,3,5,7,11,12,13) F = ABC+ACD+BC+ABD+ABCD F = (AC+ ACD)(AD+AC+BC) (b) Explain Error detecting and correcting code in details. 10 3. (a) Solve using Quine McClusky Method 10 F = M(0,3,5,7,9,12,15) and realize using NAND gate. (b) (i) Add -12210 and +65 10using 2s complement 10 (ii) Multiply 4.752 by 3.6252 (iii) Divide 502 by 52 (iv) convert 20046 to 9s and 10s complement (v) convert 73254 to radix 5

Section B

2. (a)Show how 16:1 MUX can be obtained by 4:1 MUX .Design Full Adder with MUX.

10 (b) Explain Full Subtractor. Draw it using H/A. 10

3. (a)What is meant by Encoders? Explain priority Encoders in detail.

10

(b) Design BCD to X-3Code converter. OR Magnitude Comparator 10

Section C

4. (a) What are Counters ? How we use them in digital System? Design MOD-8

Ripple counter. 10 (b) Design Decade synchronous counter using J-K Flip-Flop. 10

5. (a)Explain serial in parallel out and parallel in serial out shift registers using D-flip-

flop. Also explain its different applications. 10 (b) Convert J-K flip-flop into D flip-flop and J-K to T flip flop. 10

Section D

6. (a)What is Race free state assignment? Also explain Hazards in detail.

10 (b) Design a asynchronous sequential logic circuit for the given fig 10

8. Write a short note on the following 20 (i) Half Adder using PLA (ii) ASMs (iii)Reduction of states (iv) RAM and ROM

You might also like

- Digital Paper1Document5 pagesDigital Paper1Iyyakutti GanapathiNo ratings yet

- CS302 - Analog and DigitalDocument5 pagesCS302 - Analog and DigitalGaitonde GaneshNo ratings yet

- Ece DLD Set IiDocument2 pagesEce DLD Set IikisnamohanNo ratings yet

- Acseh0304 (DLD) 2Document5 pagesAcseh0304 (DLD) 2yt608118No ratings yet

- DPSDDocument24 pagesDPSDdigital1206No ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- LDCA Previous Year PaperDocument4 pagesLDCA Previous Year Paperflipkart6392No ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- STLD PDFDocument2 pagesSTLD PDFANUPAMA PonnuNo ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- Dlda 2Document2 pagesDlda 2Manoj NaikNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat NoFack AccountNo ratings yet

- Sathyabama: Register NumberDocument3 pagesSathyabama: Register NumberBoopalanElumalaiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- 2018 Winter DTE 3I - Q - 22320 - CODocument4 pages2018 Winter DTE 3I - Q - 22320 - CO14adisunnyNo ratings yet

- Bca 201 2022 25072022Document2 pagesBca 201 2022 25072022Nitimoy MondalNo ratings yet

- Ecs-301 Digital Logic Design 2010-11Document4 pagesEcs-301 Digital Logic Design 2010-11Satyedra MauryaNo ratings yet

- Sample Question Paper Digital Techniques PDFDocument5 pagesSample Question Paper Digital Techniques PDFAshutosh PatilNo ratings yet

- CS 2202 - Digital Principles and Systems Design PDFDocument3 pagesCS 2202 - Digital Principles and Systems Design PDFvelkarthi92No ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Sub. Code 11: May 2020 Arrear ExaminationDocument2 pagesSub. Code 11: May 2020 Arrear ExaminationSakthiNo ratings yet

- Digital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesDigital Systems Design: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- Digital Logic Design TutorialDocument10 pagesDigital Logic Design TutorialShadab IrfanNo ratings yet

- Digital Systems Design (Ecen 2002)Document2 pagesDigital Systems Design (Ecen 2002)Vikash KumarNo ratings yet

- Third Homework AssignmentDocument4 pagesThird Homework AssignmentTara Shankar ChakrabortyNo ratings yet

- Bcom 2 Sem BC Computer Fundamentals and Logical Organisation 2 12286 2020Document6 pagesBcom 2 Sem BC Computer Fundamentals and Logical Organisation 2 12286 2020Ankit VermaNo ratings yet

- DPSD Nov 2011 - Reg 2008Document3 pagesDPSD Nov 2011 - Reg 2008sububillaNo ratings yet

- Bca 101Document4 pagesBca 101Avirup ShomeNo ratings yet

- 9A04306 Digital Logic DesignDocument4 pages9A04306 Digital Logic DesignsivabharathamurthyNo ratings yet

- DPSDDocument16 pagesDPSDDhilip PrabakaranNo ratings yet

- Ece Question PapaerDocument4 pagesEce Question PapaerAbhinavRahaNo ratings yet

- Fybsc-It Sem1 de Apr19Document2 pagesFybsc-It Sem1 de Apr19faiyaz pardiwalaNo ratings yet

- 2022 Dec. ECT203-CDocument2 pages2022 Dec. ECT203-CAthul RamNo ratings yet

- Question Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-ADocument3 pagesQuestion Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-AmohanaNo ratings yet

- 08ab303 - Digital Logic CircuitsDocument3 pages08ab303 - Digital Logic CircuitsChandru RamaswamyNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversitymtbhoyeNo ratings yet

- Nov Dec 2013Document6 pagesNov Dec 2013abdnazar2003No ratings yet

- Introduction To Digital Design & Digital Logic FddsDocument3 pagesIntroduction To Digital Design & Digital Logic FddsMahima MohapatraNo ratings yet

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesDocument12 pagesEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PNo ratings yet

- DigitalDocument2 pagesDigitalSahil SharmaNo ratings yet

- EC2203 Digital Electronics Question BankDocument16 pagesEC2203 Digital Electronics Question BankSophiaKaviNo ratings yet

- R07 Set No. 2Document8 pagesR07 Set No. 2Samiullah MohammedNo ratings yet

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- Digital Circuits and Logic DesignDocument6 pagesDigital Circuits and Logic DesignSharukh BujjiNo ratings yet

- QuestionBank 15012019Document14 pagesQuestionBank 15012019Mohammed RafaatNo ratings yet

- Adobe Scan 14 Nov 2021Document3 pagesAdobe Scan 14 Nov 2021Parag RaoNo ratings yet

- 2012 December UGC NET Paper IIIDocument16 pages2012 December UGC NET Paper IIIrajasekaranvgNo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- FAQs - CS1202 Digital Principles and System DesignDocument13 pagesFAQs - CS1202 Digital Principles and System DesignsridharanchandranNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Boolean Circuit Rewiring: Bridging Logical and Physical DesignsFrom EverandBoolean Circuit Rewiring: Bridging Logical and Physical DesignsNo ratings yet