Professional Documents

Culture Documents

C CCC CCC C CC C C

C CCC CCC C CC C C

Uploaded by

Md Rizwan AhmadOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

C CCC CCC C CC C C

C CCC CCC C CC C C

Uploaded by

Md Rizwan AhmadCopyright:

Available Formats

DESIGN OF ALU OF THE 8086 MICROPROCESSOR USING VHDL.

Project Synopsis

Submitted in Partial Fulfilment of the Requirements for the Degree of

BACHELOR OF TECHNOLOGY

in

ELECTRONICS & COMMUNICATION ENGINEERING (EC-1)

By

KUNDAN KUMAR (Roll no.-0800114038)

MD RIZWAN AHMAD (Roll no.-0800114048) DENIS KUMAR (Roll no.-0800114025) ADIL MASOOD(Roll no.-0800114007)

Under the guidance of

Ms Tarana Afrin Chandel

(ASST. PROFESSOR)

DEPT. OF ELECTRONICS & COMMUNICATION ENGINEERING

INTEGRAL UNIVERSITY

KURSI ROAD, LUCKNOW (U.P.)

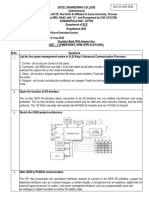

TITLE-: DESIGN OF ALU OF 8086 MICROPROCESSOR USING VHDL. OBJECTIVE-: ALUs can be built in so many ways with wide specifications and since the objective of the class project is to learn the basic of VLSI design, the specifications of the ALU were relaxed. The main objective of the project is to have a working ALU that performs different arithmetic and logic functions for all possible combinations of the inputs. The speed of ALU was not an issue and we wanted it to run at low power.

INTRODUCTION

Digital design is an amazing and very broad field. The applications of digital design are present in our daily life, including Computers, calculators, video cameras etc. In fact, there will be always need for high speed and low power digital products which makes digital design a future growing business. ALU (Arithmetic logic unit) is a critical component of a microprocessor and is the core component of central processing unit. Furthermore, it is the heart of the instruction execution portion of every computer. ALUs comprise the combinational logic that implements logic operations, such as AND and OR, and arithmetic operations, such as ADD and SUBTRACT. This project includes the programming of an 16 bit ALU in VHDL language. VHDL basically is a hardware description language and used to make ASIC Ic and FPGA. In order to stimulate the program you will require two software that are Xilinx and Modelsim. ALU is basically a arithmetic and logic unit that does all logic and arithmetic operations inside the microprocessor.

PROPOSED WORK DESCRIPTION-: Arithmetic logic unit-:

In computing, an arithmetic logic unit (ALU) is a digital circuit that performs arithmetic and logical operations. The ALU is a fundamental building block of the central processing unit (CPU) of a computer, and even the simplest microprocessors contain one for purposes such as maintaining timers. The processors found inside modern CPUs and graphics processing units (GPUs) accommodate very powerful and very complex ALUs; a single component may contain a number of ALUs. Mathematician John von Neumann proposed the ALU concept in 1945, when he wrote a report on the foundations for a new computer called the EDVAC. Research into ALUs remains an important part of computer science, falling under Arithmetic and logic structures in the ACM Computing Classification System.

1. 16 bit edge triggered register:(10%)

Registers are important modules in a synchronized circuit design. Write a 16 bit positive edge triggered register module. It has an a synchronized reset.

INPUT/ OUTPUT PIN DEFINATION-:

Property D CLK RESET Input Input Input Width(bits) 16 1 1 Active low synchronized reset Output 16-bit number Input 16-bit Number

Input

16

2.pipelined ALU design:(90%)

ALU(arithmetic logic unit) is the heart of a MIPS CPU. We will implement a basic ALU in this lab. The following picture is the block diagram of our 16-bit ALU:

IN/OUT PIN DEFINITION:

VHDL: The language

VHDL basically is a hardware description language and used to make ASIC Ic and FPGA. In order to stimulate the program you will require two software that are Xilinx and Modelsim. An entity declaration, or entity, combined with architecture or body constitutes a VHDL model. VHDL calls the entity-architecture pair a design entity. By describing alternative architectures for an entity, we can configure a VHDL model for a specific level of investigation. The entity contains the interface description common to the alternative architectures. It communicates with other entities and the environment through ports and generics. Generic information particularizes an entity by specifying environment constants such as register size or delay value.

Features of 8086 Microprocessor

1) 8086 has 16-bit ALU; this means 16-bit numbers are directly processed by 8086.

2) It has 16-bit data bus, so it can read data or write data to memory or I/O ports either 16 bits or 8 bits at a time. 3) It has 20 address lines, so it can address up to 220 i.e. 1048576 = 1Mbytes of memory (words i.e. 16 bit numbers are stored in consecutive memory locations). Due to the 1Mbytes memory size multiprogramming is made feasible as well as several multiprogramming features have been incorporated in 8086 design. 4) 8086 includes few features, which enhance multiprocessing capability (it can be used with math coprocessors like 8087, I/O processor 8089 etc. 5) Operates on +5v supply and single phase (single line) clock frequency.(Clock is generated by separate peripheral chip 8284). 6) 8086 comes with different versions. 8086 runs at 5 MHz, 8086-2 runs at 8 MHz, 8086-1 runs at 10 MHz. 7) It comes in 40-pin configuration with HMOS technology having around 20,000 transistors in its circuitry. 8) It has multiplexed address and data bus like 8085 due to which the pin count is reduced considerably.9) Higher Throughput (Speed)(This is achieved by a concept called pipelining).

Physical and electrical specifications:

Physical and electr ical specif icat ion : s

2.1. TECHNOLOGY: The design is to be implemented in a 0.25 m CMOS process with 5 metal layers You should use only 4 metal layers for the adder design. The SPICE technology is in the g25.mod file. 2.2. POWER SUPPLY: You are free to choose any supply voltage and logic swing up to 2.5 V. Make sure that you use the appropriate model when you perform any hand analysis. 2.3. PERFORMANCE METRIC: The propagation delay for static CMOS design is defined as the time interval between the 50% transition point of the inputs and the 50% point of the worst-case output signal. 2.4. AREA: The area is defined as the smallest rectangular box that can be drawn around the design. Since the ALU must interface with the cache, all of the row-matched inputs must be accessible from the left side of the design, in row-address order. In the first phase of the project, you should make area estimations based on the total transistor width and the wiring complexity. An expression for prediction of the area will be provided on the web page. 2.5. Each bit slice in the adder should accommodate 6 metal-5 busses and is 24 metal-1 tracks wide. Other circuits in the data path set this constraint. 2.5. NAMING CONVENTIONS: The input operands of the adder are named A<15:0> and B<15:0>. The output is SUM<16:0>, where SUM<16> is the carry out bit. 2.6. REGISTERS: The registers will be specified in the phase 4. 2.7. CLOCKS: The adder design is combinational, so there should be no global clock in project phases 1-3. If you choose to use dynamic logic, you are permitted a precharge/evaluate clock, but the result must become available after ONE evaluate phase (no pipelined logic). Remember that the load capacitance of the clock should be included in the energy analysis. 2.8. VOH, VOL, NOISE MARGINS: You are free to choose your logic swing. The noise margins should be at least 10% of the voltage swing. Test this by computing the VTC between one of the inputs and the output signals (with the other outputs set to the appropriate values) for a static design. For a dynamic circuit, apply an input signal with a 10% noise value added to the input and observe the outputs. 2.9. RISE AND FALL TIMES: All input signals have rise and fall times of 50 ps. The rise and fall times of the output signals (10% to 90%) should not exceed 200ps.

2.10. LOAD CAPACITANCE: Your adder is driving a 1.6mm long bus with 6 loads evenly distributed. Each capacitive load is equal to the adder input capacitance. Each wire in the bus is 4 wide with 4 spacing in M5. 2.11. INPUT CAPACITANCE: Each input of the adder should not load the previous stage with more than 50fF (less is OK).

You might also like

- DPWH Grouted Riprap DesignDocument24 pagesDPWH Grouted Riprap DesignHUBERT FILOG71% (7)

- PLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingFrom EverandPLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingRating: 4 out of 5 stars4/5 (1)

- 100 Questions OMR SheetDocument1 page100 Questions OMR SheetMd Rizwan Ahmad100% (1)

- 150 Questions OMR SheetDocument1 page150 Questions OMR SheetMd Rizwan Ahmad57% (7)

- Metric Key Way DimensionsDocument1 pageMetric Key Way Dimensionsmuzzamil100% (1)

- Seagull Subscribed ModulesDocument2 pagesSeagull Subscribed ModulesPagan jatarNo ratings yet

- Harsh AlDocument81 pagesHarsh AlSmit VahalkarNo ratings yet

- A Novel Approach On Design and Development of High Resolution (16 Bit) Analog Input/output Module With Hot Swap FacilityDocument10 pagesA Novel Approach On Design and Development of High Resolution (16 Bit) Analog Input/output Module With Hot Swap FacilityInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- RS 485Document51 pagesRS 485mgitecetech100% (1)

- OpenPLC - An Opensource Alternative For AutomationDocument5 pagesOpenPLC - An Opensource Alternative For AutomationThiago Alves100% (1)

- Deld End Sem 5,6Document6 pagesDeld End Sem 5,6The GK TalksNo ratings yet

- VHDL Tutorial-Part 1-Adc-SpiDocument7 pagesVHDL Tutorial-Part 1-Adc-Spihieuhuech1No ratings yet

- Messenger Development Without Internet Using Zigbee TechnologyDocument89 pagesMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyNo ratings yet

- MCES Group ActivityDocument55 pagesMCES Group ActivitykartiksdanNo ratings yet

- IEEE Conference OpenPLCDocument6 pagesIEEE Conference OpenPLCThiago AlvesNo ratings yet

- Interfacing With The ISA BusDocument12 pagesInterfacing With The ISA BusseyfiNo ratings yet

- Assignment Set I (1) UpdateDocument15 pagesAssignment Set I (1) UpdateAshish OjhaNo ratings yet

- Project ReportDocument20 pagesProject ReportPiyush GuptaNo ratings yet

- AC500 PLC BrochureDocument52 pagesAC500 PLC Brochureekspl927No ratings yet

- MP & DSP Lab ManualDocument122 pagesMP & DSP Lab ManualShiva RamNo ratings yet

- RF Based Pick-And-place-robot Use ZigbeeDocument66 pagesRF Based Pick-And-place-robot Use Zigbeesumit_saNo ratings yet

- I2C Interfacing To XC3S400 FPGADocument14 pagesI2C Interfacing To XC3S400 FPGAMahesh BhatkalNo ratings yet

- Asic Implementation of I2c Master Bus Controller Firm Ip CoreDocument13 pagesAsic Implementation of I2c Master Bus Controller Firm Ip CoreAnonymous e4UpOQEPNo ratings yet

- Automatic Speed BreakerDocument69 pagesAutomatic Speed BreakerRohitesh KumarNo ratings yet

- Mca Etc Jdcoem Lab Manual AkiDocument26 pagesMca Etc Jdcoem Lab Manual AkiAshwini MateNo ratings yet

- CGC LAB MPDocument39 pagesCGC LAB MPJames ManningNo ratings yet

- Physics ProjectDocument6 pagesPhysics ProjectAdhithyaNo ratings yet

- Microcontrollers 2017-18 Lab ManualDocument58 pagesMicrocontrollers 2017-18 Lab ManualSUNIL KUMAR100% (1)

- Industrial Security System Using Microcontroller Regulated Power SupplyDocument6 pagesIndustrial Security System Using Microcontroller Regulated Power Supplynaveenraj111No ratings yet

- Computing Machinery: Chapter 10: MicrocontrollersDocument51 pagesComputing Machinery: Chapter 10: MicrocontrollersAkanksha SrivastavaNo ratings yet

- ARM Question Bank Unit - 5Document14 pagesARM Question Bank Unit - 5sakthivelv.eecNo ratings yet

- AC 800PEC Control SystemDocument12 pagesAC 800PEC Control SystemlazcanoferNo ratings yet

- IEEE-488: OriginsDocument8 pagesIEEE-488: OriginsDavid BusieneiNo ratings yet

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDocument84 pages25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraNo ratings yet

- Chandy College of Engineering Mullakkadu Department of Electronics & Communication Engineering EC6711-Embedded Lab ManualDocument43 pagesChandy College of Engineering Mullakkadu Department of Electronics & Communication Engineering EC6711-Embedded Lab ManualAshok KumarNo ratings yet

- Electronics Sem - 4 Gtu SyllabusDocument19 pagesElectronics Sem - 4 Gtu SyllabusKarishma SavNo ratings yet

- 1st Rev Road RaggingDocument22 pages1st Rev Road RaggingElamaruthiNo ratings yet

- Lab 7 UART DesignDocument6 pagesLab 7 UART Designaditya220No ratings yet

- Exploring I2cDocument6 pagesExploring I2cspyeagleNo ratings yet

- Armsravan 140618054148 Phpapp01Document132 pagesArmsravan 140618054148 Phpapp01smganorkarNo ratings yet

- PC To PC Optical Fibre CommunicationDocument7 pagesPC To PC Optical Fibre CommunicationPolumuri LovakumarNo ratings yet

- Devloper BoardDocument82 pagesDevloper Boardpukhraj titreNo ratings yet

- Institute of Engineering and Technology, Alwar, Rajasthan: Wireless Keypad Controlled RobotDocument44 pagesInstitute of Engineering and Technology, Alwar, Rajasthan: Wireless Keypad Controlled RobotTwinkle SinghNo ratings yet

- Embedded System SolveDocument15 pagesEmbedded System SolveAshish OjhaNo ratings yet

- FTM 1201Document28 pagesFTM 1201remelefeleNo ratings yet

- Helmet MiniDocument56 pagesHelmet MiniSumanth VarmaNo ratings yet

- PC Based Oscilloscope Using ArduinoDocument18 pagesPC Based Oscilloscope Using ArduinoATMAKURI S V N ANJANEYA SESHASAINo ratings yet

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- PC To PC OPTICAL FIBRE COMMUNICATIONDocument7 pagesPC To PC OPTICAL FIBRE COMMUNICATIONpallaishashankashekharNo ratings yet

- I2c PaperDocument14 pagesI2c PaperParvinder SinghNo ratings yet

- Project Report On Microcontroller Based Traffic Light ControllerDocument23 pagesProject Report On Microcontroller Based Traffic Light Controllerالموعظة الحسنه chanelNo ratings yet

- Prepaid Energy MeterDocument131 pagesPrepaid Energy Metersatyajit_manna_2100% (1)

- Delayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofDocument13 pagesDelayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofnomadcindrellaNo ratings yet

- PLDTUTORDocument13 pagesPLDTUTORAjay Nath S ANo ratings yet

- DRDODocument21 pagesDRDOAyush AgarwalNo ratings yet

- School of Electrical Engineering: The University of Faisalabad, Faisalabad, PakistanDocument12 pagesSchool of Electrical Engineering: The University of Faisalabad, Faisalabad, PakistanSHAROON SARDAR GHULAMNo ratings yet

- Microprocessor Based TrafficDocument20 pagesMicroprocessor Based TrafficDiptikana MahatoNo ratings yet

- Structures To Set.: On A ADocument4 pagesStructures To Set.: On A ASurya Ganesh PenagantiNo ratings yet

- CapstoneDocument16 pagesCapstoneHarsh ShahNo ratings yet

- Manual ABB CLP AC500 2CDC125002B0205 PDFDocument44 pagesManual ABB CLP AC500 2CDC125002B0205 PDFMarcos AldrovandiNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- Important QuestionDocument4 pagesImportant QuestionMd Rizwan AhmadNo ratings yet

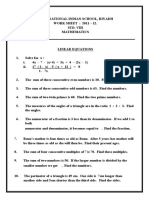

- CBSE Class 8 Linear Equations in One Variable WorksheetDocument2 pagesCBSE Class 8 Linear Equations in One Variable WorksheetMd Rizwan Ahmad75% (8)

- 12th Test PaperDocument5 pages12th Test PaperMd Rizwan AhmadNo ratings yet

- Matrices Worksheet 1Document2 pagesMatrices Worksheet 1Md Rizwan AhmadNo ratings yet

- Coefficient of Restitution (E) : Very Heavy ObjectDocument5 pagesCoefficient of Restitution (E) : Very Heavy ObjectMd Rizwan AhmadNo ratings yet

- 2.2 Equivalence RelationsDocument5 pages2.2 Equivalence RelationsMd Rizwan AhmadNo ratings yet

- Trigonometry-3 Jee Main and AdvancedDocument4 pagesTrigonometry-3 Jee Main and AdvancedMd Rizwan AhmadNo ratings yet

- 03-AC-Solution-Critical, Graphical, Ass. ResonDocument5 pages03-AC-Solution-Critical, Graphical, Ass. ResonMd Rizwan AhmadNo ratings yet

- Magnetic Moment: Classical Concept Review 27Document2 pagesMagnetic Moment: Classical Concept Review 27Md Rizwan AhmadNo ratings yet

- 49/HIS/1 A: MathematicsDocument12 pages49/HIS/1 A: MathematicsMd Rizwan AhmadNo ratings yet

- Practice Paper Math-09Document2 pagesPractice Paper Math-09Md Rizwan AhmadNo ratings yet

- Practice Paper Math-09Document5 pagesPractice Paper Math-09Md Rizwan AhmadNo ratings yet

- Sample Mathematicia XIIDocument49 pagesSample Mathematicia XIIMd Rizwan AhmadNo ratings yet

- 2776NEETZoologyReproductiveSystemTheory - Unlocked Opt PDFDocument21 pages2776NEETZoologyReproductiveSystemTheory - Unlocked Opt PDFMd Rizwan AhmadNo ratings yet

- 211Document31 pages211Md Rizwan AhmadNo ratings yet

- Science SSCDocument6 pagesScience SSCMd Rizwan AhmadNo ratings yet

- 8-St Lines and CirclesDocument2 pages8-St Lines and CirclesMd Rizwan AhmadNo ratings yet

- Fee Structure For Pre-Foundation Career Care Programmes: Academic Session 2017-2018 - Regular Classroom ProgrammeDocument2 pagesFee Structure For Pre-Foundation Career Care Programmes: Academic Session 2017-2018 - Regular Classroom ProgrammeMd Rizwan AhmadNo ratings yet

- Conic SectionDocument22 pagesConic SectionMd Rizwan AhmadNo ratings yet

- ............... Course Applied For: (Use Capital Letters Only)Document1 page............... Course Applied For: (Use Capital Letters Only)Md Rizwan AhmadNo ratings yet

- SAFE Analysis & Design Report C Model Name: Footing Test - FDBDocument26 pagesSAFE Analysis & Design Report C Model Name: Footing Test - FDBTesCospNo ratings yet

- Urban DesignDocument5 pagesUrban DesignBhoomika Khanna100% (1)

- 3d ExperienceDocument19 pages3d ExperiencebrufpotNo ratings yet

- MasoneilanDocument24 pagesMasoneilan62719No ratings yet

- Water Distribution SystemsDocument32 pagesWater Distribution Systemsvishwas gowdaNo ratings yet

- Hindustan Petroleum Corporation LimitedDocument1 pageHindustan Petroleum Corporation LimitedDinakarSatyaNo ratings yet

- Web Development - Wikipedia, The Free EncyclopediaDocument5 pagesWeb Development - Wikipedia, The Free EncyclopediaJeromeGarcia2013No ratings yet

- Wa250 5Document12 pagesWa250 5Andrea797No ratings yet

- Physics BooksDocument4 pagesPhysics BooksShams ShamsNo ratings yet

- DR650SEL2 Catalogo Partes PDFDocument75 pagesDR650SEL2 Catalogo Partes PDFEderNo ratings yet

- Manual Spin CoaterDocument18 pagesManual Spin CoaterGOWTHAM GUPTHANo ratings yet

- Ahsptmk 2021-Rab Ged, Buah MerahDocument117 pagesAhsptmk 2021-Rab Ged, Buah MerahNATSIR LEWANo ratings yet

- Lab 5-Nguyen The Huu-SE1841Document4 pagesLab 5-Nguyen The Huu-SE1841nguyenthehuu2003No ratings yet

- Student Paperette CompetitionDocument15 pagesStudent Paperette CompetitionFrancis Tanaka MutonhodzaNo ratings yet

- Components of A FlashlightDocument7 pagesComponents of A FlashlightKyleen SabinoNo ratings yet

- Liquid Resistance StarterDocument2 pagesLiquid Resistance Startercostea0028No ratings yet

- Thread Inspection MethodsDocument2 pagesThread Inspection MethodsMohamed AshfaqNo ratings yet

- Peltier Gas Cooler Series ECP® - ECP20 - DataDocument3 pagesPeltier Gas Cooler Series ECP® - ECP20 - DataJ.K. BoermanNo ratings yet

- Thermodynamics Part 4 - EntropyDocument26 pagesThermodynamics Part 4 - EntropyOrangesPlzNo ratings yet

- Create Active Passive 12 CDocument138 pagesCreate Active Passive 12 Cnawab_sharief100% (1)

- Object Oriented Programming: in PythonDocument29 pagesObject Oriented Programming: in PythonJohn mari CadNo ratings yet

- Green Belt Project Documentation 182191KSP9300CDocument45 pagesGreen Belt Project Documentation 182191KSP9300CPrakashRai100% (1)

- SixSigma Introduction (Motorola)Document2 pagesSixSigma Introduction (Motorola)Alex XavierNo ratings yet

- A Brief Introduction To Turbulence: IndiceDocument3 pagesA Brief Introduction To Turbulence: IndiceAndreaNo ratings yet

- How To Edit A Linux Live CD ISO in 30 Easy StepsDocument2 pagesHow To Edit A Linux Live CD ISO in 30 Easy StepsAndre SouzaNo ratings yet

- NERS - Requirements V 5 June 2013 - tcm240-247616Document65 pagesNERS - Requirements V 5 June 2013 - tcm240-247616Cristi GrosuNo ratings yet