Professional Documents

Culture Documents

Imp Qpaper

Imp Qpaper

Uploaded by

skmlsuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Imp Qpaper

Imp Qpaper

Uploaded by

skmlsuCopyright:

Available Formats

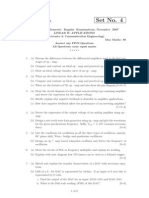

Important questions on OP-AMP and Digital Electronics 1.

(a) Draw the schematic diagram of an ideal inverting OP-AMP with voltage shunt feedback (b) Define CMRR and Slew rate (c) Draw the schematic diagram of practical Integrator (d) What is value of feed factor for a phase shift oscillator? (e) In a regulated power supply the regulation factor (Sv) =0.03 and output resistance (Ro) =0.5. Compute the change in output voltage (Vo) due to input voltage changes of 5 V and load current (IL) variation from 5A to 6A (f) Define a multiplexer and draw the logic block diagram of a 4 to 1 line multiplexer (g) What is 1 bit memory? Draw its logic diagram. (h) Why is the data bus bidirectional? (i) List the four operations commonly performed by the MPU (P). (j) Name two general purpose devices that may be interfaced with the MPU. 2. (a) An amplifier without feedback has the midband voltage gain AVo = 1000. If the reverse transmission factor () = 0.1 and Vs=0.1V, then for the feedback amplifier, compute the voltage gain (AVof ), the difference signal (Vi) and the output voltage (Vo). At some higher frequency the gain of the amplifier (without feedback) has fallen to half of its previous value, so that AV = 500. Then, if Vs remains at 0.1V, calculate the new values of the voltage gain (AVf ), Vi and Vo, and explain the self-regulatory action of the feedback amplifier. (b) Draw the circuit diagram of a dual input emitter coupled differential amplifier (DIFF AMP) and explain why the CMRR for a symmetrical circuit with

resistors Z and Zf

Re .

3. (a) Show that the expression for the closed-loop gain of a practical inverting OP-AMP is given by

AVf = Y/{Y'(1/AV)(Y'+Y+Yi)}

where Ys are admittance corresponding to the Zs (for example Y'=1/Z') and where the voltage gain AV Vo/Vi, taking the loading of Z' into account, is given by

AV= (Av+RoY')/(1+ RoY') Also show that |Av| , leads to |AV| and AVf (Z'/Z)

(b) Why is Re in an emitter coupled DIFF AMP replaced by a constant current source?

4. (a) Sketch the topology for a generalized resonant circuit oscillator, using impedances Z1, Z2, Z3. (b) At what frequency will the circuit oscillate? (c) Under what conditions does the configuration reduce to Colpitts oscillator? A Hartley oscillator? (d) State the frequency -stability criterion for a sinusoidal oscillator. 5. (a) With the help of suitable circuit diagram explain how the following differential equation can be solved using OP-AMP and other essential circuit elements:

(b) Draw the circuit of an OP-AMP differentiator and explain its operation with the help of suitable waveform charts. (c) Explain why the differentiating OP-AMP circuit is not commonly used as compared to their integrating counterpart. 6. (a) List three reasons why an unregulated supply is not good enough for some applications. (a) Consider two 4-bit numbers A and B with B > A. Verify that to subtract A from B it is only required to add B, A, and 1. Sketch the block diagram of a 4-bit subtractor obtained from a full adder and explain its operation. (c) Reduce the following logic expression using K-map technique and realize using logic gates. F(w,x,y,z) =( 0,1,2,4,5,6,8,9,12,13,14) 7. (a) Show that a 4-bit parallel binary adder can be constructed from cascaded full adders. Draw the truth table for a three-input adder and write the Boolean expressions for the Sum and Carry. (b) Define a decoder. How to decode the 4-bit code 1010 (LSB)

d2v/dt2 + K1dv/dt + K2v v1 =0

8. (a) Explain the race-around condition in connection with the J-K FLIP-FLOP and Also describe two methods to overcome this problem. (b) Draw the block-diagram of a four-stage ripple counter. Sketch the waveform at the input and at the output of each FLIP-FLOP for the counter. Explain how this waveform chart is obtained. 9. Draw the labeled functional block diagram of 8085 microprocessor and describe its primary features. 10. (a) Give the list of Instruction set of 8085- addressing modes.

(b) What do you mean by looping, counting and indexing 11. (a) Write an assembly language program to find the largest data byte among a graph of 16 data bytes. (b) Write a program segment to generate a delay of 100ms. Assume the system clock frequency to be 2 MHz.

You might also like

- 7Ps of Toyota InnovaDocument19 pages7Ps of Toyota Innovapankaj pal50% (4)

- GE CT Revolution MaximaDocument16 pagesGE CT Revolution MaximaJorge ArturoNo ratings yet

- Service Training 2005Document76 pagesService Training 2005Heidi Cuevas Venegas100% (1)

- CrazyDocument6 pagesCrazyFlexjob careerNo ratings yet

- PLC Lab ExercisesDocument33 pagesPLC Lab ExercisesShaheerLatif100% (5)

- Ade Question BankDocument7 pagesAde Question BankSonuNo ratings yet

- R09220203 ElectroniccircuitsDocument12 pagesR09220203 ElectroniccircuitsAkramahmedMohammadNo ratings yet

- 313ect06 Ec-IDocument2 pages313ect06 Ec-IramkumarrajaNo ratings yet

- Ec1254 (1) II Ece A Subject 1Document3 pagesEc1254 (1) II Ece A Subject 1Sivakannu GanesanNo ratings yet

- IcappDocument6 pagesIcappSurya TejaNo ratings yet

- Analog Circuits: Time Allotted: 3 Hrs Full Marks: 70Document4 pagesAnalog Circuits: Time Allotted: 3 Hrs Full Marks: 70Vikash KumarNo ratings yet

- 2018 April EE203-D - Ktu QbankDocument2 pages2018 April EE203-D - Ktu QbankFarooq KhandayNo ratings yet

- EC8351-Electronic Circuits IDocument2 pagesEC8351-Electronic Circuits Isyed1188No ratings yet

- Answer Answer All Questions, Each Carries 3 MarksDocument2 pagesAnswer Answer All Questions, Each Carries 3 MarksAjayShankarNo ratings yet

- EEC501Document2 pagesEEC501raviNo ratings yet

- Answer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks.: Reg No.: - Namesheena mNo ratings yet

- A&D2Document2 pagesA&D2pavithramasiNo ratings yet

- Eet205 Analog Electronics, December 2021Document3 pagesEet205 Analog Electronics, December 2021Midun RamkumarNo ratings yet

- EDC - Old Question Papers For Unit 3, 4, 5Document19 pagesEDC - Old Question Papers For Unit 3, 4, 5Deepak SahuNo ratings yet

- ES22101-Q-III-CE BranchDocument3 pagesES22101-Q-III-CE BranchcoolinkenanatamNo ratings yet

- Edlc May 2008Document1 pageEdlc May 2008SwapnilDashputeNo ratings yet

- QP Eee 22 May2010 LdicaDocument6 pagesQP Eee 22 May2010 LdicaHari PrasadNo ratings yet

- 9A04502 Linear IC ApplicationsDocument4 pages9A04502 Linear IC ApplicationssivabharathamurthyNo ratings yet

- IES CONV Electronic Comm. 2000Document11 pagesIES CONV Electronic Comm. 2000gateandiesNo ratings yet

- Sample Paper 4Document2 pagesSample Paper 4saiganesh_49No ratings yet

- B. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Document6 pagesB. Sc. EXAMINATION, 2020: No. of Printed Pages: 06 Roll No. ......................Vishal TanwarNo ratings yet

- 2019 May EE203-F - Ktu QbankDocument2 pages2019 May EE203-F - Ktu QbankFarooq KhandayNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument4 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- IES - Electronics Engineering - Analog Electronic CircuitsDocument71 pagesIES - Electronics Engineering - Analog Electronic CircuitsVishwanath MalakarNo ratings yet

- B. Tech: Roll NoDocument5 pagesB. Tech: Roll NoRavindra KumarNo ratings yet

- 3054 PDFDocument9 pages3054 PDFpadmajasivaNo ratings yet

- Aprilmay 2007Document7 pagesAprilmay 2007Viswa ChaitanyaNo ratings yet

- C1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN MergedDocument18 pagesC1EC01-C1405 - ELECTRONIC CIRCUIT ANALYSIS & DESIGN Mergedchini_naniNo ratings yet

- Edc 3Document10 pagesEdc 329viswa12No ratings yet

- Question Paper Code:: Reg. No.Document5 pagesQuestion Paper Code:: Reg. No.Samraj JebasinghNo ratings yet

- Edlc Dec 2008Document2 pagesEdlc Dec 2008SwapnilDashputeNo ratings yet

- 2-EE-Objective Paper-II-2010 PDFDocument20 pages2-EE-Objective Paper-II-2010 PDFyash97140% (1)

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- EE Con-3Document8 pagesEE Con-3shishirgupta2007No ratings yet

- 9A04502 Linear IC ApplicationsDocument4 pages9A04502 Linear IC ApplicationssivabharathamurthyNo ratings yet

- Graph Sheets May Be Supplied On Demand: Page 1 of 2Document2 pagesGraph Sheets May Be Supplied On Demand: Page 1 of 2sarang acNo ratings yet

- 3 Hours / 100 Marks: Seat NoDocument4 pages3 Hours / 100 Marks: Seat NoSiddhesh P GhadigaonkarNo ratings yet

- First / July: Basic ElectronicsDocument5 pagesFirst / July: Basic ElectronicsHarishNo ratings yet

- Question Paper: A Answer All The QuestionsDocument3 pagesQuestion Paper: A Answer All The QuestionsHarshita GauravNo ratings yet

- R3Fvle: & Etrr - )Document7 pagesR3Fvle: & Etrr - )sarveshNo ratings yet

- R7310403 Linear IC ApplicationsDocument1 pageR7310403 Linear IC ApplicationssivabharathamurthyNo ratings yet

- SVE Society's Bheemanna Khandre Institute of Technology Electronics and Communication Engineering DepartmentDocument2 pagesSVE Society's Bheemanna Khandre Institute of Technology Electronics and Communication Engineering DepartmentsharanbasappaNo ratings yet

- Model Question Paper Power Electronics: Sub code:-06EE45Document3 pagesModel Question Paper Power Electronics: Sub code:-06EE45GuruprasadNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- Analog Electronic Circuit (ECE - 201)Document3 pagesAnalog Electronic Circuit (ECE - 201)Manoj Kumar RNo ratings yet

- 9A04402 Electronic Circuit AnalysisDocument8 pages9A04402 Electronic Circuit AnalysissivabharathamurthyNo ratings yet

- Aprilmay 2009Document8 pagesAprilmay 2009Viswa ChaitanyaNo ratings yet

- Analog Electronics (0500625) SET 1Document8 pagesAnalog Electronics (0500625) SET 1Avinash PandeyNo ratings yet

- Linear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Document8 pagesLinear and Dig Italic Applications Jntu Model Paper WWW Student Yogi Com 100113195343 Phpapp02Ranjith ReddyNo ratings yet

- 2020 FinalDocument3 pages2020 FinalBen ChouNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityRushabh PatelNo ratings yet

- Aec Model Question 2021Document2 pagesAec Model Question 2021Ajay kumar GuptaNo ratings yet

- F Phy143Document2 pagesF Phy143studyzilaNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- EDCDocument28 pagesEDCzuberbashaNo ratings yet

- Edc 7Document8 pagesEdc 729viswa12100% (1)

- ES 201 Basic Electrical and Electronics Engineering II Time Allotted: 3 Full Marks: 70Document4 pagesES 201 Basic Electrical and Electronics Engineering II Time Allotted: 3 Full Marks: 70ud54No ratings yet

- 030070502-Integrated Circuit and Application-QPDocument4 pages030070502-Integrated Circuit and Application-QPARAV PRAJAPATINo ratings yet

- Power System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)From EverandPower System Transient Analysis: Theory and Practice using Simulation Programs (ATP-EMTP)No ratings yet

- PP Emergency Guide PDFDocument6 pagesPP Emergency Guide PDFgilbertomjcNo ratings yet

- ATHEROS AR8236 (١)Document116 pagesATHEROS AR8236 (١)Fahed AlmaktariNo ratings yet

- OCR 104A: Application For Mediation or Hearing - Form ADocument4 pagesOCR 104A: Application For Mediation or Hearing - Form AjohnNo ratings yet

- Use of Bamboo As Housing Material and in Making Various ProductsDocument69 pagesUse of Bamboo As Housing Material and in Making Various ProductsRAHUL100% (2)

- R Air Packers C 071360014 EngDocument7 pagesR Air Packers C 071360014 Enganon_462570989No ratings yet

- United States Court of Appeals, Third CircuitDocument8 pagesUnited States Court of Appeals, Third CircuitScribd Government DocsNo ratings yet

- NomineeDirector Direct From Nominee Director To ClientDocument5 pagesNomineeDirector Direct From Nominee Director To ClientthelegacylcNo ratings yet

- A Study On Customer Preference Towards Chocolates in CoimbatoreDocument5 pagesA Study On Customer Preference Towards Chocolates in Coimbatorekosov28578No ratings yet

- CSC128 - Fundamentals of Computer Problem Solving: Title - Shoe's Inventory SystemDocument16 pagesCSC128 - Fundamentals of Computer Problem Solving: Title - Shoe's Inventory SystemNadhirah AshlahNo ratings yet

- Prosthodontics PonticsDocument16 pagesProsthodontics PonticsLavanya R B100% (1)

- DRC VAT Training CAs Day 1-2Document40 pagesDRC VAT Training CAs Day 1-2iftekharul alam100% (1)

- Assignment of Taxation Management: NTN Procedure Submitted To: Prof. M. MuzaffarDocument4 pagesAssignment of Taxation Management: NTN Procedure Submitted To: Prof. M. MuzaffarfreshynaqviNo ratings yet

- Global Private Equity - JapanDocument16 pagesGlobal Private Equity - JapanabhishaqueNo ratings yet

- Shaft Inspection Using Phased-Array Compared To Other Techniques CINDEDocument21 pagesShaft Inspection Using Phased-Array Compared To Other Techniques CINDEIvanRomanovićNo ratings yet

- GBP Statement: TransactionsDocument2 pagesGBP Statement: Transactions13KARATNo ratings yet

- System of ExcitationDocument20 pagesSystem of ExcitationWesley RibeiroNo ratings yet

- XR70CX: Installing and Operating InstructionsDocument4 pagesXR70CX: Installing and Operating Instructionshassanain_100No ratings yet

- Switching-Controlling Pricelist 2023 WatermarkDocument76 pagesSwitching-Controlling Pricelist 2023 Watermarkcsn BabuNo ratings yet

- OrthoToolKit SF36 Score ReportDocument3 pagesOrthoToolKit SF36 Score ReportbayuNo ratings yet

- Tahalyani2016Document13 pagesTahalyani2016Riston SinagaNo ratings yet

- Shangrila - Grease TrapDocument2 pagesShangrila - Grease TrapJanpull SugasteNo ratings yet

- Gas Metal Arc Welding (GMAW)Document16 pagesGas Metal Arc Welding (GMAW)Akmal Bin Saipul AnuarNo ratings yet

- Ra 8551 Chapter 1Document11 pagesRa 8551 Chapter 1Jayson ampatuanNo ratings yet

- Grab Receipts June 2023Document14 pagesGrab Receipts June 2023Joyce Grace CasasNo ratings yet