Professional Documents

Culture Documents

Flip Flop Sect 2

Flip Flop Sect 2

Uploaded by

Bink BonkCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Flip Flop Sect 2

Flip Flop Sect 2

Uploaded by

Bink BonkCopyright:

Available Formats

Flip-flop

Clock input

Master-Slave Flip-flop

Edge-triggerred Flip-flop

1

Clock input

Flip-flops are made from gated latches (latches with

control input).

The state of a flip-flop is switched by a momentary

change in control input known as clock.

A flip-flop may response to produce output based on 3

types of clock signal:

1)Positive level trigger

2)Positive edge trigger

3)Negative edge trigger.

2

3

Figure of Clock Signals

Positive level response allows changes in the output when the

input changes while the clock pulse stays at logic 1

Problem may occur when more than 1 changes happen at the

input signal and output will keep on changing following the

input signal as long as the trigger signal still stay in positive

level.

This cause confusion and therefore positive level triggering is

less preferred. On the other hand, edge triggering is more

commonly used.

For positive edge response/triggering, the output will change

according to the input only during the positive transition of

trigger signal.

For negative edge response/triggering, the output will

change according to the input only during the negative edge

of trigger signal.

4

Edge-triggered Flip-flop

There are 2 ways to construct an edge triggered flip-

flop:

Master-Slave configuration

Efficient arrangement of gated latch

5

Edge-triggered D flip-flop

D flip-flop is constructed with 2 D latches and an

inverter (Master-Slave)

6

When CLK (clock) is 1, master D latch is enabled

but slave D latch is disabled. Input (D) will be

transferred to Y. Y output will change whenever

input D changes at this condition.

When CLK changes to 0, slave D latch is enabled

but master D latch is disabled. Data at Y will be

transferred to Q.

As a result, this edge-triggered D flip-flop is actually

a negative edge-triggered D flip-flop. (change in the

output during transition from 1 to 0 )

7

Characteristic (next state) equation for D Flip-flop

Q(t+1) = Q* = D

Characteristic (truth, function) table,

8

Edge-triggered D flip-flop using 3 SR latches ,

9

Operation of the D Flip-flop

If D = 0, when CLK becomes 1, R 0, Q 0, flip-

flop is reset. If there are further changes in the

input, R remains as 0. (The flip-flop is locked out).

During D = 0 and CLK return to 0, R 1 but

output remain unchanged (Q = 0).

If D = 1 when CLK becomes 1, S 0, Q 1, flip-

flop is set. If there are further changes in the input,

S remains as 1. (The flip-flop is locked out).

During D = 1 and CLK return to 0, S 1 but

output remain unchanged (Q = 1).

As a result, this edge-triggered D flip-flop is actually

a positive edge-triggered D flip-flop.

10

Graphical symbol for edge D flip-flop.

11

The triangle symbol in

front of C designating

that the flip-flop

responds to edge

triggering

a) Positive edge-

triggered D flip-flop

b) Negative edge-

triggered D flip-flop

Inputs

Comments

1

CLK D

Outputs

1

Q Q

0 SET

0 0 1 RESET

Inputs

Comments

1

CLK D

Outputs

1

Q Q

0 SET

0 0 1 RESET

JK Flip-Flops

JK flip-flop is constructed by using the D flip-flop

and external logic gates.

12

There are 4 operations performed by the JK flip-

flop:

Set output to 1

Reset output to 0

Complement its previous output

Hold its previous o/p

The J input sets the flip-flop output to 1 and the K

input resets the output to 0.

When both J K inputs are 1, the output is the

complement of the previous output.

13

The expression of the circuit (next state equation),

Q* = D = JQ + KQ

The JK flip-flop characteristic table,

14

Inputs

Comments

1

1 1

1

CLK K J

Outputs

1

Q Q

Q

0

Q

0

Q

0

Q

0

0 SET

Toggle

0

0

0

0 0

1

RESET

No change

2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights

Reserved

Floyd, Digital Fundamentals, 10

th

ed

Determine the Q output for the J-K flip-flop,

given the inputs shown.

CLK

Q

K

J

CLK

K

J

Q

Q

Notice that the outputs change on the leading edge of the clock.

Set Toggle Set Latch

T Flip-Flops

The T (toggle) flip-flop is a complementing flip-flop

and can be obtained from a JK flip-flop when inputs J

and K are tied together.

The graphical symbol for T flip-flop ,

16

The expression of the T flip-flop,

Q* = D = TQ + TQ = T Q

The characteristic table,

17

Edge-triggered flip-flop timing matter

3 important timing matter need to be considered while using edge-

triggered flip-flop:

1. Setup time: Minimum time for which the D input must be

maintained at a constant value prior to the occurrence of the

clock transition.

2. Hold time: Minimum time for which the D input must not

change after the application of the positive transition of the

clock.

3. Propagation delay time: The interval time between the trigger

edge and the stabilization of the output to a new state.

Propagation delay of a gate is the average transition-delay time for

the signal to propagate from input to output when the binary

signal changes in value. Usually, propagation delay is measured in

nanoseconds (ns).

18

Direct (asynchronous) inputs

Direct inputs are useful for bringing all flip-flops in a

system to a known starting state prior the clocked

operation

Some flip-flops have asynchronous inputs that are

used to force the flip-flop to a particular state

independent of the clock.

The input that sets the flip-flop to 1 is called preset

or direct set.

The input that clears the flip-flop to 0 is called clear

or direct reset.

19

2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights

Reserved

Floyd, Digital Fundamentals, 10

th

ed

Two such inputs are normally labeled preset (PRE) and clear

(CLR). These inputs are usually active LOW. A J-K flip flop with

active LOW preset and CLR is shown.

CLK

K

J

Q

Q

PRE

CLR

2009 Pearson Education, Upper Saddle River, NJ 07458. All Rights

Reserved

Floyd, Digital Fundamentals, 10

th

ed

Determine the Q output for the J-K flip-flop,

given the inputs shown.

CLK

K

J

Q

Q

PRE

CLR

Set Toggle

Reset

Toggle

Set

Set

Reset

Latch

CLK

K

J

Q

PRE

CLR

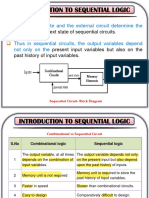

Sequential Logic Circuit Analysis

22

Introduction

The behavior of a synchronous sequential circuit is

determined from the inputs, the outputs and the

states of its flip-flop.

The outputs and the next state are both a function

of the inputs and the present state.

There are 3 methods to analyze a sequential circuit:

state equations, state table and state diagram.

23

State Equations

The behavior of the sequential circuit can be

expressed algebraically in Boolean expressions, which

include the necessary time sequence either directly or

indirectly.

A state equation or transition equation specifies the

next state as a function of the present state and

inputs.

The Boolean expressions for state equations can be

derived directly from the gates that from the

combinational circuit part of the sequential circuit.

24

Consider the example,

25

A* = Ax + Bx

B* = Ax

y = (A+B)x

State Equations:

A(t+1) = A(t)x(t) + B(t)x(t)

B(t+1) = A(t)x(t)

y (t) = (A(t)+B(t))x(t)

Note: Q

D

(t+1) = D(t)

Q

D

(t+1) = A(t+1)

A(t+1) = D(t)

State Table

The time sequence of inputs, outputs and flip-flop

states can be enumerated in a state table or

transition table.

There are 2 forms of state table. The difference is

the number of items in the table.

1

st

form: Table consists of present state, input, next

state and output.

2

nd

form: Table consists of present state, next state

and output.

26

By referring to the earlier example, the format of

the state table for 1

st

form as shown below;

27

A* = Ax + Bx

B* = Ax

y = (A+B)x

By referring to the earlier example, the format of

the state table for 2

nd

form as shown below;.

The input conditions are enumerated under the

next-state and output sections.

28

State Diagram

The information available in a state table can be

represented graphically in the form of a state

diagram.

Example of state diagram is shown below;

29

A state is represented by a circle and the transitions

between states are indicated by directed lines

connecting the circles

The binary number inside each circle identifies the

state of the flip-flops.

The directed lines are labeled with 2 binary numbers

separated by a slash.

The first number gives the input value during the

present state and the number after the slash gives

the output value during the present state with the

given input.

30

31

A* = Ax + Bx

B* = Ax

y = (A+B)x

You might also like

- J Uma ResumeDocument4 pagesJ Uma ResumeAkshay TarteNo ratings yet

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Bosch Me7.1.1 400 Vag 1033Document2 pagesBosch Me7.1.1 400 Vag 1033ddf_dedo100% (1)

- 15CS202 DSD Unit4Document78 pages15CS202 DSD Unit4Siddhant KumarNo ratings yet

- EC 201 Basic Electronics: Tarun Tripathi School of Electronics Engineering KIIT UniversityDocument35 pagesEC 201 Basic Electronics: Tarun Tripathi School of Electronics Engineering KIIT Universityvarun_1992100% (1)

- Flip FlopDocument35 pagesFlip Flopநட்ராஜ் நாதன்No ratings yet

- Unit 10 JK Master SlaveDocument51 pagesUnit 10 JK Master SlaveRennie KawanguNo ratings yet

- Flip FlopsDocument60 pagesFlip FlopsA10-14Rajat KumarNo ratings yet

- Sequential CircuitsDocument53 pagesSequential CircuitsbrsreddyNo ratings yet

- Chapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsDocument20 pagesChapter5: Synchronous Sequential Logic: Lecture2-Study Problems in Latches and Design D Flip-FlopsHamza RiazNo ratings yet

- CSE 1203 Introduction To Sequential Circuits and FFDocument27 pagesCSE 1203 Introduction To Sequential Circuits and FFgbikornoNo ratings yet

- Sequential Circuits: Flip FlopsDocument16 pagesSequential Circuits: Flip FlopsSonam SoniNo ratings yet

- Jkflip FlopDocument27 pagesJkflip FlopUsama NaveedNo ratings yet

- Product-of-Sums Simplification (POS)Document9 pagesProduct-of-Sums Simplification (POS)aregaNo ratings yet

- Logic Design Presentation - Latches & Flip FlopsDocument16 pagesLogic Design Presentation - Latches & Flip FlopsKudzai Russell MutanhaurwaNo ratings yet

- Computer Architecture 1Document39 pagesComputer Architecture 1ARAFAT GaamanNo ratings yet

- CounterDocument22 pagesCounterMahesh MahiNo ratings yet

- EE-221 Chap07 Part-01Document42 pagesEE-221 Chap07 Part-01AliNo ratings yet

- LD5 Mano Ch5Document37 pagesLD5 Mano Ch5Amr HefnyNo ratings yet

- Lecture2 Chapter5 - Study Problems in Latches and Design D Flip-FlopsDocument20 pagesLecture2 Chapter5 - Study Problems in Latches and Design D Flip-FlopsWalrus ProduceNo ratings yet

- Latched, Flip-Flops, and TimersDocument36 pagesLatched, Flip-Flops, and TimersMuhammad Umair AslamNo ratings yet

- UntitledDocument8 pagesUntitledlalita chauhanNo ratings yet

- Module 4Document26 pagesModule 4OKNo ratings yet

- Module-4: Flip-Flops, Registers and CountersDocument111 pagesModule-4: Flip-Flops, Registers and CountersSanchitha GowdaNo ratings yet

- FlipflopsDocument38 pagesFlipflopsajith p pNo ratings yet

- Chapter-6: Sequential Logic Circuit (Latches, Flip-Flop and Counter)Document56 pagesChapter-6: Sequential Logic Circuit (Latches, Flip-Flop and Counter)Bonsa100% (1)

- Digital Design On Digital Works.Document25 pagesDigital Design On Digital Works.nileshchaurasiaNo ratings yet

- Module 5 - Counter Design Problems and Flip-Flops - Oct 8thDocument65 pagesModule 5 - Counter Design Problems and Flip-Flops - Oct 8thRavi CharanNo ratings yet

- Latches, Flip-Flops TimerDocument42 pagesLatches, Flip-Flops TimerUsama AuwalNo ratings yet

- CountersDocument36 pagesCountersA10-14Rajat KumarNo ratings yet

- Chapter 5Document109 pagesChapter 5Amera AdilNo ratings yet

- Unit 4 D-JK Flip FlopsDocument17 pagesUnit 4 D-JK Flip FlopsRongeet SodhiNo ratings yet

- Sequential CircuitsDocument134 pagesSequential CircuitsRajat KumarNo ratings yet

- EET206 M4 Ktunotes - inDocument195 pagesEET206 M4 Ktunotes - inKhaled AlshurmanNo ratings yet

- Synchronous Sequential Ckts by Lakshmi NarayanaDocument30 pagesSynchronous Sequential Ckts by Lakshmi NarayanaMurali Krishna100% (1)

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- Chapter 4-SequentialCircuitsDocument36 pagesChapter 4-SequentialCircuitsnhi.phanngoc.cit21No ratings yet

- cs1104 11Document32 pagescs1104 11N Sandeep KumarNo ratings yet

- Chap - 04-Sequential CircuitsDocument47 pagesChap - 04-Sequential Circuitscharbelkhalil05No ratings yet

- DE Module 03Document20 pagesDE Module 03Rishabh TiwariNo ratings yet

- Sequential Circuits: Latches and Flip-FlopsDocument32 pagesSequential Circuits: Latches and Flip-FlopsRohan BorgalliNo ratings yet

- الانظمة الرقمية ٥ معلومات ست رندDocument14 pagesالانظمة الرقمية ٥ معلومات ست رندaddfgh177No ratings yet

- Notice: Please Change Your Zoom Name To 20/ENG/XXXDocument18 pagesNotice: Please Change Your Zoom Name To 20/ENG/XXXvidsa2002No ratings yet

- 22CB34 DD CO Module 5 Notes (PART2)Document15 pages22CB34 DD CO Module 5 Notes (PART2)Dattatreya mankameNo ratings yet

- Sequential Circuits: Presented By: Group 3Document30 pagesSequential Circuits: Presented By: Group 3Jalaj SrivastavaNo ratings yet

- LDICA Unit 5 PDFDocument80 pagesLDICA Unit 5 PDFbhanumanuNo ratings yet

- Flip-Flops: Lecturer Uzma Hasan, CSE Department, MISTDocument21 pagesFlip-Flops: Lecturer Uzma Hasan, CSE Department, MISTRafinNo ratings yet

- D Flip-FlopDocument35 pagesD Flip-FlopSwati Kasht100% (1)

- Ade Unit 5Document41 pagesAde Unit 5KUMAR SNo ratings yet

- Flipflops and WaveformsDocument22 pagesFlipflops and WaveformsmadhuriNo ratings yet

- Test 1Document6 pagesTest 1kavana a ganigaNo ratings yet

- unit 5 ANALOG-AND-DIGITAL-INTEGRATED-CIRCUIT PPTDocument64 pagesunit 5 ANALOG-AND-DIGITAL-INTEGRATED-CIRCUIT PPTdaitdesignerclubNo ratings yet

- D and J-K Flip-FlopsDocument9 pagesD and J-K Flip-FlopsMohamed KamilNo ratings yet

- L2 FlipflopsDocument39 pagesL2 FlipflopsKogul ShiyamNo ratings yet

- Topic 4Document55 pagesTopic 4tanay.s1No ratings yet

- Flip FlopsDocument14 pagesFlip FlopsAnurag ThotaNo ratings yet

- Sequential Circuit Analysis Review: Flip-Flop VariationsDocument5 pagesSequential Circuit Analysis Review: Flip-Flop VariationsAlfi Muhammad Akbar BariaNo ratings yet

- Flip FlopDocument6 pagesFlip FlopMuzakki SathorNo ratings yet

- CH5 - Synchronous Sequenctial CircuitDocument73 pagesCH5 - Synchronous Sequenctial CircuitRobert slashNo ratings yet

- Unit 5 DLDDocument189 pagesUnit 5 DLDGuru VelmathiNo ratings yet

- 4 - Bit Shift RegisterDocument32 pages4 - Bit Shift RegisterPooja PantNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Amplitude and Frequency ModulationDocument116 pagesAmplitude and Frequency ModulationPatrick Joshua GlimadaNo ratings yet

- PTU B Tech Computer Science Syllabus 3rd - 8th SemesterDocument57 pagesPTU B Tech Computer Science Syllabus 3rd - 8th SemesterRipudaman SodhiNo ratings yet

- ResumeDocument1 pageResumeNavraj Singh ChhinaNo ratings yet

- Guide in Mounting Components EPASDocument10 pagesGuide in Mounting Components EPASGinnethon CerveraNo ratings yet

- Surviving The SOC Revolution: A Guide To Platform-Based DesignDocument9 pagesSurviving The SOC Revolution: A Guide To Platform-Based DesignRamesh YrNo ratings yet

- ER1000 Remote Terminal Unit: ApplicationDocument8 pagesER1000 Remote Terminal Unit: Application1981todurkarNo ratings yet

- Week11-Lab-build A Network With Switch and Router With Packet TracerDocument22 pagesWeek11-Lab-build A Network With Switch and Router With Packet TracerAdnan AliNo ratings yet

- Weather Station Design Using IoT Platform BasedDocument4 pagesWeather Station Design Using IoT Platform Basedadib sallehNo ratings yet

- Technology Public ProcurementDocument1 pageTechnology Public ProcurementCarloNo ratings yet

- AIX 5.3 MigrationDocument4 pagesAIX 5.3 MigrationvenkatNo ratings yet

- Various Types of Diodes With Their Characteristics & UsesDocument7 pagesVarious Types of Diodes With Their Characteristics & UsesRutvik100% (1)

- Bit SwappingDocument4 pagesBit SwappingwoodksdNo ratings yet

- Light Signal Though Optical FiberDocument5 pagesLight Signal Though Optical FiberSaysay PogiNo ratings yet

- Answer: DDocument478 pagesAnswer: DDragan KneževićNo ratings yet

- Ibm Websphere Message Broker Application Development: Covers WMB v7Document8 pagesIbm Websphere Message Broker Application Development: Covers WMB v7ashwingawliNo ratings yet

- Solid PrincipalDocument66 pagesSolid Principalkris2tmgNo ratings yet

- Building OpenCV On Ubuntu Hardfloat Rootfs For i.MX6QDocument5 pagesBuilding OpenCV On Ubuntu Hardfloat Rootfs For i.MX6QvinodNo ratings yet

- ICSE COMPUTER APPLICATIONS CLASS 10 Important QuestionsDocument24 pagesICSE COMPUTER APPLICATIONS CLASS 10 Important QuestionsLucifer 666100% (1)

- Electronic Communication Pcs and NetworkingDocument12 pagesElectronic Communication Pcs and NetworkingMirza Naseer AbbasNo ratings yet

- OpenPiton System Block ManualDocument26 pagesOpenPiton System Block ManualnhungdieubatchotNo ratings yet

- Chapter 1Document33 pagesChapter 1msamviNo ratings yet

- DC Motor Circuits Notes 2up PDFDocument15 pagesDC Motor Circuits Notes 2up PDFgaradesiertoNo ratings yet

- Voice Over-WifiDocument10 pagesVoice Over-Wifijelisavac17No ratings yet

- Digital OscilloscopeDocument3 pagesDigital OscilloscopeEugenia PerezNo ratings yet

- Monalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesDocument5 pagesMonalyn Señaris - 2.2.1.4 Packet Tracer - Simulating IoT DevicesMonalyn SeñarisNo ratings yet

- Domoticz: Open Source Home Automation SystemDocument35 pagesDomoticz: Open Source Home Automation SystemkutzooiNo ratings yet

- Exception HandlingDocument23 pagesException HandlingVikram JhaNo ratings yet

- MODULE 3: 8051 Programming in C: Microcontroller Notes:18EE52Document62 pagesMODULE 3: 8051 Programming in C: Microcontroller Notes:18EE52Supritha100% (1)