Professional Documents

Culture Documents

Lecture 5 Design Representation

Lecture 5 Design Representation

Uploaded by

Seseme RamadhaniOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lecture 5 Design Representation

Lecture 5 Design Representation

Uploaded by

Seseme RamadhaniCopyright:

Available Formats

ETU 08108:Introduction to

VLSI

Design Representation

Overview of lecture

What is design

Managing complexity

Abstraction

Hierarchical approach to design

What is design?

The design process involves taking an

idea and implementing it in some manner.

We can think of design as a top down

refinement of a specification.

Design is a complex process and can be a bit

of an art.

Design is a continual refinement in the

representation of something.

Implementation choices

Design constraints

Managing complexity

The design complexity of logic devices

increases almost exponentially with the

number of transistors to be integrated -

translates to an increase in design time.

How do we manage complex designs?

Using suitable design methodologies

Abstraction

Using EDA tools

Top down approach to design

Domains and levels of abstraction -

example

For example, a half adder

Hierarchical approach to design

Divide and conquer approach

Split the design into smaller more manageable chunks

Can be applied at different levels of abstraction

General Design

Process

How to put together millions of transistors

and make it work ?

Well chosen design methodologies

Well chosen architectures

Extensive use of powerful EDA tools

Strict design management

Well chosen testing methodologies

Design re-use.

Specification

A specification of what to construct is the first major step.

Compromise between what is wanted and what can be

made

Requires extensive experience to define best compromise

A detailed specification must be agreed upon with the

system people. Major changes during design will result

in significant delays.

Requirements must be considered at many levels

System, sub-system, Board, Hybrid, IC

Specifications can (must) be verified by system

simulations.

Specification is 1/4 - 1/3 of total IC project !

Bottom - up

Build gates in given technology

Build basic units using gates

Build generic modules of use

Put modules together

Hope that you arrived at some reasonable

architecture

Gate level simulation tools

Old fashioned design methodology a la discrete logic

Comment by one of the main designers of a Pentium processor

The design was made in a typical top - down, bottom - up,

inside - out design methodology

Schematic based

Symbol of module defines interface

Schematic of module defines function

Top - down: Make first symbol and then schematic

Bottom - up: Make first Schematic and then symbol

Symbol

Schematic

Basic gate

Logic module

Long and tedious

Getting it right - Simulation

Simulate the design at all levels (transistor, gate, system)

Analog simulator (SPICE) for transistor level

Digital gate level simulator for gate based design

Mixed mode simulation of mixed analog-digital design

Behavioural simulation at system/module level (Verilog, VHDL)

All functions must be simulated and verified.

Worst case data must be used to verify timing

Worst - Typical - Best case conditions must be verified

Process variations, Temperature range, Power supply voltage

Factor two variation to both sides ( speed: : 1 : 2)

Use programming approach to verify large set of functions

(not looking at waveform displays)

Low power design

Low power design gets increasingly important:

Gate count increasing > increasing power.

Clock frequency increasing > increasing power.

Packaging problems for high power devices.

Portable equipment working on battery.

Where does power go:

1: Charging and dis-charging of capacitance: Switching nodes

2: Short circuit current: Both N and P MOS conducting during transition

3: Leakage currents: MOS transistors (switch) does not turn completely off

The power density of modern ICs are

at the same level as the hot plate on

your stove and is approaching the power

density seen in a nuclear reactor !

Vdd

Gnd

P = N

switch

* f * C * V

dd

2

+ N

switch

* f * E

short

+ N *I

lea k

* V

dd

C

K*Vdd

2

Power in a CMOS Gate

V

DD

i

DD

(t)

Ground

Power Dissipation in

CMOS Logic (0.25)

%75

%5 %20

P

total

(01) = C

L

V

DD

2

+ t

sc

V

DD

I

peak

+ V

DD

I

leakage

C

L

Components of Power

Dynamic

Signal transitions

Logic activity

Glitches

Short-circuit

Static

Leakage

Decrease power

Lower Vdd:

5v > 2.5v gives a factor 4 !

New technologies use lower Vdd

because of risk of gate-oxide

break-down and hot electron effect.

Lower Vdd and duplicate

hardware

Lower number of

switching nodes

The clock signal often

consumes 50% of total power

Functional

unit

One functional unit:

frequency = 1

Vdd = 1

Functional

unit 1

Two functional units:

frequency = 1/2

Vdd = 1/2 (optimistic)

Functional

unit 2

P= 1 * 1

2

= 1

P = 2 * 1/2 * (1/2)

2

= 1/4

Clock

Unit 1

Ena

Unit 2

Ena

Unit 3

Ena

Clock gating

Design partitioning

Good partitioning in the design provides several

advantages including:

Easy handling of design requires sensible hierarchy

Several designers/locations

Easier to keep version control

Design management is easier

Better synthesis results

Synthesis tools work better if design is partitioned well

Reusability

Verification is easier to do if partitioning is correct

Verification/Synthesis/Layout all has an effect on

partitioning

Design partitioning

Locate related combinational logic in a single module

and single process if possible.

The synthesis tool has more flexibility in optimising a

design when related combinational logic is located in the

same module. This is because synthesis tools cannot

move logic across hierarchical boundaries during

compile operation.

You might also like

- Mastering Object-Oriented Analysis and Design With UMLDocument68 pagesMastering Object-Oriented Analysis and Design With UMLChi Nguyễn NgọcNo ratings yet

- Models and Analysis for Distributed SystemsFrom EverandModels and Analysis for Distributed SystemsSerge HaddadNo ratings yet

- Threads: Tevfik KoşarDocument40 pagesThreads: Tevfik KoşarIjazKhan100% (1)

- Functional Analysis Module V1.0Document21 pagesFunctional Analysis Module V1.0Wardiman AlexsandroNo ratings yet

- Twelve Systems Engineering RolesDocument9 pagesTwelve Systems Engineering RolesShakoor MalikNo ratings yet

- Modelling 2 EdDocument74 pagesModelling 2 EdShaurya Ashutosh BhatnagarNo ratings yet

- Overview of TestingDocument15 pagesOverview of TestingDK_usaNo ratings yet

- Patrik Haslum, Nir Lipovetzky, Daniele Magazzeni, Christian Muise - An Introduction To The Planning Domain Definition Language-Morgan & Claypool (2019)Document168 pagesPatrik Haslum, Nir Lipovetzky, Daniele Magazzeni, Christian Muise - An Introduction To The Planning Domain Definition Language-Morgan & Claypool (2019)fgumpNo ratings yet

- 001 - Research in Mechanical Engineering DesignDocument18 pages001 - Research in Mechanical Engineering DesignDaniel Camilo Salamank TNo ratings yet

- 45 Years With Design MethodologyDocument41 pages45 Years With Design MethodologyJoe TahirNo ratings yet

- Levels of AbstractionDocument11 pagesLevels of AbstractionFoster TadiwanasheNo ratings yet

- 1.1.1.a History of Civil Engineering and ArchitectureDocument26 pages1.1.1.a History of Civil Engineering and Architecturemimahmoud100% (1)

- Common People Issues in TestingDocument7 pagesCommon People Issues in TestingAmarnath Sah33% (3)

- Power of Focus.Document12 pagesPower of Focus.FELICIA CARAPIETNo ratings yet

- Automated Requirements Analysis Using Natural Language Processing 8Document74 pagesAutomated Requirements Analysis Using Natural Language Processing 8asssNo ratings yet

- Testing Chapter 9Document55 pagesTesting Chapter 9Malik JubranNo ratings yet

- TestableDocument3 pagesTestableSorina NegrilaNo ratings yet

- Aras Managing Context Using Digital TwinDocument9 pagesAras Managing Context Using Digital TwinRaul ReynosoNo ratings yet

- Guide To Requirements Definition and AnalysisDocument47 pagesGuide To Requirements Definition and AnalysisKanasai 89No ratings yet

- Model Based TestingDocument51 pagesModel Based TestingarjunNo ratings yet

- Faa Ada280477 Dot Faa Rd-93 5Document411 pagesFaa Ada280477 Dot Faa Rd-93 5anantiaNo ratings yet

- GOAL Oriented Requirements Engineering PDFDocument14 pagesGOAL Oriented Requirements Engineering PDFTALALQUIDERNo ratings yet

- CS 340 Fall 2010: Section 1Document11 pagesCS 340 Fall 2010: Section 1FrizbeeFanatic14100% (1)

- Design Automation 2010 Eng FinalDocument12 pagesDesign Automation 2010 Eng Finalakhilesh120No ratings yet

- INCOSE 17 Paper 134Document18 pagesINCOSE 17 Paper 134Mafer ReveloNo ratings yet

- Co-Evolution of Metamodels and Model Transformations: An operator-based, stepwise approach for the impact resolution of metamodel evolution on model transformations.From EverandCo-Evolution of Metamodels and Model Transformations: An operator-based, stepwise approach for the impact resolution of metamodel evolution on model transformations.No ratings yet

- Design Patterns For Simulations in ErlangDocument72 pagesDesign Patterns For Simulations in ErlangSkyezine Via Kit Fox0% (1)

- Engineering Design Thinking TeachingandlearningDocument18 pagesEngineering Design Thinking TeachingandlearningBruno Botelho0% (1)

- A Framework For A SEBK 63Document7 pagesA Framework For A SEBK 63Not Jessica SmithNo ratings yet

- Aerofoil Design RepresentationDocument46 pagesAerofoil Design RepresentationYadana1No ratings yet

- Viewpoint Design, Innovation, AgilityDocument7 pagesViewpoint Design, Innovation, Agilityapi-3851548No ratings yet

- DigitalThread - Collaborative Research - ReportDocument44 pagesDigitalThread - Collaborative Research - ReporterdaltekinNo ratings yet

- Digital Twin Generation Reconceptualizing Agent Systems For Behaviorcentered Cyberphysical System Developmentsensors SwitzerlandDocument24 pagesDigital Twin Generation Reconceptualizing Agent Systems For Behaviorcentered Cyberphysical System Developmentsensors SwitzerlandJoao NunesNo ratings yet

- Design AutomationDocument11 pagesDesign AutomationRitam MajumderNo ratings yet

- A Failure of Focus - KodakDocument155 pagesA Failure of Focus - KodakchangumanguNo ratings yet

- Ten Unsung Digital and Ai Ideas Shaping BusinessDocument10 pagesTen Unsung Digital and Ai Ideas Shaping BusinessjimituloveNo ratings yet

- 4b Clarify ProblemDocument2 pages4b Clarify ProblemomuhighNo ratings yet

- UntitledDocument498 pagesUntitledAzarudheen S StatisticsNo ratings yet

- Final Summary Report - Water System Seismic Resilience and Sustainability Program v5.1!9!26-14Document30 pagesFinal Summary Report - Water System Seismic Resilience and Sustainability Program v5.1!9!26-14Southern California Public RadioNo ratings yet

- Abstraction: From Wikipedia, The Free EncyclopediaDocument11 pagesAbstraction: From Wikipedia, The Free Encyclopedia1985 productionNo ratings yet

- Software Design Specification Template PDFDocument6 pagesSoftware Design Specification Template PDFjames kilonzoNo ratings yet

- EMU, Department of Arch.-ARCH312 - Architecture & Design Theories Instructors: T.ulusu Uraz, H. Pulhan ... 2018-19 FallDocument65 pagesEMU, Department of Arch.-ARCH312 - Architecture & Design Theories Instructors: T.ulusu Uraz, H. Pulhan ... 2018-19 Fallmert avlarNo ratings yet

- Problem Formulation in MRDocument18 pagesProblem Formulation in MRAnkita SainiNo ratings yet

- MSAA SystemDesignFINALDocument85 pagesMSAA SystemDesignFINALRolly ChanNo ratings yet

- SE - Week3 (Requirement Engineering)Document22 pagesSE - Week3 (Requirement Engineering)LaibakhanNo ratings yet

- Thread SchedulingDocument38 pagesThread SchedulingmatijahNo ratings yet

- SE-LEC-UOG-12 - Design Concepts and PrincipleDocument59 pagesSE-LEC-UOG-12 - Design Concepts and PrincipleshavzzNo ratings yet

- Teamcenter For Systems EngineeringDocument17 pagesTeamcenter For Systems EngineeringSenad BalicNo ratings yet

- Basic Concepts of Software QualityDocument41 pagesBasic Concepts of Software QualityBalaram PapanaNo ratings yet

- Naval Postgraduate School: Monterey, CaliforniaDocument283 pagesNaval Postgraduate School: Monterey, CaliforniaZig ZigNo ratings yet

- Embedded System Life CycleDocument15 pagesEmbedded System Life Cyclejibrangill50% (2)

- Model-Based Systems Engineering (MBSE) Challenge: Modeling & Simulation Interoperability (MSI) Team Status UpdateDocument105 pagesModel-Based Systems Engineering (MBSE) Challenge: Modeling & Simulation Interoperability (MSI) Team Status UpdateNaveen TripuraneniNo ratings yet

- Model Based System Engineering: No Institute GivenDocument5 pagesModel Based System Engineering: No Institute GivenSenthil Kumar KNo ratings yet

- An Introduction To R: W. N. Venables, D. M. Smith and The R Core TeamDocument105 pagesAn Introduction To R: W. N. Venables, D. M. Smith and The R Core TeamJuan Pablo KutianskiNo ratings yet

- DEV475 Mastering Object-Oriented Analysis and Design With UML 2.0Document2 pagesDEV475 Mastering Object-Oriented Analysis and Design With UML 2.0Sadmir Okanović100% (1)

- Modeling System Requirements With Use Cases: Mcgraw-Hill/IrwinDocument38 pagesModeling System Requirements With Use Cases: Mcgraw-Hill/IrwinsyayumiNo ratings yet

- Ipc 2581BDocument9 pagesIpc 2581BlaxenovNo ratings yet

- Language, Cognition, Meaning, SymbolDocument33 pagesLanguage, Cognition, Meaning, SymbolOrlando Fernández100% (1)

- FrankBuschmann SevenSecretsEveryArchitectShouldKnow - pdf-805789816 PDFDocument32 pagesFrankBuschmann SevenSecretsEveryArchitectShouldKnow - pdf-805789816 PDFRiddhi PatelNo ratings yet

- Conceptual View of Memory CellDocument64 pagesConceptual View of Memory CellTanisha Jauhari 21BCE3566No ratings yet

- How RAM WorksDocument3 pagesHow RAM WorksMohamed Hussain100% (2)

- Deld Mcqs 1Document25 pagesDeld Mcqs 1hertzberg 1No ratings yet

- Microprocessor and Microcontroller FundamentalsDocument24 pagesMicroprocessor and Microcontroller FundamentalsSrijita DasNo ratings yet

- Flancter App NoteDocument11 pagesFlancter App NotebigdogguruNo ratings yet

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015Document2 pagesEce5015 Digital-Ic-Design Eth 1.0 40 Ece5015Sivanantham SadhasivamNo ratings yet

- Lecture 6 - RTL SynthesisDocument72 pagesLecture 6 - RTL SynthesisantoniocljNo ratings yet

- Low Power Logic StyleDocument12 pagesLow Power Logic Stylergangadhar049236No ratings yet

- Assignment 3 MCDocument1 pageAssignment 3 MChardip160% (5)

- Winbond W9425G6JH-5 Datasheet PDFDocument52 pagesWinbond W9425G6JH-5 Datasheet PDFworldoasisNo ratings yet

- Switching Theory and Logic Design (CSE-203) (Makeup)Document2 pagesSwitching Theory and Logic Design (CSE-203) (Makeup)Random ShitNo ratings yet

- Lec 3Document28 pagesLec 3Talha KhanNo ratings yet

- Logic Gates RevisionDocument13 pagesLogic Gates RevisionbanaliaNo ratings yet

- Program Instruction Memory Central Processing Unit BootupDocument4 pagesProgram Instruction Memory Central Processing Unit BootupADSR100% (1)

- Synopsys Tutorial v11 PDFDocument64 pagesSynopsys Tutorial v11 PDFJinu M GeorgeNo ratings yet

- Random Access MemoryDocument18 pagesRandom Access MemoryFRANCESCO222No ratings yet

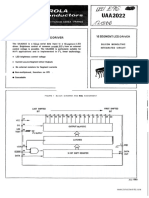

- Datasheet UAA2022 PARA CONTROLAR LEDSDocument6 pagesDatasheet UAA2022 PARA CONTROLAR LEDSRonald FrenzelNo ratings yet

- Ch5 - Basic Computer Organization and DesignDocument44 pagesCh5 - Basic Computer Organization and DesignGagan ChandelNo ratings yet

- Buses: Synchronous BusDocument4 pagesBuses: Synchronous BusIndu BalakrishnanNo ratings yet

- VLSI TrendsDocument18 pagesVLSI TrendsShibendu BhowmickNo ratings yet

- LPC2148 MCU User ManualDocument354 pagesLPC2148 MCU User ManualzelalembirhanuNo ratings yet

- 16/32 BIT Microcontroller: TLCS-900Document68 pages16/32 BIT Microcontroller: TLCS-900Cesar SaucedoNo ratings yet

- Answer: Q1Document46 pagesAnswer: Q1amar2k904100% (3)

- Electronic System Reliability Engineering PPT-c09Document15 pagesElectronic System Reliability Engineering PPT-c09krishNo ratings yet

- S.V.University, Tirupati: Semester: IiDocument13 pagesS.V.University, Tirupati: Semester: IiMallikaNo ratings yet

- Critical Reading Books VLSI DesignDocument5 pagesCritical Reading Books VLSI DesignVishnu NjNo ratings yet

- Jntu Vlsi Systems DesignDocument5 pagesJntu Vlsi Systems Design9010469071No ratings yet

- ULN2804Document5 pagesULN2804vka_princeNo ratings yet

- Introduction To ARM Cortex-M ProcessorDocument19 pagesIntroduction To ARM Cortex-M ProcessorJay PatelNo ratings yet

- Power Transistor 2SC2625Document4 pagesPower Transistor 2SC2625Jaydi ZambranoNo ratings yet