Professional Documents

Culture Documents

An Introduction To Microprocessor Architecture Using 8085 As A Classic Processor

An Introduction To Microprocessor Architecture Using 8085 As A Classic Processor

Uploaded by

Arnold JohnOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

An Introduction To Microprocessor Architecture Using 8085 As A Classic Processor

An Introduction To Microprocessor Architecture Using 8085 As A Classic Processor

Uploaded by

Arnold JohnCopyright:

Available Formats

An Introduction to Microprocessor

Architecture

using intel 8085 as a classic processor

Intel 8085

3

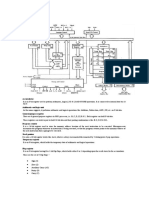

Intel 8085 Pin

Configuration

4

Signals and I/O Pins

The 8085 and Its Buses

The 8085 is an 8-bit general purpose microprocessor that can address 64K

Byte of memory.

It has 40 pins and uses +5V for power. It can run at a maximum frequency of

3 MHz.

The pins on the chip can be grouped into 6 groups:

Address Bus.

Data Bus.

Control and Status Signals.

Power supply and frequency.

Interrupt and Externally Initiated Signals.

Serial I/O ports.

The Address and Data Bus Systems

The address bus has 8 signal lines A8 A15 which are unidirectional.

The other 8 address bits are multiplexed (time shared) with the 8 data bits.

So, the bits AD0 AD7 are bi-directional and serve as A0 A7 and

D0 D7 at the same time.

During the execution of the instruction, these lines carry the

address bits during the early part, then during the late parts of

the execution, they carry the 8 data bits.

In order to separate the address from the data, we can use a latch to

save the value before the function of the bits changes.

ALE used to demultiplex address/data bus

7

The Control and Status Signals

There are 4 main control and status signals. These are:

ALE: Address Latch Enable. This signal is a pulse that become 1

when the AD0 AD7 lines have an address on them. It

becomes 0 after that. This signal can be used to enable a latch to

save the address bits from the AD lines.

RD: Read. Active low.

WR: Write. Active low.

IO/M: This signal specifies whether the operation is a memory

operation (IO/M=0) or an I/O operation (IO/M=1).

S1 and S0 : Status signals to specify the kind of operation being

performed. Usually not used in small systems.

Power Supply and Frequency Control

Signals

+V

CC

= +5V V

SS

= GND

There are 3 important pins in the frequency control group.

X0 and X1 are the inputs from the crystal or clock generating circuit.

The frequency is internally divided by 2.

So, to run the microprocessor at 3 MHz, a clock running at 6 MHz should

be connected to the X0 and X1 pins.

CLK (OUT): An output clock pin to drive the clock of the rest of

the system.

Interrupt and Externally Initiated

Signal

Interrupt Pins These are hardware interrupts used to

initiate an interrupt service routine stored at predefined

locations of the system memory.

1. INTR- General purpose interrupt

2. INTA- Acknowledge an interrupt

3. RST 7.5, RST 6.5, RST 5.5- Restart Interrupt. They have

higher Priority than INTR interrupt.

4.TRAP- Nonmaskable interrupt and has highest priority

5. Reset In- Reset the Microprocessor. The Program

Counter inside the microprocessor is set to Zero.

6. Reset Out- Indicates CPU is being reset. Can be

used as a system reset.

7. HOLD, HLDA- These pins are used when data

transfer is to be performed directly between an external

device and the main memory of the system.

8. Ready- It sets the ready signal after completing the

present job. The microprocessor enters into WAIT state

while the READY pin is disabled

Interrupt and Externally Initiated

Signal (cont.)

Serial I/O Ports

SID( Serial Input Data)

SOD(Serial Output Data)

These pins are used to interface 8085 with a serial device.

One bit information can be read or sent out serially

through these signal lines

Intel 8085 Architecture

14

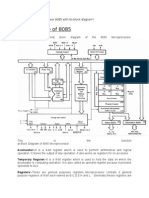

Intel 8085 CPU Block Diagram

The ALU

In addition to the arithmetic & logic circuits, the ALU

includes an accumulator, which is a part of every arithmetic

& logic operation.

Also, the ALU includes a temporary register used for holding

data temporarily during the execution of the operation. This

temporary register is not accessible by the programmer.

S Z AC P CY

D7 D6 D5 D4 D3 D2 D1 D0

The Flags register

There is also a flag register whose bits are affected by the arithmetic & logic

operations.

S-sign flag

The sign flag is set if bit D7 of the accumulator is set after an

arithmetic or logic operation.

Z-zero flag

Set if the result of the ALU operation is 0. Otherwise is reset. This

flag is affected by operations on the accumulator as well as other

registers. (DCR B).

AC-Auxiliary Carry

This flag is set when a carry is generated from bit D3 and passed to

D4 . This flag is used only internally for BCD operations.

P-Parity flag

After an ALU operation, if the result has an even # of 1s, the p-flag

is set. Otherwise it is cleared. So, the flag can be used to indicate even

parity.

CY-carry flag

This flag is set when a carry is generated from bit D7 after an unsigned

operation.

Timing and Control unit

This unit works as the brain of the CPU and

generates all the timing and control signals to

perform all the internal & external operations of

the CPU

On chip generator controlled by external crystal

Clock o/p which gives internal clock frequency

RESET i/p, RESET o/p

Timing and Control unit

Status output-S0 and S1 signifies the states of

the CPU

Three o/ps RD, WR and IO/M to control

external units

READY i/p- The CPU goes to WAIT State

until the READY becomes high.

HOLD- This signal indicates that a peripheral

such as DMA(Direct Memory Access)

Controller is requesting the use of the address

and data buses.

HLDA- This signal acknowledges the HOLD

request

Instruction Register and Decoder

IR & Instruction Decoder are part of ALU

When instruction is fetched from memory, it is

loaded into the IR

Registers

The Registers are of 8-bit & 16-bit size used for different

purposes

A- Accumulator This is an special purpose register.

All the ALU operations are performed with reference

to the contents of Accumulator.

B,C,D,E,H,L General purpose registers. These

registers can also be used for 16-bit operations in

pairs. The default pairs are BC, DE & HL.

.

PC Program Counter This is a 16-bit

register used to address the memory location

from where an instruction is going to be

executed.

SP Stack pointer - This is a 16-bit register

used to address the top of the stack memory

location.

Temporary register, W & Z These registers

are only used by 8085 and are not available for

the programmer.

Registers

The 8085 has 5 extended hardware interrupt

INTR,RST 5.5, RST 6.5, RST 7.5 and TRAP

Interrupt besides TRAP are enabled by Enable

Interrupt instruction (EI) and disabled by

Disable Interrupt instruction (DI) or by a

RESET, or by the acknowledge of an interrupt

request..

Interrupt Control

8085 has two signals used for software

controlled serial I/O

SOD(Serial Output Data)

SID (Serial Input Data)

Data is controlled through two instructions

SIM(Set Interrupt Mask) and RIM(Reset

Interrupt Mask)

Serial I/O control

You might also like

- DI-166 Service Manual v1.18Document31 pagesDI-166 Service Manual v1.18Juan Cristóbal CarvalloNo ratings yet

- If-Else Statements: BranchingDocument32 pagesIf-Else Statements: BranchingNazmul Alam DiptoNo ratings yet

- Twain ScanningDocument10 pagesTwain ScanningmbianchettoNo ratings yet

- Unit IIpptDocument70 pagesUnit IIpptAbhay ChaudharyNo ratings yet

- Microprocessor Ramesh S GaonkarDocument25 pagesMicroprocessor Ramesh S GaonkarAbraiz Khan KhattakNo ratings yet

- Chap2!4!8085 Architecture and InstructionsDocument61 pagesChap2!4!8085 Architecture and Instructionsshyam bkNo ratings yet

- Questionnaire MICROPROCESSOR PART 1 UNIT 1 and 2Document20 pagesQuestionnaire MICROPROCESSOR PART 1 UNIT 1 and 2aditya2021cs081No ratings yet

- EEE - BEE603 - Microprocessor and Microcontroller - Mr. K. DwarakeshDocument24 pagesEEE - BEE603 - Microprocessor and Microcontroller - Mr. K. Dwarakeshsatishcoimbato12No ratings yet

- Chapter 3Document35 pagesChapter 3ajayroyNo ratings yet

- UNIT I MicroprocessorDocument130 pagesUNIT I MicroprocessorAlok KumarNo ratings yet

- Unit - VI DEDocument60 pagesUnit - VI DErahulbixt23No ratings yet

- 8085 Microproceesor - PPTDocument59 pages8085 Microproceesor - PPTShanagonda Manoj KumarNo ratings yet

- Eec Practical 8085 MicroprocessorDocument8 pagesEec Practical 8085 MicroprocessorinxludezNo ratings yet

- M4 Yash AllabadiDocument6 pagesM4 Yash Allabadidegijon661No ratings yet

- Class 2-Introduction To 8085 Microprocessor PDFDocument46 pagesClass 2-Introduction To 8085 Microprocessor PDFDeepika AgrawalNo ratings yet

- MIC 04 - Case Study One 8085 MPUDocument40 pagesMIC 04 - Case Study One 8085 MPUomar hanyNo ratings yet

- Introduction To Microprocessor 8085Document23 pagesIntroduction To Microprocessor 8085GousAttarNo ratings yet

- Chapter2 MicroprocessorDocument95 pagesChapter2 MicroprocessorsagarNo ratings yet

- Introduction To 8085 MicroprocessorDocument37 pagesIntroduction To 8085 MicroprocessorAmit BeheraNo ratings yet

- Ii Microprocessor - 8085 ArchitectureDocument6 pagesIi Microprocessor - 8085 ArchitectureYohannis DanielNo ratings yet

- Architecture of 8085 MicroprocessorDocument69 pagesArchitecture of 8085 Microprocessornamrata puranikNo ratings yet

- The 8085 Microprocessor ArchitectureDocument39 pagesThe 8085 Microprocessor ArchitectureAhmed YassinNo ratings yet

- 8085 Pin Diagram and ArchitectureDocument8 pages8085 Pin Diagram and ArchitectureSneha SinghNo ratings yet

- Microprocessor NotesDocument60 pagesMicroprocessor NotesVijay KumarNo ratings yet

- Development of MicroprocessorDocument67 pagesDevelopment of MicroprocessorDanzioNo ratings yet

- Introduction To Microprocessors and 8085Document17 pagesIntroduction To Microprocessors and 8085Hoot FootNo ratings yet

- Microprocessor (Pin Digram)Document16 pagesMicroprocessor (Pin Digram)Ravi guptaNo ratings yet

- The 8085 Microprocessor ArchitectureDocument12 pagesThe 8085 Microprocessor ArchitectureBernard MunyithyaNo ratings yet

- Intel 8085 Architecture: AccumulatorDocument6 pagesIntel 8085 Architecture: AccumulatorDipesh YadavNo ratings yet

- 8085 Microprocessor - Functional Units: AccumulatorDocument5 pages8085 Microprocessor - Functional Units: AccumulatorDeep KambleNo ratings yet

- EE309 MP Mod1 Ktunotes - inDocument17 pagesEE309 MP Mod1 Ktunotes - inDivya KrishnanNo ratings yet

- Notes Unit 1Document25 pagesNotes Unit 1Ashish YadavNo ratings yet

- Microprocessor2 PDFDocument69 pagesMicroprocessor2 PDFAarush TimalsinaNo ratings yet

- 8085 OperationDocument12 pages8085 OperationMandeep SinghNo ratings yet

- 8085 Features, Signal DescriptionDocument13 pages8085 Features, Signal DescriptionRakesh Kumar DNo ratings yet

- 8085 ArchitectureDocument13 pages8085 ArchitectureShubham BokoliaNo ratings yet

- Cs2 Practical PDFDocument62 pagesCs2 Practical PDFMaitri ShahNo ratings yet

- System BusDocument20 pagesSystem BusshyamNo ratings yet

- Micrprocessor Notes 2023Document18 pagesMicrprocessor Notes 2023GautamNo ratings yet

- 8085 Microprocess or ArchitectureDocument39 pages8085 Microprocess or ArchitectureAbhi SharmaNo ratings yet

- 8085 Is Pronounced AsDocument9 pages8085 Is Pronounced AsArbaaz khan786No ratings yet

- UNIT-4: 8085 MicroprocessorDocument28 pagesUNIT-4: 8085 MicroprocessorMuthuvel MNo ratings yet

- 8085 Microprocessor Architecture, Pin DiagramDocument10 pages8085 Microprocessor Architecture, Pin DiagramSachin Jaysenan0% (1)

- Architechture of 8085: Q. Explane Micro Processor 8085 With Its Block Diagram?Document13 pagesArchitechture of 8085: Q. Explane Micro Processor 8085 With Its Block Diagram?Shubham SahuNo ratings yet

- 8085 Microprocessor - Functional Units: AccumulatorDocument3 pages8085 Microprocessor - Functional Units: AccumulatorANKIT SHARMANo ratings yet

- Unit 1 Lect 2Document17 pagesUnit 1 Lect 2tankdhruvik800000No ratings yet

- 8085 Instruction Addressing Modes ImppDocument87 pages8085 Instruction Addressing Modes ImppRohan VaidyaNo ratings yet

- Microprocess ArchitectureDocument24 pagesMicroprocess ArchitectureNew worldNo ratings yet

- CHAPTER 5: Introduction To Intel 8085 Microprocessor HardwareDocument35 pagesCHAPTER 5: Introduction To Intel 8085 Microprocessor HardwareRakesh Kumar DNo ratings yet

- 8085 1Document17 pages8085 1Amar GhogaleNo ratings yet

- 8085microproceesor ArchitectureDocument60 pages8085microproceesor ArchitecturePooja Anand JhaNo ratings yet

- 3-Ee8551-Microprocessors and MicrocontrollersDocument109 pages3-Ee8551-Microprocessors and MicrocontrollersKeerthana SahadevanNo ratings yet

- Microprocessor - 8085 ArchitectureDocument4 pagesMicroprocessor - 8085 ArchitectureLithika RameshNo ratings yet

- Unit-1 (1) Draw and Explain The Internal Architecture of 8085Document11 pagesUnit-1 (1) Draw and Explain The Internal Architecture of 8085Mann MehtaNo ratings yet

- MPDocument34 pagesMPAbhinandan JainNo ratings yet

- 03 The Architecture of The 8085Document28 pages03 The Architecture of The 8085Sheena Ann StonehillNo ratings yet

- 8085 MicroprocessorDocument25 pages8085 Microprocessorprofessor2062No ratings yet

- 8085 ArchitectureDocument40 pages8085 ArchitectureKarthi KNo ratings yet

- The 8085 Microprocessor ArchitectureDocument30 pagesThe 8085 Microprocessor ArchitectureSurbhit SinhaNo ratings yet

- An Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorDocument17 pagesAn Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorChiragNo ratings yet

- Unit - 2Document91 pagesUnit - 2s.rezina96No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Mcafee Enterprise Security Manager 11.5.x Installation Guide 11-12-2021Document52 pagesMcafee Enterprise Security Manager 11.5.x Installation Guide 11-12-2021Valentin Stefan TalpeanuNo ratings yet

- Concept Map of Basic Computer PeriodDocument2 pagesConcept Map of Basic Computer PeriodJhona A. BenosaNo ratings yet

- Procedure For Realdisp5Document10 pagesProcedure For Realdisp5ridhwan wahyudiNo ratings yet

- Multi-User PTW LibraryDocument3 pagesMulti-User PTW LibraryicaroNo ratings yet

- Intel Q35/Q33, G35/G33/G31, P35/P31 Express Chipset Memory Technology and Configuration GuideDocument13 pagesIntel Q35/Q33, G35/G33/G31, P35/P31 Express Chipset Memory Technology and Configuration GuidedejanNo ratings yet

- (SYBEX) Computer - Repair - CompTIA A+Document893 pages(SYBEX) Computer - Repair - CompTIA A+Won Chang100% (1)

- Auto Intensity Control of Street LightsDocument7 pagesAuto Intensity Control of Street LightsKoushik MaityNo ratings yet

- Comdasys SBCDocument2 pagesComdasys SBCbudituxNo ratings yet

- Au Zdictionary en USDocument182 pagesAu Zdictionary en USGuivo NamorNo ratings yet

- E50 E60instructions 11.1Document3 pagesE50 E60instructions 11.1Mara DorinNo ratings yet

- Coding StandardDocument74 pagesCoding Standardmanikanta mutyalaNo ratings yet

- NSA: Security Highlights of Windows 7Document2 pagesNSA: Security Highlights of Windows 7Brad BeckettNo ratings yet

- Using NessusDocument6 pagesUsing NessusJayal YadavNo ratings yet

- Zerto Virtual Replication InstallationDocument51 pagesZerto Virtual Replication InstallationmathewkylescribdNo ratings yet

- Actional 8.2.1 Release NotesDocument14 pagesActional 8.2.1 Release NotesMarcio ConceicaoNo ratings yet

- Installation Guide of Arduino IdeDocument8 pagesInstallation Guide of Arduino IdeSaurav kumarNo ratings yet

- Cloud Computing: Assignment-1Document14 pagesCloud Computing: Assignment-1Ravi Teja CherukuriNo ratings yet

- Modbus ProtocolDocument8 pagesModbus ProtocolvaibhavNo ratings yet

- HP 15-Da0xxx Series Compal LA-G07BP EPK50 r0.3Document44 pagesHP 15-Da0xxx Series Compal LA-G07BP EPK50 r0.3Henry Tuscano PerezNo ratings yet

- QT Installation For Visual Studio: RE RequisitesDocument13 pagesQT Installation For Visual Studio: RE RequisitesRudoLaip Thh PakpahanNo ratings yet

- Q.gate IP v23 en Web A4Document3 pagesQ.gate IP v23 en Web A4goofflineNo ratings yet

- Xvme-230 Manual February, 1985 Chapter 1 IntroductionDocument168 pagesXvme-230 Manual February, 1985 Chapter 1 IntroductionKevin BudzynskiNo ratings yet

- How To Install Windows 10Document4 pagesHow To Install Windows 10RItu CHOWDHURYNo ratings yet

- CHFI Tool Notes by Ken Underhill: Recover My Files (Windows)Document4 pagesCHFI Tool Notes by Ken Underhill: Recover My Files (Windows)FerryNo ratings yet

- Debug 1214Document3 pagesDebug 1214Hirmaa HirmaaNo ratings yet

- Dc-Da2000 - SM 2-2Document8 pagesDc-Da2000 - SM 2-2Poon Electronic Training CentreNo ratings yet